篇一 :加法器 数电实验报告三

实验三 加法器

一、 实验目的

1、掌握用SSI器件实现全加器的方法。

2、掌握用MSI组合逻辑器件实现全加器的方法。

3、掌握集成加法器的应用。

二、 实验设备及器件

1、数字逻辑电路实验板1块

2、74HC(LS)00(四二输入与非门) 1片

3、74HC(LS)86(四二输入异或门) 1片

4、74HC(LS)153(双四选一数据选择器) 1片

5、74HC(LS)283(4位二进制全加器) 1片

三、 实验原理

组合逻辑电路是数字电路中最常见的逻辑电路之一。组合逻辑电路的特点,就是在任意时刻电路的输出仅取决于该时刻的输入信号,而与信号作用前电路所处的状态无关。本实验是根据给定的逻辑功能,设计出实现这些功能的组合逻辑电路。

不考虑低位进位,只本位相加,称半加。实现半加的电路,为半加器。考虑低位进位的加法称为全加。实现全加的电路,为全加器。实现三个输入变量(一位二进制数)全加运算功能的电路称为1位全加器。实现多位二进制数相加有串行多位加法和并行多位加法两种形式,其中比较简单的一种电路是采用多个1位全加器并行相加,逐位进位的方式。

实验用器件管脚介绍:

1、74HC(LS)00(四二输入与非门)管脚如下图所示。

…… …… 余下全文

篇三 :四位加法器实验报告

四位加法器实验报告

1.实验目的:

掌握组合逻辑电路的基本分析与设计方法;

理解半加器和全加器的工作原理并掌握利用全加器构成不同字长加法器的各种方法;

学习元件例化的方式进行硬件电路设计;

学会利用软件仿真实现对数字电路的逻辑功能进行验证和分析。

2.实验仪器:

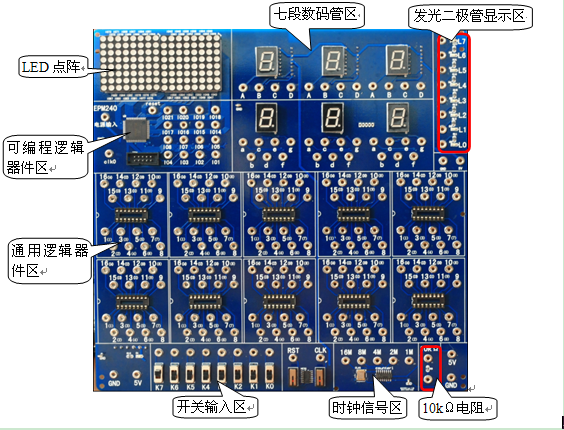

数字逻辑实验箱

3.实验内容:

A. 设计实现逐次进位加法器,进行软件仿真并在实验平台上测试。

B. 设计实现超前进位加法器,进行软件仿真并在实验平台上测试。

C.使用VHDL自带加法运算实现一个4位全加器。

4.实验代码:

A. 逐次进位加法器:

library ieee;

use ieee.std_logic_1164.all;

…… …… 余下全文

篇四 :加法器的基本原理实验报告

一、实验目的

1、了解加法器的基本原理。掌握组合逻辑电路在Quartus Ⅱ中的图形输入方法及文本输入方法。

2、学习和掌握半加器、全加器的工作和设计原理

3、熟悉EDA工具Quartus II和Modelsim的使用,能够熟练运用Vrilog HDL语言在Quartus II下进行工程开发、调试和仿真。

4、掌握半加器设计方法

5、掌握全加器的工作原理和使用方法

二、实验内容

1、建立一个Project。

2、图形输入设计:要求用VHDL结构描述的方法设计一个半加器

3、进行编译,修改错误。

4、建立一个波形文件。(根据真值表)

5、对该VHDL程序进行功能仿真和时序仿真Simulation

三、实验步骤

…… …… 余下全文

篇五 :加法器设计实验报告全

重 庆 XXXX

实 验 报 告

课 程 名 称: 电 子 电 路 基 础 实 验

实 验 名 称: 加 法 器 设 计

实 验 类 型:设 计 学 时: 3 学 时

系 别:物理与电子工程学院 专 业:电子信息工程

年 级 班 别:09级电信2班 学 期:20##—2011上

学 生 姓 名:xxx 学 号:20090701xxx

…… …… 余下全文

篇六 :数字电路加法器实验报告

中山大学移动信息工程学院本科生实验报告

(2014学年秋季学期)

课程名称:数字电路实验 任课教师:王军 助教:李正

一、 实验题目

Lab9:用3种不同的方法实现4位加法器

1. 行为级描述的加法器

2. 行波进位加法器

3. 超前进位加法器

二、实验目的

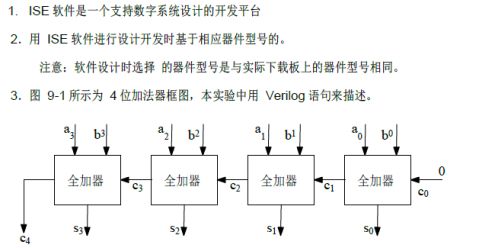

1.更加熟练的运用ISE软件进行实验设计和仿真。

2.加深对verilog语言的理解和运用

3.掌握加法器的原理,学会用不同层级实现方法来实现加法器

三、实验内容

1. 实验步骤

?编写文本文件并编译

?软件仿真

?进行硬件配置

2. 实验原理

四、 实验结果

1.Lab9: ISE软件进行4位加法器的设计与实现(行为级描述的加法器)

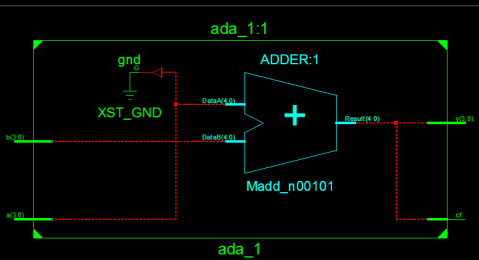

1.1. 综合得出的RTL电路图

- 1 -

图一:加法器行为级描述RTL图

如图一所示,用行为级语言对加法器进行描述即可实现四位加法器。

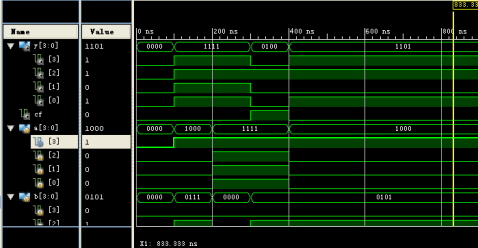

1.2 仿真波形图

图二:图一:行为级加法器实现的仿真图

如图二所示,当输入a,b二进制的四位数时,输出y分别是将四位数相加。cf是最大进位,当a与b相加之后的数大于16,则cf输出为1,其余情况输出为0。例如,当输入为a=1000,b=0111,时,输出相应的y应为1111,cf为0。根据加法运算,上述仿真的结果是正确的。

…… …… 余下全文