篇一 :数字电子线路实验报告_译码器及其应用

数电实验报告

实验三 译码器及其应用

一、实验目的

1、掌握译码器的测试方法。

2、了解中规模集成译码器的功能,管脚分布,掌握其逻辑功能。

3、掌握用译码器构成组合电路的方法。

4、学习译码器的扩展。

二、实验仪器

1、数字逻辑电路实验板 1块

2、74HC138 3-8线译码器 2片

3、74HC20 双4输入与非门 1片

三、实验原理

1、中规模集成译码器74HC138

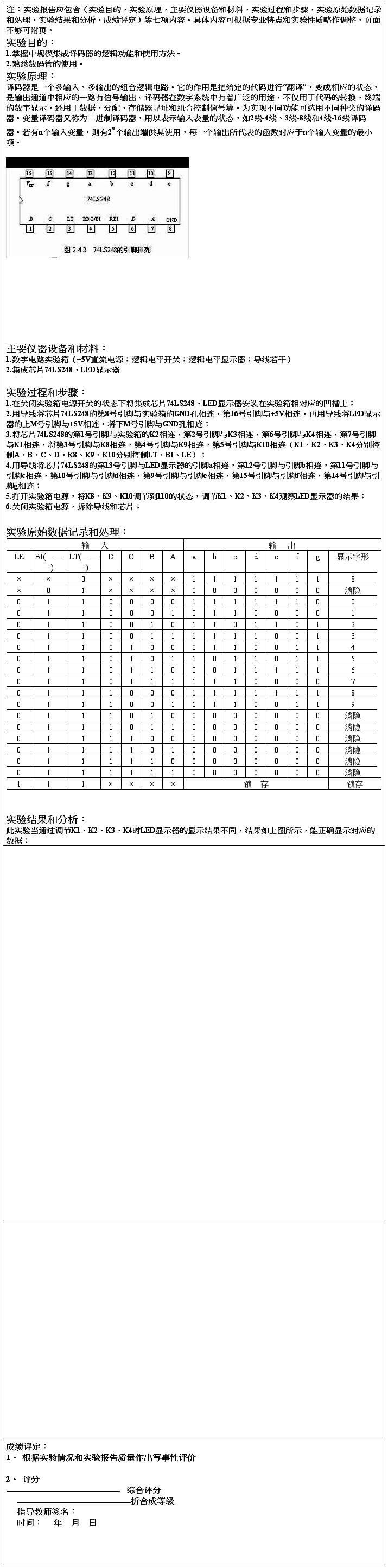

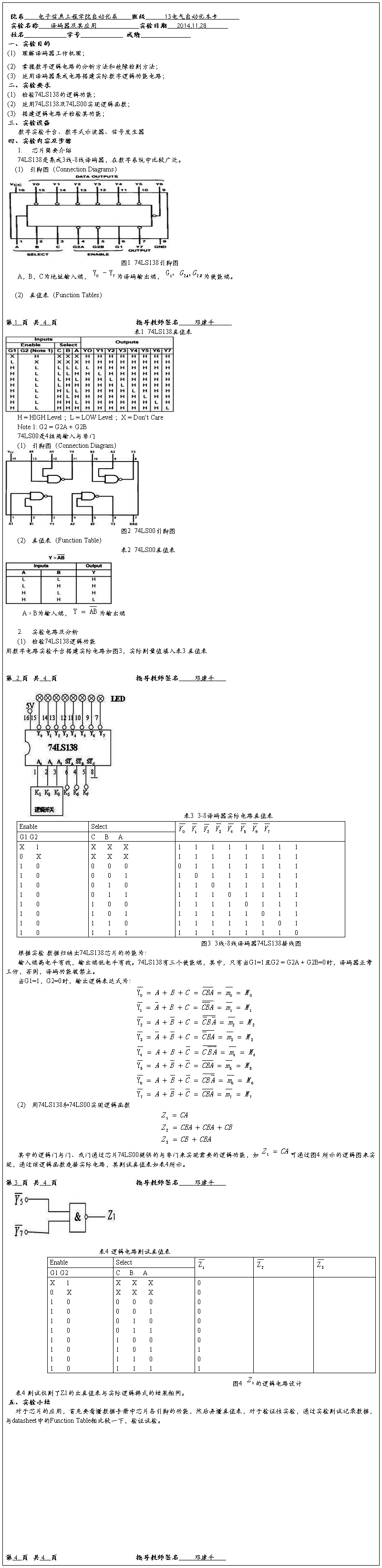

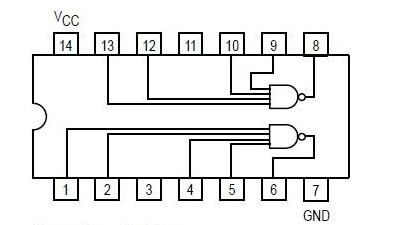

74HC138是集成3线-8线译码器,在数字系统中应用比较广泛。图3-1是其引脚排列。

其中 A2 、A1 、A0

为地址输入端, 0Y~ 7Y为译码输出端,S1、2S、3S为使能端。74HC138真值表如下:

74HC138引脚图为:

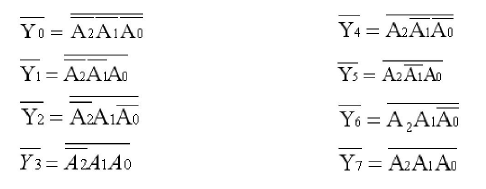

74HC138工作原理为:当S1=1,S2+S3=0时,电路完成译码功能,输出低电平有效。其中:

2、译码器应用

因为74HC138 三-八线译码器的输出包括了三变量数字信号的全部八种组合,每一个输

出端表示一个最小项,因此可以利用八条输出线组合构成三变量的任意组合电路。

四、实验内容

1、译码器74HC138 逻辑功能测试

(1)控制端功能测试

…… …… 余下全文

篇二 :译码器及其应用实验报告

实验二译码器及其使用

一. 实验目的

1. 掌握译码器的测试方法。

2. 了解中规模集成译码器的管脚分布,掌握其逻辑功能。

3. 掌握译码器构成组合电路的方法。

4. 学习译码器的扩展。

二.实验设备及器件。

1. 数字逻辑电路实验板1块。

2. 74HC(LS)20(四二输入与非门)一片。

3.74HC(LS)138(3-8译码器)二片。

三.实验原理

1.74HC(LS)138 是集成3 线-8 线译码器,在数字系统中应用比较广泛。下图是其引脚排列,

其中A2、A1、A0 为地址输入端,~为译码输出端,S 1、2、3 为使能端。下表为74HC(LS)138

…… …… 余下全文

篇三 :译码器及其应用实验报告_20xx303513_张忠钢

实验三译码器及其应用

姓名:张忠钢 班号:14011107 学号:2011303513

一、实验目的

(1)、掌握译码器的测试方法和使用方法;

(2)、了解中规模集成译码器的原理,管脚分布,掌握其逻辑功能,以及译码显示器电路的构成原理;

(3)、掌握集成译码器的扩展方法。

二、实验设备

数字电路实验箱,74LS20,74LS138。

三、实验内容

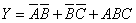

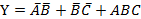

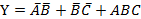

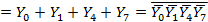

(1)利用3-8译码器74LS138和与非门74LS20实现函数:

四输入与非门74LS20的管脚图如下:

…… …… 余下全文

篇四 :实验一_用七段数码管显示简单字符--译码器及其使用 实验报告

用七段数码管显示简单字符——译码器及其应用

实验报告

专业班级:20##级计算机1班

学号:1137030 姓名:赵艺湾

实验地点: 理工楼901 实验时间:2012.9.26

实验一 用七段数码管显示简单字符——译码器及其应用

一、实验目的

1、了解显示译码器的结构和理解其工作原理。

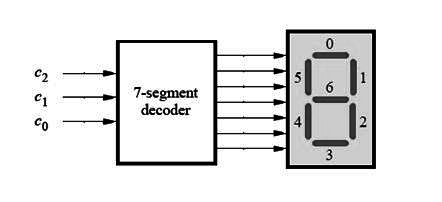

2、学习7段数码显示译码器设计。

3、学习用基逻辑门、3-8译码器、4-1选择器控制显示器的显示。

二、实验内容

1、了解逻辑门、3-8译码器、4-1选择器的工作原理,设计基本电路,实现以下功能:

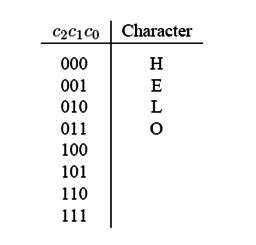

C 2C 1C 0 是译码器的3个输入,用C 2C 1C 0 的不同取值来选择在七段数码管上输出不同字符。七段数码管是共阳极的。

图1 七段译码器

C 2C 1C 0 的不同取值对应显示的字母如下:

图2 字符编码

…… …… 余下全文

篇五 :实验三---译码器及其应用实验报告

实验三 译码器及其应用

一、实验目的

(1) 掌握中规模集成译码器的逻辑功能和使用方法;

(2) 熟悉掌握集成译码器的应用;

(3) 掌握集成译码器的扩展方法。

二、实验设备

数字电路实验箱,电脑一台,74LS20,74LS138。

三、实验内容

(1)利用3-8译码器74LS138和与非门74LS20实现函数:

四输入与非门74LS20的管脚图如下:

对函数表达式进行化简:

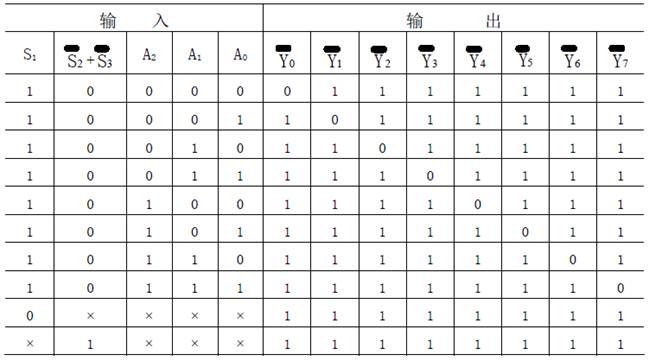

按Figure 1所示的电路连接。并用Multisim进行仿真,将结果对比。

Figure 1

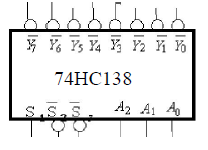

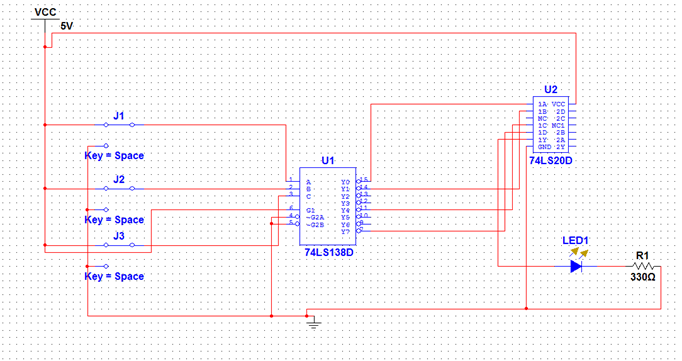

(2) 用两片74LS138组成4-16线译码器。

因为要用两片3-8实现4-16译码器,输出端子数目 刚好够用。

刚好够用。

而输入端只有  三个,故要另用使能端进行片选使两片138译码器进行分时工作。而实验台上的小灯泡不够用,故只用一个灯泡,而用连接灯泡的导线测试

三个,故要另用使能端进行片选使两片138译码器进行分时工作。而实验台上的小灯泡不够用,故只用一个灯泡,而用连接灯泡的导线测试 ,在各端子上移动即可。在multisim中仿真电路连接如Figure 2所示(实验台上的电路没有接下面的两个8灯LED):

,在各端子上移动即可。在multisim中仿真电路连接如Figure 2所示(实验台上的电路没有接下面的两个8灯LED):

Figure 2

四、实验结果

(1) 利用3-8译码器74LS138和与非门74LS20实现函数。

…… …… 余下全文

篇八 :译码器及其应用仿真实验

实验二 译码器及其应用仿真实验

一、 实验目的

1、掌握译码器的测试方法。

2、了解中规模集成译码器的管脚分布,掌握其逻辑功能。

3、掌握用译码器构成组合电路的方法。

4、学习译码器的扩展。

二、 实验设备及器件

1、multisim11.0仿真软件

2、 计算机

三、 实验原理

74HC(LS)138是集成3线-8线译码器,在数字系统中应用比较广泛。下图是其引脚排列,其中A2、A1、A0为地址输入端, ~

~ 为译码输出端,S 1、

为译码输出端,S 1、 2、

2、 3为使能端。下表为74HC(LS)138功能表。74HC(LS)138工作原理为:当S 1=1

3为使能端。下表为74HC(LS)138功能表。74HC(LS)138工作原理为:当S 1=1 2+

2+ 3=0时,电路完成译码功能,输出低电平有效。其中:

3=0时,电路完成译码功能,输出低电平有效。其中:

…… …… 余下全文

学院实验报告

学院实验报告 专业名称 软件工程

专业名称 软件工程