篇二 :时序逻辑电路测试及研究 实验报告(有数据)

实验六 时序逻辑电路测试及研究

一、实验目的

1、掌握计数器电路分析及测试方法。

2、训练独立进行实验的技能。

二、实验仪器及器件

1、双踪示波器、实验箱

2、实验用元器:74LS00 1片 74lS73 2片 74LS175 1片 74LS10 1片

三、实验内容、测试电路及测试表格

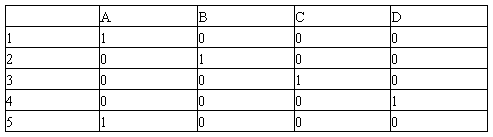

1、异步二进制计数器

(1) 按图5.1 接线。

(2) 由CP 端输入单脉冲,测试并记录

Q1—Q4 状态及波形(可调连续脉冲)。

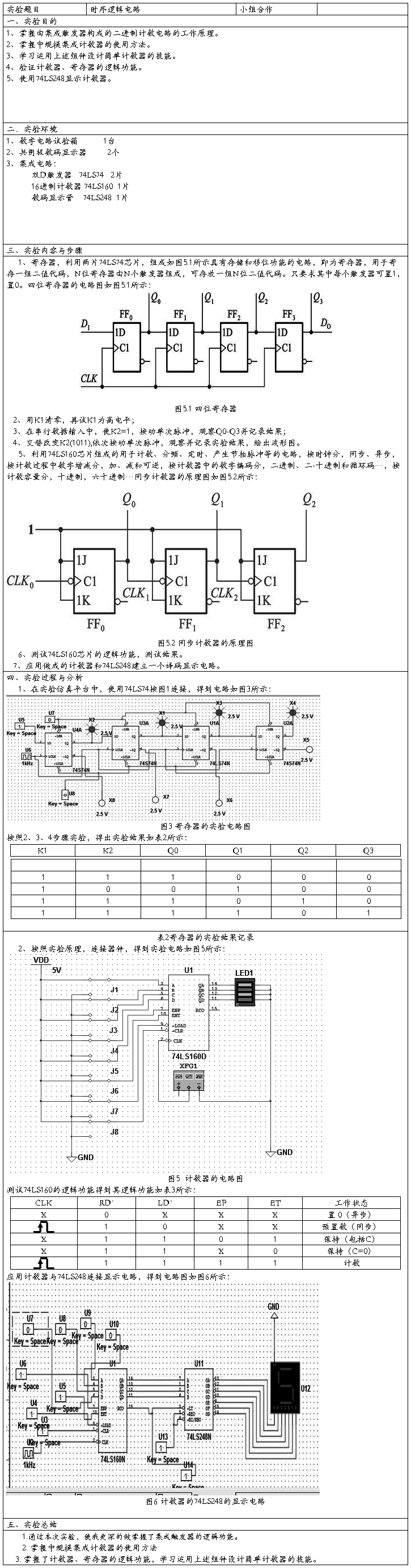

表6.1

2、异步二—十进制加法计数器

(1) 按图5.2 接线。QA、QB、QC、QD 4 个输出端分别接发光二极管显示,CP 端接连续脉冲或

单脉冲。

(2) 在CP 端接连续脉冲,观察CP、QA、QB、QC、QD 的波形。

(3) 画出CP、QA、QB、QC、QD 的波形。

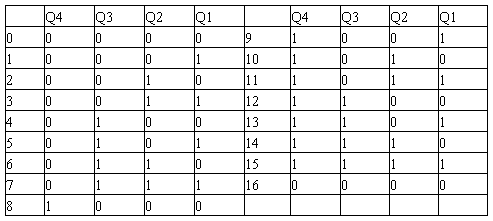

表6.2

3、移位寄存器型计数器

(1) 按图5.3 接线构成环形计数器,将A、B、C、D 置为1000,用单脉冲计数,记录各触发器状态。

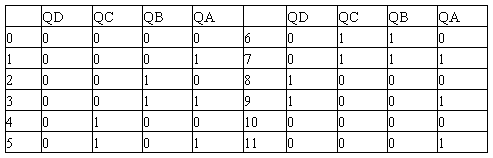

表6.3

(2) 改为连续脉冲计数,并将其中一个状态为“0”的触发器置为“1”(模拟干扰信号作用的结果),观察计数器能否正常工作。分析原因。

…… …… 余下全文

篇三 :触发器-时序逻辑电路实验报告

实验报告

实验报告

课程名称:数字电子技术基础实验 指导老师:樊伟敏 成绩:__________________

实验名称:触发器应用实验 实验类型:设计类 同组学生姓名:__________

一、实验目的和要求(必填) 二、实验内容和原理(必填)

…… …… 余下全文

篇四 :时序逻辑电路实验报告

二、时序逻辑电路实验题目

1. 试用同步加法计数器74LS161(或74LS160)和二4输入与非门74LS20构成百以内任意进制计数器,并采用LED数码管显示计数进制。采用555定时器构成多谐振荡电路,为同步加法计数器提供时钟输入信号。例如,采用同步加法计数器74LS 161构成60进制加法计数器的参考电路如图2所示。

设计:

(一)设计一个固定进制的加法计数器。

(1)利用555定时器设计一个可以生时钟脉冲的多谐振荡器,使其构成长生脉冲,对同步加法器74LS161输入信号,根据555定时器构成的多谐振荡器的周期可定,由图可的T=T1+T2=0.7(RA+RB)C+0.7 RBC=0.7(RA+2RB)C,通过改变电阻RA,RB和C的大小,可以改变脉冲的周期。所发电阻为2个510kΩ,C=1uF,则T=0.7(RA+2RB)C=0.7x510x3x0.1/1000s=1.071s.

(2)利用十六进制的加法计数器74LS61组成百以内任意进制计数器,可以用清零法和置数法改变计数器的技术进制,由于译码显示器可以显示0.1.2.3….9,所以一片74LS161只可以控制一个显示器,就要将一片74LS161改为十进制,最后再利用级联的74LS161改变数组进制,可以将不同进制的数值用显示姨妈其显示出来,下面以33进制为例进行设计,

…… …… 余下全文

篇五 :时序逻辑电路实验报告

数字电子技术实验报告

实验名称:时序逻辑电路

班级 姓名 学号

实验日期 年月日 交报告日期年月日

时序逻辑电路

一、设计要求

1.设计一个秒脉冲发生器,用LED指示秒脉冲的发送。

2.设计一个带有异步清零和同步置数信号的4位寄存器,并在开发板上验证。

二、实验内容

任务1:秒脉冲发生器

(1)源文件——ge.v

module ge(

input clr,

input clk,

output LED

);

parameter T1s = 26'b10_1111_1010_1111_0000_1000_0000;

…… …… 余下全文

篇六 :数电实验报告-时序逻辑电路

实验报告

课程名称:数字电子技术基础实验

指导老师:**

成绩:

实验名称:时序逻辑电路实验 实验类型:设计类 同组学生姓名:

一、实验目的和要求(必填)

二、实验内容和原理(必填)

三、主要仪器设备(必填)

四、操作方法和实验步骤

五、实验数据记录和处理

六、实验结果与分析(必填)

七、讨论、心得

一、实验目的和要求

1. 加深理解时序电路的工作原理。

2. 掌握同步时序逻辑电路的设计与调试方法。

3. 了解集成时序逻辑电路的应用。

4. 提高分析实验中出现的问题的能力,学习自启动电路的设计方法。

二、主要仪器与设备

实验选用集成电路芯片:74LS00(与非门)、74LS55(与或非门)、74LS74(双D

触发器)、74LS107(双J—K 触发器),74LS161中规模集成计数器,GOS-6051 型示波器,导线,SDZ-2 实验箱。

三、实验内容和原理、数据记录

1. 用74LS107型J-K触发器和74LS11三输入与非门设计一个8421BCD码的同步十进制加法计数器并进行实验。

…… …… 余下全文

篇七 :数电实验报告 典型时序逻辑电路分析与设计实验

《数字电子技术》课程实验报告

实验四:典型时序逻辑电路分析与设计实验

1、实验目的

1、掌握中规模数字集成电路同步计数器的基本工作原理和使用方法。

2、理解中规模数字集成电路同步计数器的基本工作特性。

3、掌握用中规模数字集成电路同步计数器实现任意进制计数器的基本方法。

4、了解同步计数器基本调试方法。

2、实验任务

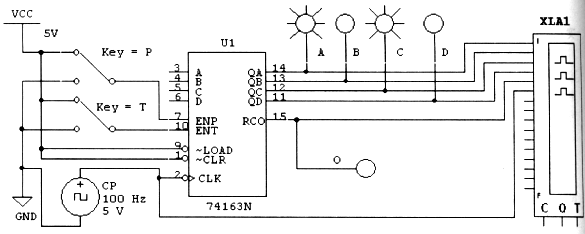

1、4位二进制加法计数器74LS163功能分析(参考实验教材P356)

(1)参考图6.7.1,在实验板创建4位二进制加法计数器74LS163功能分析电路:① 计数;② 清零;③ 保持功能。

图6.7.1

(2)将检测结果记入自拟的表格中。

…… …… 余下全文

篇八 :学生实验报告模版—时序逻辑电路的设计与测试-参考答案

实验十一 时序逻辑电路的设计与测试

一、 实验目的

1. 掌握时序逻辑电路的设计原理与方法。

2. 掌握时序逻辑电路的实验测试方法。

二、 实验原理

该实验是基于JK触发器的时序逻辑电路设计,要求设计出符合一定规律的红、绿、黄三色亮灭循环显示的电路,并且在实验板上搭建实现出来。主要的设计和测试步骤如下:

(1)根据设计的循环显示要求,列出有关Q3Q2Q1状态表;

(2)根据状态表,写出各触发器的输入端J和K的状态;

(3)画出各触发器的输入端J和K关于Q3Q2Q1的卡诺图;

(4)确定各触发器的数软J和K的最简方程;

(5)根据所得的最简方程设计相应的时序逻辑电路;

(6)在实验板上,有步骤有次序的搭建实验电路,测试所设计的电路是否满足要求。

具体设计过程参见【附录二】提供的实例。

三、 预习要求

1. 查阅附录芯片CC4027B和芯片74LS00的管脚定义。

2. 阅读理论教材关于时序逻辑电路的内容,掌握实验的理论基础。

四、 实验设备与仪器

1. 数字电路实验板(箱);

2. 芯片:CC4027B;74LS00;74LS20。

…… …… 余下全文