篇一 :数字电子时钟实验报告

华大计科学院

数字逻辑课程设计说明书

题目: 多功能数字钟

专业: 计算机科学与技术

班级: 网络工程1班

***

学号: ****

完成日期: 20XX-9

一、设计题目与要求

设计题目:多功能数字钟

设计要求:

1.准确计时,以数字形式显示时、分、秒的时间。

2.小时的计时可以为“12翻1”或“23翻0”的形式。

3.可以进行时、分、秒时间的校正。

二、设计原理及其框图

1.数字钟的构成

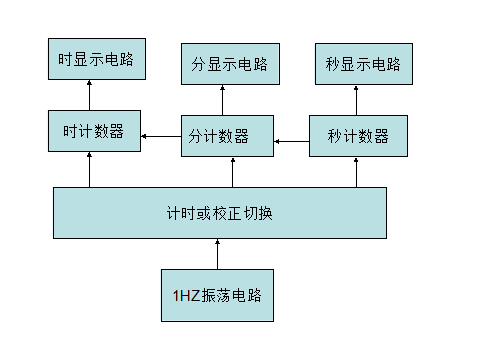

数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路。图 1 所示为数字钟的一般构成框图。

图1 数字电子时钟方案框图

⑴多谐振荡器电路

多谐振荡器电路给数字钟提供一个频率1Hz 的信号,可保证数字钟的走时准确及稳定。

⑵时间计数器电路

时间计数电路由秒个位和秒十位计数器、分个位和分十位计数器及时个位和时十位计数器电路构成。其中秒个位和秒十位计数器、分个位和分十位计数器为60 进制计数器。而根据设计要求,时个位和时十位计数器为24 进制计数器。

⑶译码驱动电路

译码驱动电路将计数器输出的8421BCD 码转换为数码管需要的逻辑状态,并且为保证数码管正常工作提供足够的工作电流。

…… …… 余下全文

篇二 :数字钟实验报告

数字钟实验报告

数字钟实验报告

课题名称:数字钟的设计与制作

组员:王庆刘盛清杨隽

姚琦邱健斌

姓名:

班级:电气信息I类112班

实验时间:

实验时间:

实验地点:

实验地点:

指导老师:

目录

一、实验目的--------------------------------------------------------------------------------------------------------------3

二、实验任务及要求-----------------------------------------------------------------------------------------------------3

三、实验设计内容--------------------------------------------------------------------------------------------------------3

…… …… 余下全文

篇三 :数字电子钟实验报告

目 录

一、设计目的、意义 …………………………………………………1

二、设计内容 …………………………………………………………1

1总体设计方案简介 ………………………………………………1

2单元电路设计 ……………………………………………………2

3总电路图 …………………………………………………………6

4仿真结果 …………………………………………………………7

三、结果分析……………………………………………………………8

四、设计总结……………………………………………………………8

五、设计心得……………………………………………………………9

参考文献 ………………………………………………………………10

附录 ……………………………………………………………………11

一、设计目的、意义

1.巩固和加深对电子线路基本知识的理解,提高综合运用课程知识的能力。

2.培养学生根据课程需要自学参考书籍,查阅手册、图表和文献资料的能力。

3.通过实际电路方案的分析比较、设计计算、元件选取、安装调试等环节,初步掌握简单实用电路的分析方法和工程设计方法。

…… …… 余下全文

篇四 :数字电路数字时钟课程实验报告

数字时钟设计实验报告

一、设计要求:

设计一个24小时制的数字时钟。

要求:计时、显示精度到秒;有校时功能。采用中小规模集成电路设计。

发挥:增加闹钟功能。

二、设计方案:

由秒时钟信号发生器、计时电路和校时电路构成电路。

秒时钟信号发生器可由振荡器和分频器构成。

计时电路中采用两个60进制计数器分别完成秒计时和分计时;24进制计数器完成时计时;采用译码器将计数器的输出译码后送七段数码管显示。

校时电路采用开关控制时、分、秒计数器的时钟信号为校时脉冲以完成校时。

三、电路框图:

图一 数字时钟电路框图

四、电路原理图:

(一)秒脉冲信号发生器

秒脉冲信号发生器是数字电子钟的核心部分,它的精度和稳定度决定了数字钟的质量。由振荡器与分频器组合产生秒脉冲信号。

Ø 振荡器: 通常用555定时器与RC构成的多谐振荡器,经过调整输出1000Hz

脉冲。

…… …… 余下全文

篇六 :数字电子钟设计实训报告

四川机电职业技术学院设计报告书

数字电子钟的设计

【摘要】

本系统由晶体振荡器、分频器、计数器、译码器、七段译码显示器和校准、报时电路组成,采用了CMOS或TTL系列(双列直插式)中小规模集成芯片。总体方案设计由主体电路和扩展电路两大部分组成。其中主体电路完成数字钟的基本功能,扩展电路完成数字钟的扩展功能,进行了各单元电路设计,总体安装、制作及调试。数字钟是一种计时装置,不仅能替代指针式钟表,还可以运用到定时控制、自动计时及时间程序控制等方面,应用广泛。

【关键词】

石英晶振、分频器、计数器、译码器、七段译码显示器、校准、整点报时。

第一章 数字电子钟总体方案

1.1 数字电子钟总体方案的确定

数字电子钟组成一般由振荡器、分频器、计数器、译码器及显示器等几部分组成。石英振荡器产生的时标信号送到分频器,分频电路将时标信号分成秒脉冲,秒脉冲送入计数器进行计数,并把累计结果以“时”、“分”、“秒”的数字显示出来。“秒”的显示由两级计数器和译码器组成的六十进制计数器电路实现,“分“的显示电路与“秒”相同。“时”的显示由两极计数器和译码器组成的二十四进制计数器电路实现。

秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,一般用石英晶体振荡器加分频器来实现。将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。“分计数器”也采用60进制计数器,每累计60分钟,发出一个“时脉冲”信号,该信号将被送到“时计数器”。“时计数器”采用24进制计时器,可实现对一天24小时的累计。译码显示电路将“时”、“分”、“秒”计数器的输出状态0进行七段显示译码器译码,通过六位七段译码显示器显示出来。整点报时电路根据计时系统的输出状态产生一脉冲信号,然后去触发一音频发生器实现报时。校时电路时用来对“时”、“分”显示数字进行校对调整的。

…… …… 余下全文

篇八 :多功能数字电子钟实验报告

一、设计题目

多功能数字电子钟

二、设计目的

1、掌握数字电路中计数、分频、译码、显示及时钟脉冲振荡器等组合逻辑电路与时序逻辑电路的综合应用。

2、掌握多功能数字钟电路设计方法、装调技术及数字钟的扩展应用。

三、设计内容及要求

1、基本要求

a)准确计时,以数字形式显示时、分、秒的时间;

b)小时以24进制,分和秒为60进制;

c)具有校时电路

2、设计数字钟的整体电路并画出电路图

3、组装、调试单元电路及整体电路

四、设计过程

1、 查阅资料,了解数字钟电路的基本原理并画出原理框图

数字钟电路系统主要由主体电路和扩展电路两大部分组成,其中主体电路完成数字钟的基本功能,扩展电路完成数字钟的扩展功能。振荡器、分频器、计时电路、译码显示电路与校时电路五大部分组成数字钟的整体电路。其中计时电路即为时间的计时,校时电路主要是在时间不准确时调节时间到准确的时间点上。系统组成原理框图如下图1.1所示。

图1.1 数字电子钟原理框图

由以上的原理图可知,本电路主要由振荡器和分频器产生1HZ(即1秒)的秒脉冲,用秒脉冲驱动计数器开始计时。因为每分钟60秒,每小时60分钟,所以应该有24进制的“时计数器”、60进制的“分计数器”、60进制的“秒计数器”。当“秒计数器”计数到59后,下一个脉冲到达时“分计数器”就进1,“分计数器”计数到59后,再来一个脉冲“时计数器”就进1。把秒计数器的输出进行译码、显示时钟秒。分计数器的输出经译码、显示时钟分。时计数器的输出经译码、显示时钟时。例如,当计时到20:59:59时,再来一个脉冲后,就会显示21:00:00。

…… …… 余下全文