篇一 :一位半加器实验报告

实验一 1位半加器

一、 实验目的

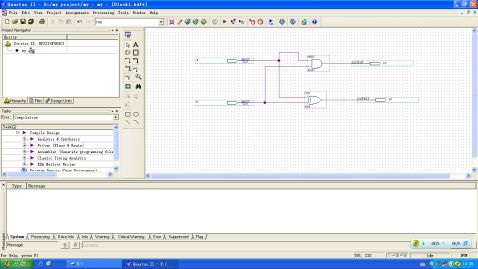

熟悉利用QuartusⅡ的原理图输入方法设计简单组合电路,并掌握其设计方法和软件的应用

二、 实验原理:

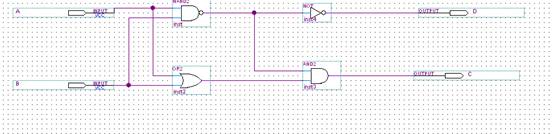

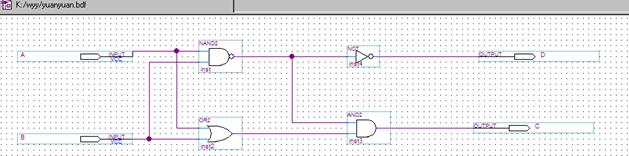

1位半加器可以由与、或、非等基本门构成,如下图所示。

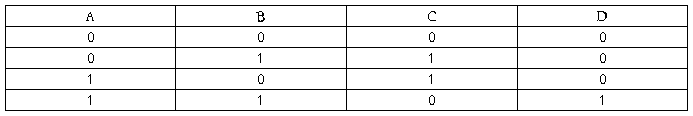

半加器的真值表中两个输入是加数A和B,输出有一个是C,另一个是D。

三、 实验内容

按半加器的原理图完成输入、编译,然后进行仿真。

四、 步骤

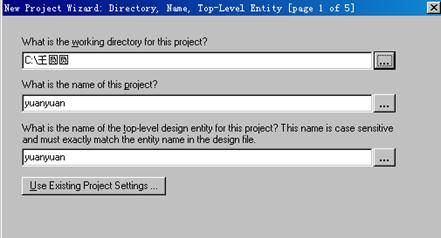

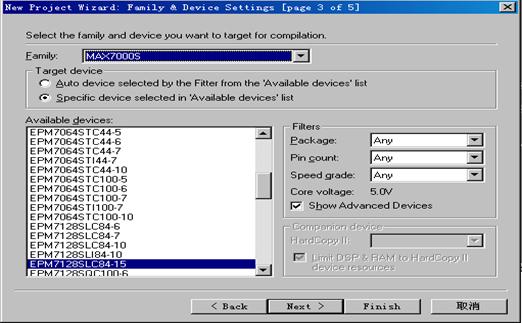

1、 项目的新建

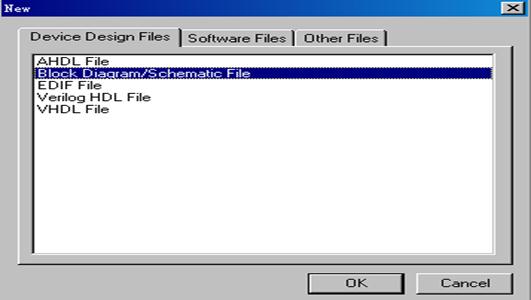

2、 半加器的原理图设计

3、 编译

4、 仿真

仿真要设置仿真结束时间,波形编辑器默认的仿真结束时间为1µS,根据仿真需要,可以自由设置仿真的结束时间。选择QUARTUSII软件的Edit>End Time命令,弹出线路束时间对话框,在Time框办输入仿真结束时间,点击OK按钮完成设置。

…… …… 余下全文

篇二 :Quartus II半加器实验报告

CPLD/FPGA设计实验报告

实验一 半加器

一、 创建工程

工程名称:adder 顶层实体文件名:adder

器件: EP1C12Q240C8 (要求:Cyclone系列任意器件)

…… …… 余下全文

篇四 :半加器和D触发器实验报告

VHDL硬件描述语言实验实验内容:

报告 1、半加器 2、D触发器

半加器

? 实验原理:

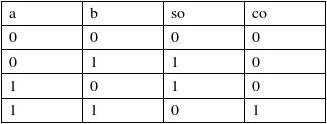

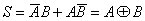

"和"与"进位"。根据半加器的

逻辑表达式可知半加器的“和”so是a、bco是a、b相与。所以半加器可以用两个与非门和一个异或门组成。 1

? 真值表:

?

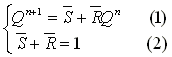

特征方程:

? 实验电路图:

? 功能仿真图:

D触发器

? 实验原理:

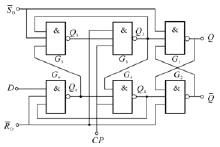

SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。当/SD=1且/RD=0时,不论输入端D为何种状态,都会使Q=0,Q非=1,即触发器置0;当/SD=0且/RD=1时,Q=1,Q非=0,触发器置1,SD和RD通常又称为直接置1和置0端。我们设它们均已加入了高电平,不影响电路的工作。工作过程如下:

1.CP=0时,G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5非=D非。

D触发器原理

2.当CP由0变1时触发器翻转。这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。Q3=Q5非=D非,Q4=Q6非=D。由基本RS触发器的逻辑功能可知,Q=Q3非=D。

…… …… 余下全文

篇五 :数电实验报告半加全加器

实验二 半加/减器与全加/减器

一、实验目的:

(1)掌握全加器和半加器的逻辑功能。

(2)熟悉集成加法器的使用方法。

(3)了解算术运算电路的结构。

二、实验设备:

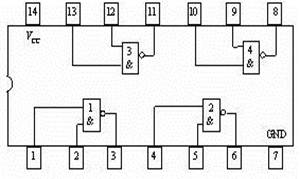

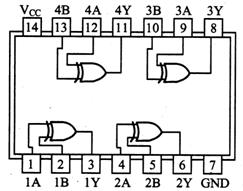

1、74LS00(二输入端四与非门)

2、74LS86(二输入端四异或门)

3、数字电路实验箱、导线若干。

(74LS00引脚图) (74LS86引脚图)

三、实验原理:

两个二进制数相加,叫做半加,实现半加操作的电路,称为半加器。A表示被加数,B表示加数,S表示半加和,Co 表示向高位的进位。

全加器能进行加数、被加数和低位来的信号相加,并给出该位的进位信号以及和。

四、实验内容:

用74LS00和74LS86实现半加器、全加器的逻辑电路功能。

(一)半加器、半减器

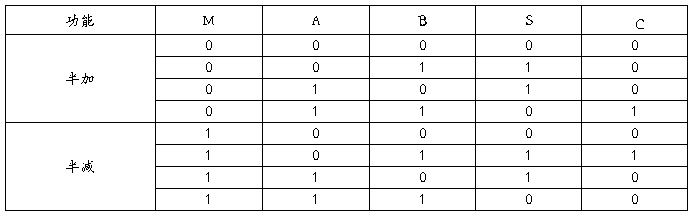

M=0时实现半加,M=1时实现半减,真值表如下:

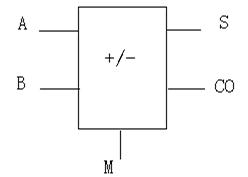

(半加器图形符号)

(半加器图形符号)

2、

(1)S真值表:

(2)C真值表:

…… …… 余下全文

篇六 :组合逻辑电路(半加器全加器及逻辑运算) 实验报告

电子通信与软件工程系2013-2014学年第2学期

《数字电路与逻辑设计实验》实验报告

---------------------------------------------------------------------------------------------------------------------

班级: 姓名: 学号: 成绩:

同组成员: 姓名: 学号: ---------------------------------------------------------------------------------------------------------------------

…… …… 余下全文

篇七 :半加器全加器的工作原理和设计方法实验报告

一、实验目的

1、学习和掌握半加器全加器的工作原理和设计方法。

2、熟悉EDA工具Quartus II的使用,能够熟练运用Vrilog HDL语言在

Quartus II下进行工程开发、调试和仿真。

3、掌握组合逻辑电路在Quartus Ⅱ中的图形输入方法及文本输入方法,

掌握层次化设计方法。

4、掌握半加器、全加器采用不同的描述方法。

二、实验内容

1、完成半加器全加器的设计,包括原理图输入,编译、综合、适配、仿真等。并将半加器电路设

置成一个硬件符号入库

2、建立更高层次的原理图设计,利用1位半加器构成1位全加器,并完成编译、综合、适配、仿真并硬件测试

3、采用图形输入法设计1位加法器分别采用图形输入和文本输入方法,设计全加器

4、实验报告:详细叙述1位全加法器的设计流程,给出各层次的原理图及其对应的仿真波形图,给出加法器的上时序分析情况,最后给出硬件测试流程和结果。

…… …… 余下全文

篇八 :半加器全加器&4位奇偶发生器设计实验报告

上海大学 计算机学院

上海大学 计算机学院

《数字逻辑实验》报告 2

姓名 王僖 学号 12125821 教师 刘学民

时间 周一(7-10)地点计算机学院大楼 704机房 机位 38

一. 分立元件构成半加器和全加器 实验

1. 实验目的

1)掌握组合逻辑电路的功能测试

2)学会二进制数的运算规则

3)掌握构造半加器和全加器的逻辑功能

2. 原理

半加器是对两个一位二进制数进行相加,产生“和”与“进位”。根据半加器逻辑表达式可知,半加器的“和”Y是A、B的异或,而“进位”Z是A、B的相与。故半加器可用一个集成异或门和两个与非门组成。

…… …… 余下全文