篇一 :通用寄存器实验报告

6.9 通用寄存器 实验报告

一、实验目的:

1、了解通用寄存器组的用途及对CPU的重要性。

2、掌握通用寄存器组的设计方法。

二、实验内容:

1、通用寄存器组的作用

通用寄存器组是CPU的重要组成部分。

(1)从存储器和外部设备(除DMA方式外)取来的数据要放在通用寄存器中;

(2)向存储器和外部设备(除DMA方式外)输出的数据从通用寄存器中取出;

(3)参加算术运算和逻辑运算的数据从通用寄存器组中取出,同时通用寄存器也是运算结果的暂存地。

(4)通用寄存器组有两个读端口,负责提供进行算术逻辑单元需要的源操作数和目的操作数;有一个写端口,负责将运算结果保存到指定的寄存器内。

2、通用寄存器组功能实现

根据通用寄存器组的功能要求,一个只有四个16位寄存器的通用寄存器组的框图如下图所示:

⑴ 寄存器部分:

当reset为低电平时,将四个16位寄存器R0-R3复位为0;当寄存器的write和sel为高电平时,在时钟信号clk的上升沿将D端的输入D[15-0]写入寄存器,然后送到寄存器的输出Q[15-0]。4个寄存器的允许写信号write和外部产生的目的寄存器写信号DRWr直接相连。每个寄存器还有另一个选择信号sel,它决定哪一个寄存器进行写操作。4个寄存器的选择信号分别和2-4译码器产生的sel00、sel01、sel10、sel11相连。只有当一个寄存器被选中(sel为高电平时),才允许对该寄存器进行写操作。

…… …… 余下全文

篇二 :寄存器实验报告

寄存器实验报告

一、实验目的

1. 了解寄存器的分类方法,掌握各种寄存器的工作原理;

2. 学习使用Verilog HDL 语言设计两种类型的寄存器。

二、实验设备

PC 微机一台,TD-EDA 实验箱一台,SOPC 开发板一块。

三、实验内容

寄存器中二进制数的位可以用两种方式移入或移出寄存器。第一种方法是以串行的方式将数据每次移动一位,这种方法称之为串行移位(Serial Shifting),线路较少,但耗费时间较多。第二种方法是以并行的方式将数据同时移动,这种方法称之为并行移位(Parallel Shifting),线路较为复杂,但是数据传送的速度较快。因此,按照数据进出移位寄存器的方式,可以将移位寄存器分为四种类型:串行输入串行输出移位寄存器(Serial In- Serial Out)、串行输入并行输出移位寄存器(Serial In- Parallel Out)、并行输入串行输出移位寄存器(Parallel In- Serial Out)、并行输入并行输出移位寄存器(Parallel In-Parallel Out)。

…… …… 余下全文

篇三 :通用寄存器组实验报告

通用寄存器组

学号:201207030 姓名:叶利钦 专业:计算121

一、 实验目的

(1) 了解通用寄存器组的用途及对CPU的重要性。

(2) 掌握通用寄存器组的设计方法。

二、 实验原理

通用寄存器组是CPU的重要组成部分。从存储器取来的数据要放在通用寄存器中;从外部设备取来的数据除DMA方式外,要放在通用寄存器中。向存储器输出的数据也是从通用寄存器中取出;向外部设备输出的数据除DMA方式外也是从通用寄存器中取出来的。由于从通用寄存器组中取数据比从存储器或者外部设备取数据快得多,因此参加算术运算和逻辑运算的数据一般是从通用寄存器组中取出,它向算术逻辑单元ALU提供了进行算术运算和逻辑运算所需要的两个操作数,同时又是运算结果的暂存地。通用寄存器组内寄存器的数目与CPU性能有关,CPU性能预告,通用寄存器组内的寄存器数目越多。由于算术逻辑运算需要两个操作数,因此通用寄存器组有两个读端口,负责提供进行算术逻辑单元需要的源操作数和目的操作数。通用寄存器组有1个写端口,负责将运算结果保存到指定的寄存器内。根据通用寄存器组的功能要求,一个只有4个16位寄存器的通用寄存器组的框图如下图所示。

…… …… 余下全文

篇四 :计算机组成原理实验报告 通用寄存器单元实验

西华大学数学与计算机学院实验报告

一、目的

1.了解通用寄存器的组成和硬件电路

2. 利用通用寄存器实现数据的置数、左移、右移等功能

二、实验原理

(1)寄存器实验构成

1、通用寄存器由2片GAL构成8位字长的寄存器单元。8芯插座RA-IN作为数据输入端,可通过端8芯扁平电缆,把数据数据输入端连接到数据总线上。

2、数据输出由一片74LS244(输出缓冲器)来控制。用8芯插座RA-OUT作为数据输出端,可通过端8芯扁平电缆,把数据数据输出端连接到数据总线上。

3、判零和进位电路由1片GAL、1片7474和一些常规芯片组成,用2个LED(ZD、CY)发光管分别显示其状态。

(2)通用寄存器单元的工作原理

通用寄存器的核心部件为2片GAL,它具有锁存、左移、右移、保存等功能。各个功能都由X1、X2信号和工作脉冲RACK来决定。当置ERA=0、X0=1、X1=1,RACK有上升沿时,把总线上的数据打入通用寄存器。可通过设置X1、X0来指定通用寄存器工作方式,通用寄存器的输出端Q0~Q7接入判零电路。LED(ZD)亮时,表示当前通用寄存器内数据为0。

…… …… 余下全文

篇五 :寄存器实验

实验七:寄存器实验

实验题目:寄存器实验

实验类型:设计性

一、实验目的:掌握74HC574寄存器使用方法;掌握component语句和port map语句使用方法;掌握cop2000计算机组成原理实验仪的寄存器组实现方法;能用VHDL语言完成寄存器组的设计与仿真验证。

二、实验仪器设备及实验环境:计算机组成原理实验室,微机一台,quartus II软件。

三、总的设计思想、实验原理:

Cop2000计算机组成原理实验仪是南京伟福实业有限公司开发的实验设备,为配合讲授与学习计算机组成原理课程而研制。

Cop2000具有8位字长结构,实现了8种运算功能的ALU和4个8位字长的通用寄存器,同时ALU使用两个暂存器A和W,从硬件构成上来说,其用74HC574来构成寄存器,对于A、W和4个通用寄存器R0、R1、R2、R3都是用该芯片来实现。为了实现通用寄存器写入和读出的选择,使用了两个2:4译码器。

现在要求在quartusII环境下完成cop2000寄存器组的设计与仿真,可以先分别设计出8位寄存器74HC574和2:4译码器,然后使用component语句和port map语句完成整体设计。

…… …… 余下全文

篇六 :寄存器实验报告

实验报告

实验名称_______________

姓名__________学号___________

同组同学姓名__________学号__________

实验日期______________

实验完成日期______________

1.实验题目名称: 寄存器实验

2.实验目的:1)掌握QuartusII 5.0软件的图形编辑、编译、 仿真的设计流程。

2)学习74670三态输出寄存器堆的使用。

3)了解寄存器组的使用,设计出完善的寄存器组。

3.实验内容:设计出功能完善的寄存器组,并对设计的正确性进行验证。具体要求如下:

1)用图形方式设计出寄存器组的电路原理图。

2)测试波形要用时序仿真实现,现将不同的数据连续写入4个寄存器后,在分别读出。

3)将设计文件封装成器件符号。

4)数据的宽度最好为16位。

…… …… 余下全文

篇七 :A.W寄存器的打入实验

江西理工大学南昌校区

实验报告

【实验目的】

使用计算机原理器材完成A.W寄存的打入

【实验原理】

通过A.W寄存器操作有数据显示在AEN/WEN上面分别为AF/2C。

【实验步骤】

1.首先接通实验器材的电源,打开工作开关。

2.在实验机器器材上找ALU、A/W寄存器,AEN/WEN、K0----K23都是接口。

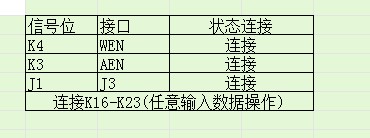

3.连接线路操作,如下图:

4.在器材上连上电源线,按照规定操作,向上打入是显示工作端,向下打入是显示示不工作此端,也可以是控制数据的实现或者数据的输入端口。

5.数据功能的实现ME/TV键盘上自己动手输入“hand...”,接着准备数据输入K16-K23,中任意输入数据,都是十六位的操作,AF=10101111, 2C=00101100。

6.为了得到上面的数据应该有进行step/的产生上位以及产生KEN=AF,WEN=2C,即可以完成了该项试验操作,运行成功。

【实验总结】

通过本实验我们对计算机原理器材内部构造有了一定了解,在老师的指导下,我们得到了相应的结果;与小组人员对遇到的问题进行了激烈的探讨,加强了团队合作能力。

…… …… 余下全文

实验报告

实验报告