十进制计数器实验报告

![文本框: [广东水利电力职业技术学院]](https://upload2.fanwen118.com/wk001/2616734/2616734_img_002.png)

设计一个动态显示十进制计数器

一,前言

本实验将用到七段数码显示译码器.译码器是用来驱动各种显示器件,从而将用二进制代码表示的数字,文字,符号翻译成人们习惯的形式直观地显示出来的电路.这种显示器可用多种发光器件构成.

二,任务书

大家一起讨论,把程序编写出来.我负责建立文件,分配管脚,下载程序,检查错误;罗文驰负责写程序,检查错误;翟国豪负责原理图仿真调试,检查错误;林国强负责硬件的连接,整个设计的解说.

三,设计要求

在七段数码管上自动显示1--9.不用按键控制.

四,设计目的

1,了解数码管的工作原理.

2,学习七段数码管显示译码器的设计.

3,学习Verilog的CASE语句及多层次设计方法.

五,设计方案

本实验要求在时钟信号的作用下,通过输入的键值在数码管上显示相应的键值.在试验中,数字时钟选择1KHZ作为扫描时钟,用四个开关作为输入,当四个开关置为一个二进制数时,在数码管上显示其十六进制的值.实验板中的拨动开关与FPGA的接口连接.

六,设计原理

七,硬件要求

主芯片EPM240T100C5,七段数码管.

八,设计步骤

1,打开QUARTUSII软件,新建一个工程.

2,建完工程后,再建一个VHDL FILE,打开VHDL编辑器对话框.

3,按照实验原理和自己的想法,在VHDL编辑窗口编写Verilog程序.

4,编写完Verilog程序后,保存起来.注意顶体名跟程序实体名要一致.

5,对自己编写的Verilog程序进行编译并仿真,对程序的错误进行修改.

6,编译仿真无误后,进行管脚分配.分配完成后,再进行全编译一次,以 使管脚分配生效.

7,用下载电缆通过JTAG口将对应的xun文件加载到FPGA中.观察实验结果是否与自己的编程思想一致.

九,源程序

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity xun is

port(clk,reset:in std_logic;

dis:out std_logic_vector(6 downto 0);

r:out std_logic_vector(5 downto 0));

end xun;

architecture behav of xun is

signal seg7:std_logic_vector(6 downto 0);

signal countnum: integer range 0 to 9;

signal clk_1k: std_logic;

begin

r<="011111";

process(clk)

variable cnt1:integer range 0 to 5000;

variable cnt2:integer range 0 to 2500;

begin

if clk'event and clk='1' then

if cnt1=5000 then

cnt1:=0;

if cnt2=2500 then

cnt2:=0;

clk_1k<=not clk_1k;

else

cnt2:=cnt2+1;

end if;

else

cnt1:=cnt1+1;

end if;

end if;

end process;

process(reset,clk_1k)

begin

if reset='1' then

if clk_1k'event and clk_1k='1' then

if countnum=9 then

countnum<=0;

else

countnum<=countnum+1;

end if;

end if;

end if;

end process;

process(clk,countnum)

begin

case countnum is

when 0=>seg7<="0111111";

when 1=>seg7<="0000110";

when 2=>seg7<="1011011";

when 3=>seg7<="1001111";

when 4=>seg7<="1100110";

when 5=>seg7<="1101101";

when 6=>seg7<="1111101";

when 7=>seg7<="0000111";

when 8=>seg7<="1111111";

when 9=>seg7<="1100111";

when others=>seg7<="0000000";

end case;

end process;

dis<=seg7;

end;

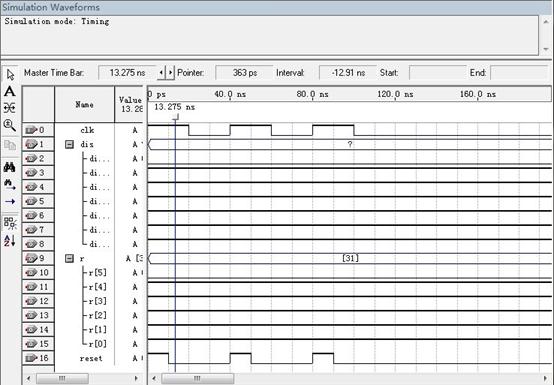

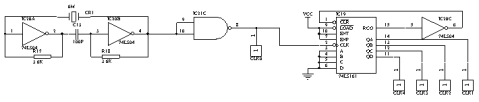

十,原理图仿真调试

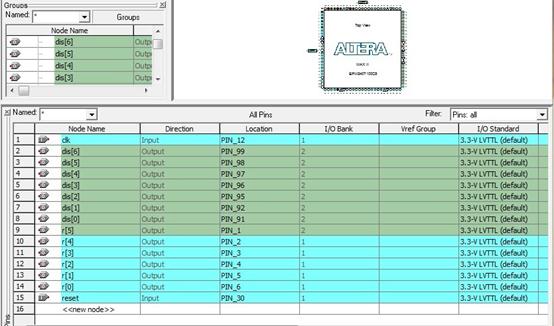

十一,管脚的分配

十二,数据处理及分析结果

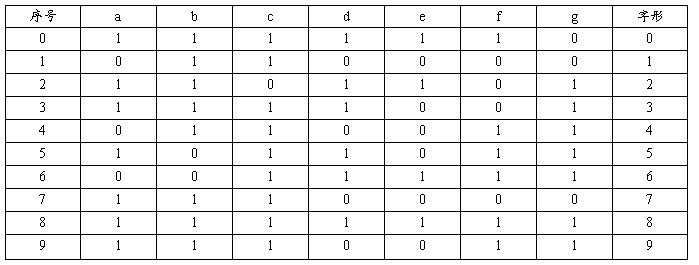

十进制数的显示,都是根据数码管的高低电平和时钟来控制的.

当设计文件加载到目标器件后,将数字信号源50MHZ的数字时钟分频为1KHZ作为扫描时钟(扫描时钟作用是使6个数码管同时显示),使其为一个数值,则6个数码管屏蔽一个后,只有一个显示十六进制的值.

十三,收获和体会

写程序和检查程序是一件很考人耐心和细心的事情.没有现成的程序等着你,什么都是要你动手一步步地实现.做什么事都要细致耐心,多学多问才能会。

通过此次实验让我懂得了十进制计数器的原理和应用以及以后可以自己设计更多不一样功能的彩灯.

熟悉了程序的设计与调试过程.

培养了我们的动手能力和团队合作能力.

有不懂的问题在和组内人讨论后仍没有结果的再去问老师,因为那样才能充分激发我们的创造性思维和提高我们的动手能力.

第二篇:定时计数器(8253)实验报告

实验6 8253定时计数器电路接口实验

2220083443 赵洪宇

一、实验目的

掌握8253定时器的编程原理,用示波器观察不同模式下的输出波形。

二、实验设备

MUT—Ⅲ型实验箱、8086CPU模块、示波器(实验台无)。

三、实验内容

8253计数器0,1,2工作于方波方式,观察其输出波形

四、实验原理介绍

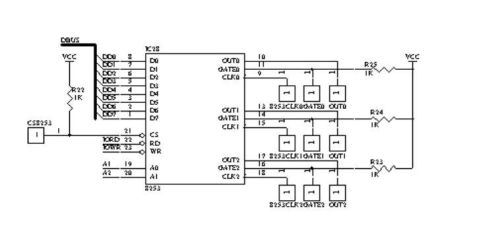

本实验用到两部分电路:脉冲产生电路、8253定时器/计数器电路

(1)电路原理

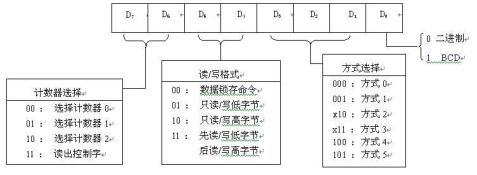

该电路由1片8253组成,8253的片选输入端插孔CS8253,数据口,地址,读写线均已接好,T0、T1、T2时钟输入分别为8253CLK0、8253CLK1、8253CLK2。定时器输出,GATE控制孔对应如下:OUT0、GATE0、OUT1、GATE1、OUT2、GATE2、CLK2。 本实验用到两部分电路:脉冲产生电路、8253定时器/计数器电路

脉冲产生电路

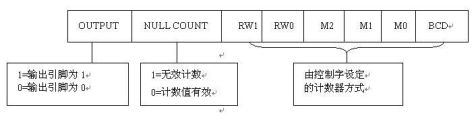

8253的方式控制字

8253的状态字

(2)电路测试

检查复位信号,通过8253定时器/计数器接口实验,程序全速运行,观察片选、读、写、总线信号是否正常。

五、实验步骤

1、实验连线:

CS0 CS8253 OUT0 8253CLK2 OUT2 LED1

示波器(实验中无) OUT1 CLK3 8253CLK0 CLK3 8253CLK1 实验接线原理图如下:

注:GATE信号无输入时为高电平

2、编程调试程序

assume cs:code

code segment public

org 100h

start:

mov dx,04a6h

mov ax,36h

out dx,ax

mov dx,04a0h

mov ax,7Ch

out dx,ax

mov ax,92h

out dx,ax

mov dx,04a6h

mov ax,76h

out dx,ax

mov dx,04a2h

mov ax,32h

out dx,ax

mov ax,0

out dx,ax

mov dx,04a6h

mov ax,0b6h

out dx,ax

mov dx,04a4h

mov ax,04h

out dx,ax

mov ax,0

out dx,ax

next:

nop

jmp next

code ends

end start

;控制寄存器 ;计数器0,方式3 ;计数值927Ch ;计数器1,方式3 ;计数值32h ;计数器2,方式3 ;计数值04h 3、全速运行,观察实验结果

六、实验结果

程序全速运行后,LED1闪烁(周期为0.25s),本实验由于实验台没有提供示波器,所以对于实验所要求的观察方式3的波形无法实现。

七、程序流程图

八、实验总结

通过本次实验,熟悉了8253定时器/计数器的内部工作原理,透彻理解了8253的方式控制字,状态字等功能的实现原理,这是本次实验最大的收获!并且,掌握了对8253的初始化以及运行的过程。锻炼,并熟悉了在MUT—Ⅲ型实验箱实验环境下的操作,在对试验台进行清零操作时要比第一次熟练很多,省去了很多麻烦,还降低了错误的发生。本次实验比较成功,获益匪浅。

-

计数器实验报告

实验4计数器及其应用一实验目的1学习用集成触发器构成计数器的方法2掌握中规模集成计数器的使用及功能测试方法二实验原理计数器是一个用…

-

实验四、 计数器的设计 电子版实验报告

实验四计数器的设计实验室实验台号日期专业班级姓名学号一实验目的1通过实验了解二进制加法计数器的工作原理2掌握任意进制计数器的设计方…

-

数电 计数器实验报告

试验七计数器李*电子信息科学与技术一、试验目的1.掌握中规模集成计数器74LS160,161的逻辑功能及使用方法。2.掌握74LS…

-

实验报告:计数器

四川大学电气信息学院电气工程及其自动化网络专升本实验报告实验课程:电工电子综合实践实验名称:计数器班级:05秋电气工程及其自动化姓…

-

计数器实验报告

计数器实验报告一实验内容1静态测试芯片74LS90的逻辑功能2动态测试芯片73LS90的芯片功能画出clk与其中一个输出的波形图3…

-

计数器实验报告

实验4计数器及其应用一实验目的1学习用集成触发器构成计数器的方法2掌握中规模集成计数器的使用及功能测试方法二实验原理计数器是一个用…

-

秒计数器实验报告

秒计数器实验报告一实验目的1显示60秒计时功能2计时器为60秒递减计时器3根据原理图分析各单元电路的功能4熟悉电路中所用到的各集成…

-

实验六 同步计数器的设计实验报告

数字电路实验报告实验六同步计数器的设计学号姓名一实验目的和要求1熟悉JK触发器的逻辑功能2掌握用JK触发器设计同步计数器二实验仪器…

-

二位计数器实验报告

二位计数器实验报告王林20xx141444014一实验目的1设计一个二位的计数器2熟悉QuartusII软件的功能及环境二详细设计…

-

光电计数器_实验报告

电子系统课程设计设计题目光电计数器作者指导教师光电计数器实验报告工业生产中常常需要自动统计产品的数量数字式电子计数器有直观和计数精…

- 电子技术实验报告7-计数器及其应用