通信原理实验报告

实验二 数字调制

一、 实验目的

1、掌握绝对码、相对码概念及它们之间的变换关系。

2、掌握用键控法产生2ASK、2FSK、2DPSK 信号的方法。

3、掌握相对码波形与2PSK 信号波形之间的关系、绝对码波形与2DPSK 信号波形之间的关系。

4、了解2ASK、2FSK、2DPSK 信号的频谱与数字基带信号频谱之间的关系。

二、实验内容

1、用示波器观察绝对码波形、相对码波形。

2、用示波器观察2ASK、2FSK、2PSK、2DPSK 信号波形。

3、用频谱仪观察数字基带信号频谱及2ASK、2FSK、2DPSK 信号的频谱。

三、基本原理

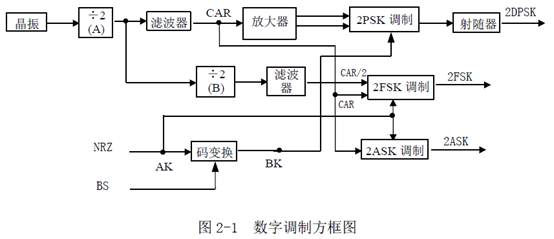

本实验用到数字信源模块和数字调制模块。信源模块向调制模块提供数字基带信号(NRZ 码)和位同步信号BS(已在实验电路板上连通,不必手工接线)。调制模块将输入的绝对码AK(NRZ 码)变为相对码BK、用键控法产生2ASK、2FSK、2DPSK 信号。调制模块内部只用+5V 电压。

本单元有以下测试点及输入输出点:

CAR 2DPSK 信号载波测试点

BK 相对码测试点

2DPSK 2DPSK 信号测试点/输出点,VP-P>0.5V

2FSK FSK 信号测试点/输出点,VP-P>0.5V

2ASK 2ASK 信号测试点,VP-P>0.5V

用2-1 中晶体振荡器与信源共用,位于信源单元,其它各部分与电路板上主要元器件对应关系如下:

2(A) U8: 双D 触发器74LS74

2(B) U9: 双D 触发器74LS74

滤波器A V6: 三极管9013,调谐回路

滤波器B V1: 三极管9013,调谐回路

码变换 U18: 双D 触发器74LS74;U19:异或门74LS86

2ASK 调制 U22: 三路二选一模拟开关4053 ·9·

2FSK 调制 U22: 三路二选一模拟开关4053

2PSK 调制 U21: 八选一模拟开关4051

放大器 V5: 三极管9013

射随器 V3: 三极管9013

将晶振信号进行2 分频、滤波后,得到2ASK 的载频2.2165MHZ。放大器的发射极和集电极输出两个频率相等、相位相反的信号,这两个信号就是2PSK、2DPSK 的两个载波,2FSK 信号的两个载波频率分别为晶振频率的1/2 和1/4,也是通过分频和滤波得到的。

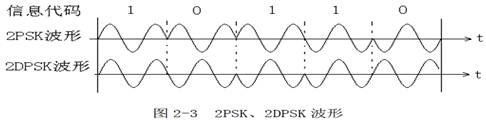

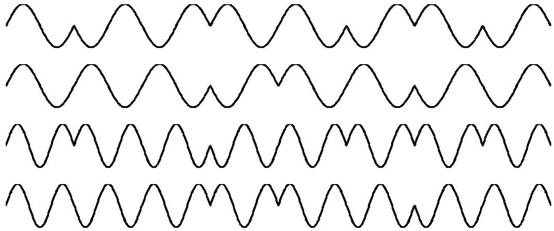

下面重点介绍2PSK、2DPSK。2PSK、2DPSK 波形与信息代码的关系如图2-3 所示。

图中假设码元宽度等于载波周期的1.5 倍。2PSK 信号的相位与信息代码的关系是:前后码元相异时,2PSK 信号相位变化180,相同时2PSK 信号相位不变,可简称为“异变同不变”。2DPSK 信号的相位与信息代码的关系是:码元为“1”时,2DPSK 信号的相位变化180。码元为“0”时,2DPSK 信号的相位不变, 可简称为“1 变0 不变”。

应该说明的是,此处所说的相位变或不变,是指将本码元内信号的初相与上一码元内信号的末相进行比较,而不是将相邻码元信号的初相进行比较。实际工程中,2PSK 或2DPSK 信号载波频率与码速率之间可能是整数倍关系也可能是非整数倍关系。但不管是那种关系,上述结论总是成立的。

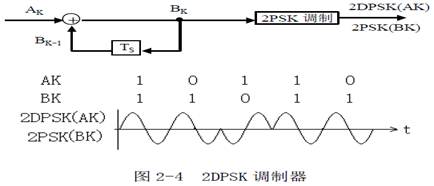

本单元用码变换——2PSK 调制方法产生2DPSK 信号,原理框图及波形图如图2-4 所示。相对于绝对码AK、2PSK 调制器的输出就是2DPSK 信号,相对于相对码、2PSK 调制器的输出是2PSK 信号。图中设码元宽度等于载波周期,已调信号的相位变化与AK、BK 的关系当然也是符合上述规律的,即对于AK 来说是“1 变0 不变”关系,对于BK 来说是“异变同不变”关系,由AK 到BK 的变换也符合“1 变0 不变” 规律。

图2-4 中调制后的信号波形也可能具有相反的相位,BK 也可能具有相反的序列00100,这取决于载波的参考相位以及异或门电路的初始状态。

2DPSK 通信系统可以克服上述2PSK 系统的相位模糊现象,故实际通信中采用2DPSK 而不用2PSK(多进制下亦如此,采用多进制差分相位调制MDPSK),此问题将在数字解调实验中再详细介绍。

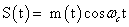

2PSK 信号的时域表达式为

式中m(t)为双极性不归零码BNRZ,当“0”、“1”等概时m(t)中无直流分量,S(t)中无载频分量,2DPSK 信号的频谱与2PSK 相同。

2ASK 信号的时域表达式与2PSK 相同,但m(t)为单极性不归零码NRZ,NRZ 中有直流分量,故2ASK 信号中有载频分量。

2FSK 信号(相位不连续2FSK)可看成是AK 与调制不同载频信号形成的两个2ASK 信号相加。时域表达式为 AK

? ? ?

?

式中m(t)为NRZ 码。

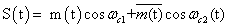

图 2-5 2ASK,2PSK,2FSK的频谱图

设码元宽度为TS, 在数值上等于码速率,2ASK、2PSK(2DPSK)、2FSK 的功率谱密度如图2-5 所示。可见,2ASK、2PSK(2DPSK)的功率谱是数字基带信号m(t)功率谱的线性搬移,故常称2ASK、2PSK (2DPSK)为线性调制信号。多进制的MASK、MPSK(MDPSK)、MFSK 信号的功率谱与二进制信号功率谱类似。

在数值上等于码速率,2ASK、2PSK(2DPSK)、2FSK 的功率谱密度如图2-5 所示。可见,2ASK、2PSK(2DPSK)的功率谱是数字基带信号m(t)功率谱的线性搬移,故常称2ASK、2PSK (2DPSK)为线性调制信号。多进制的MASK、MPSK(MDPSK)、MFSK 信号的功率谱与二进制信号功率谱类似。

本实验系统中m(t)是一个周期信号,故m(t)有离散谱,因而2ASK、2PSK(2DPSK)、2FSK 也具有离散谱。

四、实验步骤

本实验使用数字信源单元及数字调制单元。

1、熟悉数字调制单元的工作原理。接好电源线,打开实验箱电源开关。

2、用数字信源单元的FS 信号作为示波器的外同步信号,示波器CH1 接信源单元的(NRZ-OUT)AK,CH2 接数字调制单元的BK,信源单元的K1、K2、K3 置于任意状态(非全0),观察AK、BK 波形,总结绝对码至相对码变换规律以及从相对码至绝对码的变换规律。

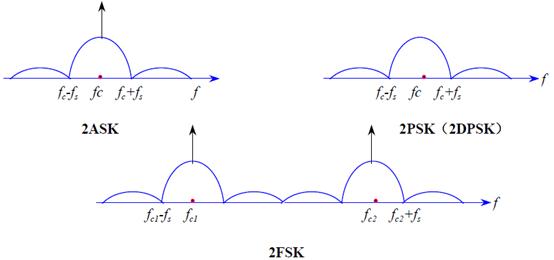

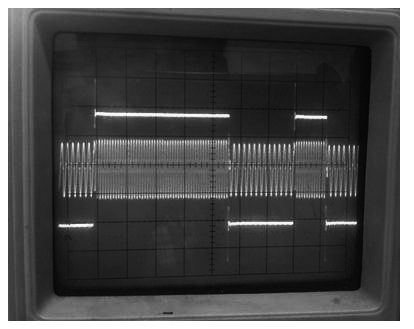

图 2-6 AK和BK信号

结论:从图中结果,总结AK信号和BK信号的关系为: ,反过来,

,反过来, 。由于异或1相当于取反,异或0相当于保持。所以当

。由于异或1相当于取反,异或0相当于保持。所以当 时,

时, ,而当

,而当 时,

时, 。

。

最终的BK波形由 的首个参考相位决定。

的首个参考相位决定。

3、示波器CH1 接2DPSK,CH2 分别接AK 及BK,观察并总结2DPSK 信号相位变化与绝对码的关系以及2DPSK 信号相位变化与相对码的关系。

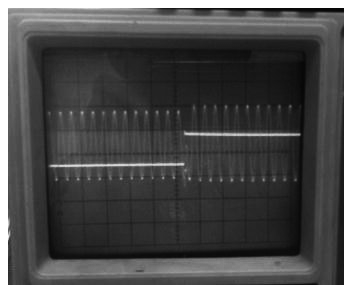

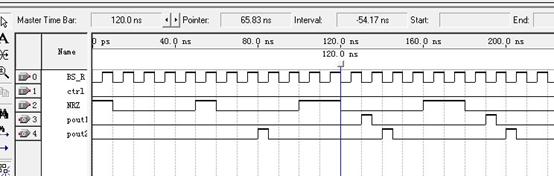

图 2-7 AK和2DPSK信号

结论:2DPSK信号在AK码元为“1”时反相。

图 2-8 BK和2DPSK信号

结论:2DPSK信号在BK信号的前后码元不一致时反相。

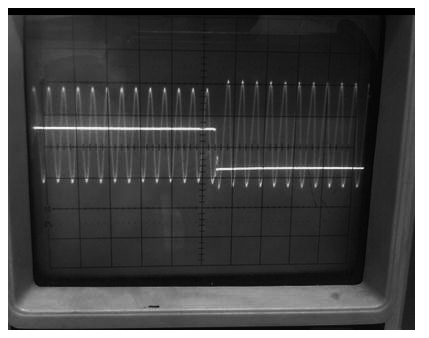

4、示波器CH1 接AK、CH2 依次接2FSK 和2ASK;观察这两个信号与AK 的关系。

图 2-9 AK信号和2FSK信号

结论: 2FSK信号中,在AK信号码元为“1”是,对应已调波有载波振幅,码元为“0”时,无已调载波波振幅。

图 2-10 AK信号和2ASK信号

结论:2ASK信号在AK信号码元为“0”和“1”时,分别有两种频率不同的载波振幅。

五、实验报告思考总结:

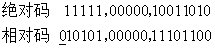

1、设绝对码为全1、全0 或1001 1010,求相对码。

2、设信息代码为1001 1010,载频分别为码元速率的1 倍和1.5 倍,画出2DPSK 及2PSK 信号波形。

图 2-15 2DPSK 及2PSK 信号波形

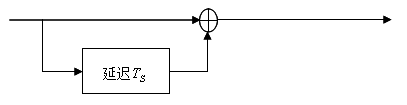

3、总结绝对码至相对码的变换规律、相对码至绝对码的变换规律并设计一个由相对码至绝对码的变换电路。

① 绝对码至相对码的变换规律:

“1”变“0”不变,即绝对码的“1”码时相对码发生变化,绝对码的“0”码时相对码不发生变化。——此为信号差分码。(参考码任意取,所以最终由两种相反的结果。)

② 相对码至绝对码的变换规律:

相对码的当前码元与前一码元相同时对应的当前绝对码为“0”码,相异时对应的当前绝对码为“1”码。(同样,参考码任意取,所以最终由两种相反的结果。)

可行的电路:

可行的电路:

4、总结2DPSK 信号的相位变化与信息代码(即绝对码)之间的关系以及2DPSK 信号的相位变化与相对码之间的关系(即2PSK 的相位变化与信息代码之间的关系)。

2DPSK 信号的相位变化与绝对码(信息代码)之间的关系是:“1 变0 不变”,即“1”码对应的2DPSK 信号的初相相对于前一码元内2DPSK 信号的末相变化180º,“0”码对应的2DPSK 信号的初相与前一码元内2DPSK 信号的相位相同。

2PSK 信号的相位变化与相对码(信息代码)之间的关系是:“异变同不变”,即当前码元与前一码元相异时则当前码元内2PSK 信号的初相相对于前一码元内2PSK 信号的末相变化180º,相同时则码元内2PSK 信号的初相相对于前一码元内2PSK 信号的相位无变化。

第二篇:通信原理实验报告liu

基于CPLD/FPGA的AMI/HDB3编译码设计

姓名: 2班39号

摘要:本设计重点介绍采用基于CPLD/FPGA的VHDL语言通过Quartus2软件对AMI/HDB3码进行编码和译码的过程,让我们了解基带信号怎样变换为AMI/HDB3的原理,并且AMI/HDB3码又怎样还原成基带信号!!并且通过波形仿真,和逻辑模块的设计让我们更加形象,细致的了解关于AMI/HDB3的码型变换。

关键词:基带信号,AMI/HDB3码,双极性归零,破坏码,正负极性,编码,译码

1. 设计原理

(1),AMI是传号交替反转码。其编码规则是将二进制代码“1”(传号)交替的变换为传输码的“+1”和“-1”,而“0”(空号)保持不变。例如:

消息代码: 1 0 0 1 1 0 0 0 0 0 0 0 1 1 0 0 1 1

AMI代码:+1 0 0 -1 +1 0 0 0 0 0 0 0 -1 +1 0 0 -1 +1

AMI码对应的基带信号是正负极性交替的脉冲序列,而0电位保持不变,此外AMI码的编译码电路简单,便于利用传号极性交替规律观察误码情况。但AMI码也有其不足,当原信码出现连“0”串时,信号的电平长时间不跳变,造成提取定时信号的困难。解决“0”码问题的有效方法之一就是采用下面的HDB3码。

(2),HDB3码的全称是3阶高密度双极性码,它是AMI码的改进型,其目的是为了保持AMI码的优点而克服其缺点,使连“0”的个数不超过3个。其编码规则如下:

1),当信码的连“0”个数不超过3时,扔按AMI码的规则编,即传号极性交替;

2),当连“0”的个数超过3时,则将第四个“0”改为非“0”的脉冲,记为+V或-V,

称之为破坏脉冲。相邻V码的极性必须交替出现,以确保编好的码中无直流;

3),为了便于识别,V码的极性应与其前一个非“0”脉冲极性相同,否则,将“0”的第一个“0”更改为与该破坏脉冲相同的极性脉冲,并记为+B或-B ;

4),破坏脉冲之后的传号码极性也要交替。其中+V,-V,脉冲和+B和-B脉冲与+1,-1脉冲波形相同,用V或B符号的目的是为了示意是将原信码的“0”变换成“1”码。

虽然HDB3码的编码规则比较复杂,但译码却比较简单。从上述原理看出,每一个破坏码符号V总是与前一非“0”符号同极性。这就是说,从收到的符号序列中可以容易的找到破坏点V,于是也断定V符号以及前面的3个符号必须是连续的0符号,从而恢复4个连0码,再将所有-1变成+1后便得到原来的消息代码。

2.设计思路

(1),AMI/HDB3编码单元中的端口为基带信号NRZ码、电平控制信号ctrl、正极性输出pout1和负极性输出pout2(因为AMI/HDB3的编码为双极性归零码,而仿真波形中没有双极性编码,因此将双极性码分离为正负极性的2组码)。当ctrl端口接高电平时进行HDB3码的编码,当电平控制ctrl端口接低电平时进行AMI编码,单元输出两路并行信号pout1和pout2,分别与AMI码或HDB3码的正极性信号和负极性信号相对应,这两个信号作为AMI/HDB3编译码模块中的单双极性变换器的输入信号,同时经过ctrl的控制和经极性变换后得到AMI码或HDB3码。

(2), 在译码单元中将编码单元输出的将AMI/HDB3双极性转换的2路单极性码作为输入信号,控制电平ctrl控制译码为AMI码或HDB3码。最后由输出端口输出译码后的信号。

(3),在这里可以将编码单元和译码单元分开设计,先进行编码的设计,并进行波形仿真,然后进行译码设计,在波形仿真时将译码器的输入信号波形设置为和编码器的输出波形一致,然后进行编译,对比译码的仿真输出波形是否和编码的基带输入信号一致.从而确定程序是否出现差错!!

3.模块的设计

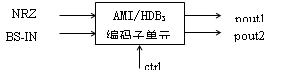

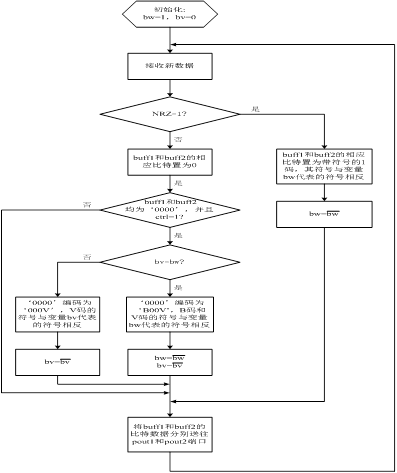

(1)、.编码单元模块

NRZ:基带输入信号 BS-IN:位同步信号 ctrl:输出码型控制信号

pout1:输出码极性变换后的正极性输出

pout2:输出码极性变换后的负极性输出

AMI/HDB3编码单元的算法流程图

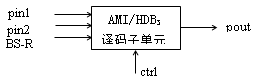

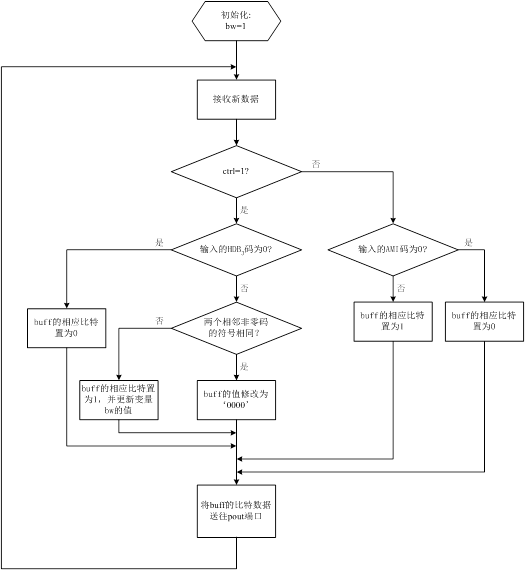

(2)、译码单元模块

Pin1:输入信号,与编码单元中的pout1相连

Pin2:输入信号,与编码单元中的pout2相连

BS-R: 位同步信号:ctrl:控制AMI码或HDB3码译码为原信号

Pout:译码后的信号输出端口

AMI/HDB3 译码单元算法流程图

AMI/HDB3 译码单元算法流程图

4、仿真,分析

代码: 1 000 0 1 000 0 1 1 000 0 1 1

AMI码: -1 000 0 +1 000 0 -1 +1 000 0-1+1

HDB3码:-1 000-V +1 000+V -1 +1-B00-V+1-1

其中HDB3码也可以以+1开始

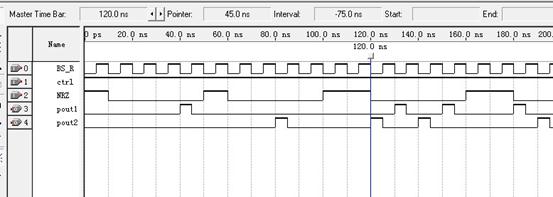

(1)、 首先进行AMI/HDB3码编码的仿真.

Ctrl为低电平时为AMI编码!!

Ctrl 为高电平时为HDB3编码!

此为ctrl为低电平时AMI编码!依图可观察出输出延时了7个时间脉冲!!第一个码编为 ”-1”

此为ctrl为高电平时编的HDB3码!可通过观察知第一个高电平编为”+1”

且有3个时间脉冲的延时.

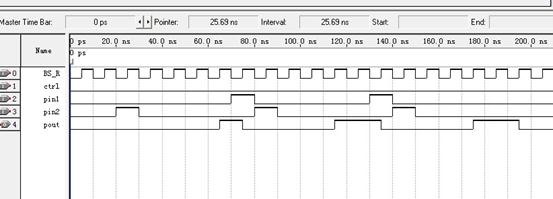

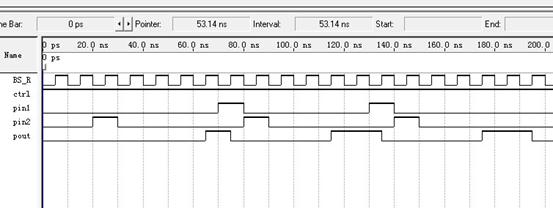

(2),进行译码,将AMI/HDB3码还原成基带NRZ信号即为图中的pout

ctrl为低电平时为AMI译码。

ctrl为高电平时为HDB3译码

此为ctrl为低电平时的AMI译码,由图看出译码而出的信号有一定的延时。

此为ctrl为高电平时的HDB3码译码,输入,输出之间有一定的延时。

此为编译码逻辑原理图!前面为输入端,然后编码器,译码器,最后输出端口。

5.结果

由波形仿真图分析其高低电平,得出编码,译码的码字,并比较编码器的输入,和译码器的输出,看是否一致,得出在误差范围内输入,输出相一致,实验设计成功!!

6、总结

通过对通信原理实验中的AMI/HDB3码的设计,我加深了对基于CPLD/FPGA设计的认识,并通过本次设计基本掌握了Quartus2的基本应用,并且也加深了对编译语言VHDL的认识!!对其他的关于EDA的课程奠定了一定的基础。通过本次设计实验还加深了对AMI/HDB3码的认识和了解,通过亲自的编码和译码过程以及波形仿真更加形象的学习了基带传输中的常用码型AMI/HDB3码,也为《通信原理》中后续章节的学习做铺垫。

参考文献

[1] 樊昌信.通信原理(第五版)[M].北京:国防工业出版社。2002.8

[2] 张辉,曹丽娜.现代通信原理与技术(第二版).西安:西安电子科技大学出版社。2009.2

[3] 曹志刚.现代通信原理. 北京:清华大学出版社。2001.4

-

通信原理实验报告

通信原理实验基于MATLAB仿真的BPSK的调制与解调班级姓名指导教师实验时间基于MATLAB仿真的BPSK的调制与解调一实验要求…

- 通信原理实验报告

-

通信报告通信原理实验心得体会

通信原理实验心得体会091180024代岳通信工程众所周知,《通信原理》是电子、通信、计算机、自控和信息处理等专业的重要基础课,所…

-

通信原理实验报告

湖北民族学院信息工程学院实验报告班级15班姓名董非凡学号k031041533成绩试验时间20xx年4月21日12节实验地点实验楼五…

-

通信原理课程设计报告(基于Matlab)

青岛农业大学理学与信息科学学院通信原理课程报告设计题目2DPSK调制与解调系统的仿真学生专业班级电子信息工程学生姓名学号指导教师完…

-

通信原理实验报告

现代通信原理课程设计报告设计题目题目2专业班级学号20xx101026姓名刘敬亚任课教师设计时间题目2一设计任务与要求1设计目的使…

-

通信原理实验报告

湖北民族学院信息工程学院实验报告班级15班姓名董非凡学号k031041533成绩试验时间20xx年4月21日12节实验地点实验楼五…

-

电子科技大学通信原理实验实验报告2

电子科技大学通信学院最佳接收机匹配滤波器实验报告班级学生学号教师任通菊最佳接收机匹配滤波器实验一实验目的1运用MATLAB软件工具…

-

通信原理实验报告

广西科技大学课程名称指导教师班级姓名学号成绩评定实验报告实验一数字基带信号一实验目的1了解单极性码双极性码归零码不归零码等基带信号…

-

电子科技大学通信原理实验实验报告3

电子科技大学通信学院最佳接收机匹配滤波器实验报告班级物联网1班学生谢一平学号20xx010906007教师任通菊最佳接收机匹配滤波…

-

大物实验示波器的使用实验报告

实验二十三示波器的使用班级姓名学号同组人日期【实验目的】1、了解示波器的基本结构和工作原理,学会正确使用示波器。2、掌握用示波器观…