电子秒表设计VHDL

一、 设计题目:

基于VHDL语言的电子秒表设计(可调时,有闹钟、定时功能)

二、 设计目的:

⑴掌握较复杂的逻辑设计和调试

⑵学习用原理图+VHDL语言设计逻辑电路

⑶学习数字电路模块层次设计

⑷掌握QuartusII软件及Modelsim软件的使用方法

三、 设计内容:

(一)设计要求

1、具有以二十四小时计时、显示、整点报时、时间设置和闹钟的功能。

2、设计精度要求为1S。

(二).系统功能描述

1 . 系统输入:系统状态及校时、定时转换的控制信号为k、set、ds;

时钟信号clk,采用实验箱的50MHz;

系统复位信号为reset。输入信号均由按键产生。

系统输出:8位LED七段数码管显示输出,蜂鸣器声音信号输出。

多功能数字钟系统功能的具体描述如下:

2. 计时:set=1,ds=1工作状态下,每日按24h计时制计时并显示,蜂鸣器无声,逢整点报时。

3. 校时:在set=0,ds=0状态下,按下“k键”,进入“小时”校准状态,之后按下“k键”则进入“分”校准状态,继续按下“k键”则进入“秒校准”状态,之后如此循环。

1)“小时”校准状态:在“小时”校准状态下,显示“小时”数码管以1Hz的频率递增计数。

2)“分”校准状态:在“分”校准状态下,显示“分”的数码管以1Hz的频率递增计数。

3)“秒”复零状态:在“秒复零”状态下,显示“分”的数码管以1Hz的频率递增计数。

4. 整点报时:蜂鸣器在“59”分钟的第50—59,以1秒为间隔分别发出1000Hz,500Hz的声音。

5. 显示:采用扫描显示方式驱动8个LED数码管显示小时、分、秒。

闹钟:闹钟定时时间到,蜂鸣器发出交替周期为1s的1000Hz、500Hz的声音,持续时间为一分钟;

6. 闹钟定时设置:在set=0,ds=1状态下,按下“k”,进入闹钟的“时”设置状态,之后按下“k键”进入闹钟的“分”设置状态,继续按下“k 键”则进入“秒”设置状态, 之后如此循环。

1) 闹钟“小时”设置状态:在闹钟“小时”设置状态下,显示“小时”的数码管以1Hz的频率递增计数。

2) 闹钟:“分”设置状态:在闹钟“分”设置状态下,显示“分”的数码管以1Hz的频率递增计数。

7. 定时器功能:在set=1,ds=0状态下,按下“k”,进入定时器的“时”设置状态,之后按下“k键”进入定时器的“分”设置状态,继续按下“k 键”则进入“秒”设置状态, 之后如此循环。在dsk=1时,定时器以1s为单位开始倒时,当dsk=0,停止倒时,在最后的十秒时间,蜂鸣器发出声音。

(三)各功能模块设计说明及源程序

1.1000Hz分频模块

产生1000Hz频率

2.1Hz模块

产生1Hz频率

3.计时,定时,闹钟,校时模块

通过装换不同的状态,分别实现计时,定时,闹钟,校时功能;源程序如下

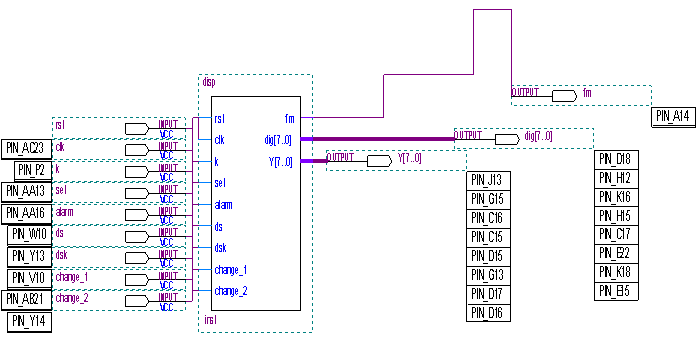

4.顶层显示模块

显示数码管,源代码如下:

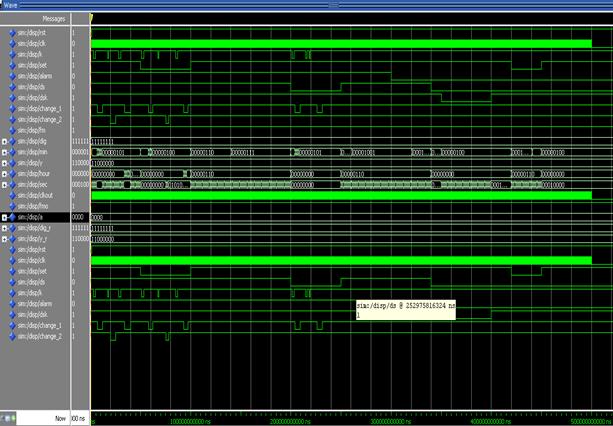

(四).Modelsim综合仿真图

四.总结及体会

通过这次电子设计大赛课程设计,我学到了很多,对于原本掌握的不好的数字逻辑相关知识,在课程设计具体实践中有了很深刻的认识,在对于Quartus+Modelsim仿真的操作上也有很大的提高,增加了操作的熟练程度。

通过实验调试,我才真正地认识到了信号与变量的区别以及他们的使用方法。这份报告是用VHDL代码写的,比较长。相比之下,VERILOG语言显得简洁多了。不过可能是对VERILOG的学习还不够,调试中出现比较多的问题。故最后还是选择了VHDL语言的这份。

最后,感谢在思维陷入困境时给予我指点,让我获得灵感的同学们!

附录:各模块源程序

1.1000Hz模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity frediv_1000 is

port

(

clk : in std_logic;

clkout : out std_logic

);

end frediv_1000;

architecture rt3 of frediv_1000 is

begin

process(clk)

variable count:integer range 0 to 50000;

begin

if clk'event and clk = '1' then

if count = 49999 then

count := 0;

else

count := count + 1;

if count <= 24999 then

clkout <= '1';

else

clkout <= '0';

end if;

end if;

end if;

end process;

end rt3;

2. 1HZ模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity frediv is

port

(

clk : in std_logic;

clkout : out std_logic

);

end frediv;

architecture rt1 of frediv is

begin

process(clk)

variable count:integer range 0 to 50000000;

begin

if clk'event and clk = '1' then

if count = 49999999 then

count := 0;

else

count := count + 1;

if count <= 24999999 then

clkout <= '1';

else

clkout <= '0';

end if;

end if;

end if;

end process;

end rt1;

3.计时,定时,闹钟,校时模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity adjust is

port

(

rst,clk,k,set,alarm,ds,dsk : in std_logic;

change_1,change_2 : in std_logic;

fmo : out std_logic;

sec,min,hour : out std_logic_vector(7 downto 0)

);

end adjust;

architecture rt1 of adjust is

signal clk_1Hz,clk_1000Hz,clk_500Hz :std_logic;

signal sec_r,min_r,hour_r :std_logic_vector(7 downto 0);

signal sec_ra,min_ra,hour_ra :std_logic_vector(7 downto 0);

signal sec_rd,min_rd,hour_rd :std_logic_vector(7 downto 0);

signal fm_1 :std_logic;

signal cht,cmt,cst,cha,cma,csa,chd,cmd,csd :std_logic;

signal sel_show :std_logic_vector(1 downto 0);

type state_type is(s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11);

signal state:state_type;

component frediv

port

(

clk : in std_logic;

clkout : out std_logic

);

end component;

component frediv_1000

port

(

clk : in std_logic;

clkout : out std_logic

);

end component;

begin

U1:frediv port map(clk,clk_1Hz);

U3:frediv_1000 port map(clk,clk_1000Hz);

-------500Hz

process(clk_1000Hz,rst)

begin

if (rising_edge(clk_1000Hz)) then

if(rst = '0') then

clk_500Hz <='0';

else

clk_500Hz <=not clk_500Hz;

end if;

end if;

end process;

process(clk)

begin

if sel_show(1 downto 0) = "11" then --shizhong

sec <= sec_r;

min <= min_r;

hour <= hour_r;

else if sel_show(1 downto 0) = "01" then--naozhong

sec <= sec_ra;

min <= min_ra;

hour <= hour_ra;

else if sel_show(1 downto 0) = "10" then--dingshi

sec <= sec_rd;

min <= min_rd;

hour <= hour_rd;

else if sel_show(1 downto 0) = "00" then--shizhong

sec <= sec_r;

min <= min_r;

hour <= hour_r;

end if;

end if;

end if;

end if;

end process;

process(clk_1Hz)

begin

if(rising_edge(clk_1Hz))then

if(rst='0')then

state<=s0;

sel_show(1 downto 0)<="11";

cht<='0';cmt<='0';cst<='0';

cha<='0';cma<='0';csa<='0';

chd<='0';cmd<='0';csd<='0';

else if (set = '1'and ds='1')then

sel_show(1 downto 0)<="11";

if(state=s4 or state=s5 or state=s6 or state=s7 or state=s8 or state=s9 or state=s10 or state=s11)then

state<=s0;

else if( state=s0)then

if(k='0')then

state<=s1;

else state<=s0;

end if;

else if(state=s1)then

cht<='1';cmt<='0';cst<='0';

cha<='0';cma<='0';csa<='0';

chd<='0';cmd<='0';csd<='0';

if(k='0')then

state<=s2;

else state<=s1;

end if;

else if(state=s2)then

cht<='0';cmt<='1';cst<='0';

cha<='0';cma<='0';csa<='0';

chd<='0';cmd<='0';csd<='0';

if(k='0')then

state<=s3;

else state<=s2;

end if;

else if( state=s3 )then

cht<='0';cmt<='0';cst<='1';

cha<='0';cma<='0';csa<='0';

chd<='0';cmd<='0';csd<='0';

if(k='0')then

state<=s0;

else state<=s3;

end if;

end if;

end if;

end if;

end if;

end if;

else if(set='0'and ds='1')then

sel_show(1 downto 0)<="01";

cht<='0';cmt<='0';cst<='0';

cha<='0';cma<='0';csa<='0';

chd<='0';cmd<='0';csd<='0';

if(state=s0 or state=s1 or state=s2 or state=s3 or state=s8 or state=s9 or state=s10 or state=s11)then

state<=s4;

else if( state=s4)then

if(k='0')then

state<=s5;

else

state<=s4;

end if;

else if( state=s5)then

cht<='0';cmt<='0';cst<='0';

cha<='1';cma<='0';csa<='0';

chd<='0';cmd<='0';csd<='0';

if(k='0')then

state<=s6;

else

state<=s5;

end if;

else if(state=s6 )then

cht<='0';cmt<='0';cst<='0';

cha<='0';cma<='1';csa<='0';

chd<='0';cmd<='0';csd<='0';

if(k='0')then

state<=s7;

else

state<=s6;

end if;

else if(state=s7)then

cht<='0';cmt<='0';cst<='0';

cha<='0';cma<='0';csa<='1';

chd<='0';cmd<='0';csd<='0';

if(k='0')then

state<=s4;

else

state<=s7;

end if;

end if;

end if;

end if;

end if;

end if;

else if(set='1'and ds='0')then

sel_show(1 downto 0)<="10";

cht<='0';cmt<='0';cst<='0';

cha<='0';cma<='0';csa<='0';

chd<='0';cmd<='0';csd<='0';

if(state=s0 or state=s1 or state=s2 or state=s3 or state=s4 or state=s5 or state=s6 or state=s7)then

state<=s8;

else if( state=s8)then

if(k='0')then

state<=s9;

else

state<=s8;

end if;

else if( state=s9)then

cht<='0';cmt<='0';cst<='0';

cha<='0';cma<='0';csa<='0';

chd<='1';cmd<='0';csd<='0';

if(k='0')then

state<=s10;

else

state<=s9;

end if;

else if(state=s10 )then

cht<='0';cmt<='0';cst<='0';

cha<='0';cma<='0';csa<='0';

chd<='0';cmd<='1';csd<='0';

if(k='0')then

state<=s11;

else

state<=s10;

end if;

else if(state=s11)then

cht<='0';cmt<='0';cst<='0';

cha<='0';cma<='0';csa<='0';

chd<='0';cmd<='0';csd<='1';

if(k='0')then

state<=s8;

else

state<=s11;

end if;

end if;

end if;

end if;

end if;

end if;

else

sel_show(1 downto 0) <= "00";

cht<='0';cmt<='0';cst<='0';

cha<='0';cma<='0';csa<='0';

chd<='0';cmd<='0';csd<='0';

end if;

end if;

end if;

end if;

end if;

end process;

process(clk_1Hz)

begin

if clk_1Hz'event and clk_1Hz = '1' then

if rst = '0' then

sec_r <= "00000000";

min_r <= "00000000";

hour_r <= "00000000";

else if (change_1 = '0' and cmt = '1') then

if min_r(3 downto 0) >= 9 then

min_r(3 downto 0) <= "0000";

if min_r(7 downto 4) >= 5 then

min_r(7 downto 4) <= "0000";

else

min_r(7 downto 4) <= min_r(7 downto 4) + "1";

end if;

else

min_r(3 downto 0) <= min_r(3 downto 0) + "1";

end if;

else if (change_2 = '0' and cmt = '1') then

if min_r(3 downto 0) <= 0 then

min_r(3 downto 0) <= "1001";

if min_r(7 downto 4) <= 0 then

min_r(7 downto 4) <= "0101";

else

min_r(7 downto 4) <= min_r(7 downto 4) - "1";

end if;

else

min_r(3 downto 0) <= min_r(3 downto 0) - "1";

end if;

else if (change_1 = '0' and cht = '1') then

if (hour_r(7 downto 4) = 2 and hour_r(3 downto 0) = 3 ) then

hour_r <= "00000000";

else

if(hour_r(3 downto 0) >= 9)then

hour_r(3 downto 0) <= "0000";

hour_r(7 downto 4) <= hour_r(7 downto 4) + "1";

else

hour_r(3 downto 0) <= hour_r(3 downto 0) + "1";

end if;

end if;

else if (change_2 = '0' and cht = '1') then

if (hour_r(7 downto 4) = 0 and hour_r(3 downto 0) = 0 ) then

hour_r <= "00100011";

else

if(hour_r(3 downto 0) <= 0 and hour_r(7 downto 4) < 2)then

hour_r(3 downto 0) <= "1001";

hour_r(7 downto 4) <= hour_r(7 downto 4) - "1";

else

hour_r(3 downto 0) <= hour_r(3 downto 0) - "1";

end if;

end if;

else if (change_1 = '0' and cst = '1') then

if sec_r(3 downto 0) >= 9 then

sec_r(3 downto 0) <= "0000";

if sec_r(7 downto 4) >= 5 then

sec_r(7 downto 4) <= "0000";

else

sec_r(7 downto 4) <= sec_r(7 downto 4) + "1";

end if;

else

sec_r(3 downto 0) <= sec_r(3 downto 0) + "1";

end if;

else if (change_2 = '0' and cst = '1') then

if sec_r(3 downto 0) <= 0 then

sec_r(3 downto 0) <= "1001";

if sec_r(7 downto 4) <= 0 then

sec_r(7 downto 4) <= "0101";

else

sec_r(7 downto 4) <= sec_r(7 downto 4) - "1";

end if;

else

sec_r(3 downto 0) <= sec_r(3 downto 0) - "1";

end if;

else

if sec_r(3 downto 0) >= 9 then

sec_r(3 downto 0) <= "0000";

if sec_r(7 downto 4) >= 5 then

sec_r(7 downto 4) <= "0000";

if min_r(3 downto 0) >= 9 then

min_r(3 downto 0) <= "0000";

if min_r(7 downto 4) >= 5 then

min_r(7 downto 4) <= "0000";

if hour_r(7 downto 4) = 2 then

if hour_r(3 downto 0) = 3 then

hour_r <= "00000000";

else

hour_r(3 downto 0) <= hour_r(3 downto 0) + "1";

end if;

else

if(hour_r(3 downto 0) >= 9)then

hour_r(3 downto 0) <= "0000";

hour_r(7 downto 4) <= hour_r(7 downto 4) + "1";

else

hour_r(3 downto 0) <= hour_r(3 downto 0) + "1";

end if;

end if;

else

min_r(7 downto 4) <= min_r(7 downto 4) + "1";

end if;

else

min_r(3 downto 0) <= min_r(3 downto 0) + "1";

end if;

else

sec_r(7 downto 4) <= sec_r(7 downto 4) + "1";

end if;

else

sec_r(3 downto 0) <= sec_r(3 downto 0) + '1';

end if;

end if;

end if;

end if;

end if;

end if;

end if;

end if;

end if;

end process;

process(clk_1Hz)

begin

if clk_1Hz'event and clk_1Hz = '1' then

if rst = '0' then

sec_ra <= "00000000";

min_ra <= "00000000";

hour_ra<= "00000000";

else if (change_1 = '0' and cma = '1') then

if min_ra(3 downto 0) >= 9 then

min_ra(3 downto 0) <= "0000";

if min_ra(7 downto 4) >= 5 then

min_ra(7 downto 4) <= "0000";

else

min_ra(7 downto 4) <= min_ra(7 downto 4) + "1";

end if;

else

min_ra(3 downto 0) <= min_ra(3 downto 0) + "1";

end if;

else if (change_2 = '0' and cma = '1') then

if min_ra(3 downto 0) <= 0 then

min_ra(3 downto 0) <= "1001";

if min_ra(7 downto 4) <= 0 then

min_ra(7 downto 4) <= "0101";

else

min_ra(7 downto 4) <= min_ra(7 downto 4) - "1";

end if;

else

min_ra(3 downto 0) <= min_ra(3 downto 0) - "1";

end if;

else if (change_1 = '0' and cha = '1') then

if (hour_ra(7 downto 4) = 2 and hour_ra(3 downto 0) = 3 ) then

hour_ra <= "00000000";

else

if(hour_ra(3 downto 0) >= 9)then

hour_ra(3 downto 0) <= "0000";

hour_ra(7 downto 4) <= hour_ra(7 downto 4) + "1";

else

hour_ra(3 downto 0) <= hour_ra(3 downto 0) + "1";

end if;

end if;

else if (change_2 = '0' and cha = '1') then

if (hour_ra(7 downto 4) = 0 and hour_ra(3 downto 0) = 0 ) then

hour_ra <= "00100011";

else

if(hour_ra(3 downto 0) <= 0 and hour_ra(7 downto 4) < 2)then

hour_ra(3 downto 0) <= "1001";

hour_ra(7 downto 4) <= hour_ra(7 downto 4) - "1";

else

hour_ra(3 downto 0) <= hour_ra(3 downto 0) - "1";

end if;

end if;

else if (change_1 = '0' and csa = '1') then

if sec_ra(3 downto 0) >= 9 then

sec_ra(3 downto 0) <= "0000";

if sec_ra(7 downto 4) >= 5 then

sec_ra(7 downto 4) <= "0000";

else

sec_ra(7 downto 4) <= sec_ra(7 downto 4) + "1";

end if;

else

sec_ra(3 downto 0) <= sec_ra(3 downto 0) + "1";

end if;

else if (change_2 = '0' and csa = '1') then

if sec_ra(3 downto 0) <= 0 then

sec_ra(3 downto 0) <= "1001";

if sec_ra(7 downto 4) <= 0 then

sec_ra(7 downto 4) <= "0101";

else

sec_ra(7 downto 4) <= sec_ra(7 downto 4) - "1";

end if;

else

sec_ra(3 downto 0) <= sec_ra(3 downto 0) - "1";

end if;

end if;

end if;

end if;

end if;

end if;

end if;

end if;

end if;

end process;

process(clk_1Hz)

begin

if clk_1Hz'event and clk_1Hz = '1' then

if rst = '0' then

sec_rd <= "00000000";

min_rd <= "00000000";

hour_rd <= "00000000";

else if (change_1 = '0' and cmd = '1') then

if min_rd(3 downto 0) >= 9 then

min_rd(3 downto 0) <= "0000";

if min_rd(7 downto 4) >= 5 then

min_rd(7 downto 4) <= "0000";

else

min_rd(7 downto 4) <= min_rd(7 downto 4) + "1";

end if;

else

min_rd(3 downto 0) <= min_rd(3 downto 0) + "1";

end if;

else if (change_2 = '0' and cmd = '1') then

if min_rd(3 downto 0) <= 0 then

min_rd(3 downto 0) <= "1001";

if min_rd(7 downto 4) <= 0 then

min_rd(7 downto 4) <= "0101";

else

min_rd(7 downto 4) <= min_rd(7 downto 4) - "1";

end if;

else

min_rd(3 downto 0) <= min_rd(3 downto 0) - "1";

end if;

else if (change_1 = '0' and chd = '1') then

if (hour_rd(7 downto 4) = 2 and hour_rd(3 downto 0) = 3 ) then

hour_rd <= "00000000";

else

if(hour_rd(3 downto 0) >= 9)then

hour_rd(3 downto 0) <= "0000";

hour_rd(7 downto 4) <= hour_rd(7 downto 4) + "1";

else

hour_rd(3 downto 0) <= hour_rd(3 downto 0) + "1";

end if;

end if;

else if (change_2 = '0' and chd = '1') then

if (hour_rd(7 downto 4) = 0 and hour_rd(3 downto 0) = 0 ) then

hour_rd <= "00100011";

else

if(hour_rd(3 downto 0) <= 0 and hour_rd(7 downto 4) < 2)then

hour_rd(3 downto 0) <= "1001";

hour_rd(7 downto 4) <= hour_rd(7 downto 4) - "1";

else

hour_rd(3 downto 0) <= hour_rd(3 downto 0) - "1";

end if;

end if;

else if (change_1 = '0' and csd = '1') then

if sec_rd(3 downto 0) >= 9 then

sec_rd(3 downto 0) <= "0000";

if sec_rd(7 downto 4) >= 5 then

sec_rd(7 downto 4) <= "0000";

else

sec_rd(7 downto 4) <= sec_rd(7 downto 4) + "1";

end if;

else

sec_rd(3 downto 0) <= sec_rd(3 downto 0) + "1";

end if;

else if (change_2 = '0' and csd = '1') then

if sec_rd(3 downto 0) <= 0 then

sec_rd(3 downto 0) <= "1001";

if sec_rd(7 downto 4) <= 0 then

sec_rd(7 downto 4) <= "0101";

else

sec_rd(7 downto 4) <= sec_rd(7 downto 4) - "1";

end if;

else

sec_rd(3 downto 0) <= sec_rd(3 downto 0) - "1";

end if;

else if dsk='0' then

if sec_rd(3 downto 0) <= 0 then

sec_rd(3 downto 0) <= "1001";

if sec_rd(7 downto 4) <= 0 then

sec_rd(7 downto 4) <= "0101";

if min_rd(3 downto 0) <= 0 then

min_rd(3 downto 0) <= "1001";

if min_rd(7 downto 4) <= 0 then

min_rd(7 downto 4) <= "0101";

if hour_rd(7 downto 4) = 0 then

if hour_rd(3 downto 0) = 0 then

hour_rd <= "00100011";

else

hour_rd(3 downto 0) <= hour_rd(3 downto 0) - "1";

end if;

else

if(hour_rd(3 downto 0) <= 0)then

hour_rd(3 downto 0) <= "1001";

hour_rd(7 downto 4) <= hour_rd(7 downto 4) - "1";

else

hour_rd(3 downto 0) <= hour_rd(3 downto 0) - "1";

end if;

end if;

else

min_rd(7 downto 4) <= min_rd(7 downto 4) - "1";

end if;

else

min_rd(3 downto 0) <= min_rd(3 downto 0) - "1";

end if;

else

sec_rd(7 downto 4) <= sec_rd(7 downto 4) - "1";

end if;

else

sec_rd(3 downto 0) <= sec_rd(3 downto 0) - "1";

end if;

end if;

end if;

end if;

end if;

end if;

end if;

end if;

end if;

end if;

end process;

fmo<=fm_1;

process(clk)

begin

if clk'event and clk = '1' then

if(min_r=min_ra and hour_r=hour_ra and sec_r(0)='0' and alarm='0')then

fm_1<=clk_1000Hz;

else if(min_r=min_ra and hour_r=hour_ra and sec_r(0) ='1' and alarm='0' )then

fm_1<=clk_500Hz;

else if ( min_r(7 downto 4 )= 5 and min_r(3 downto 0)= 9 and sec_r(7 downto 4) = 5 and sec_r(0)='1' ) then

fm_1<=clk_1000Hz;

else if ( min_r(7 downto 4 )= 5 and min_r(3 downto 0)= 9 and sec_r(7 downto 4) = 5 and sec_r(0) = '0') then

fm_1<=clk_500Hz;

else if (dsk='0' and min_rd(7 downto 0)="00000000" and hour_r(7 downto 0)="00000000" and sec_rd(7 downto 4)="0" and sec_rd( 0)='1') then

fm_1<=clk_1000Hz;

else if (dsk='0' and min_rd(7 downto 0)="00000000" and hour_r(7 downto 0)="00000000" and sec_rd(7 downto 4)="0" and sec_rd(0)='0') then

fm_1<=clk_500Hz;

else

fm_1<='1';

end if;

end if;

end if;

end if;

end if;

end if;

end if;

end process;

end rt1;

4.顶层显示模块

显示数码管,源代码如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity disp is

port

(

rst,clk : in std_logic;

k,set,alarm,ds,dsk : in std_logic;

change_1,change_2 : in std_logic;

fm : out std_logic;

dig,Y : out std_logic_vector(7 downto 0)

);

end disp;

architecture rt1 of disp is

signal min,hour,sec :std_logic_vector(7 downto 0);

signal clkout,fmo :std_logic;

signal scan_cnt :std_logic_vector(2 downto 0);

signal A :std_logic_vector(3 downto 0);

signal dig_r,Y_r :std_logic_vector(7 downto 0);

component adjust

port

(

rst,clk,k,set,alarm,ds,dsk : in std_logic;

change_1,change_2 : in std_logic;

fmo : out std_logic;

sec,min,hour : out std_logic_vector(7 downto 0)

);

end component;

begin

U2:adjust port map(rst,clk,k,set,alarm,ds,dsk,change_1,change_2,fmo,sec,min,hour);

process(clk,rst)

variable cnt :integer range 0 to 50000000;

begin

if clk'event and clk = '1' then

if rst = '0' then

cnt := 0;

else

if cnt = 99999 then

cnt := 0;

else

cnt := cnt + 1;

if cnt = 49999 then

clkout <= '1';

else

clkout <= '0';

end if;

end if;

end if;

end if;

end process;

process(clkout,rst)

begin

if clkout'event and clkout = '1' then

if rst = '0' then

scan_cnt <= "000";

else

scan_cnt <= scan_cnt + '1';

end if;

end if;

end process;

fm <= fmo;

dig <= dig_r;

Y <= Y_r;

process(scan_cnt,sec,min,hour)

begin

case (scan_cnt) is

when "000" => dig_r <= "11111110"; A <= sec(3 downto 0);

when "001" => dig_r <= "11111101"; A <= sec(7 downto 4);

when "010" => dig_r <= "11110111"; A <= min(3 downto 0);

when "011" => dig_r <= "11101111"; A <= min(7 downto 4);

when "100" => dig_r <= "10111111"; A <= hour(3 downto 0);

when "101" => dig_r <= "01111111"; A <= hour(7 downto 4);

when "110" => dig_r <= "11111011"; A <= "1010";

when "111" => dig_r <= "11011111"; A <= "1011";

when others => dig_r <= "11111111"; A <= "0000";

end case;

end process;

process(A)

begin

case (A) is

when "0000" => Y_r <= "11000000";--0

when "0001" => Y_r <= "11111001";--1

when "0010" => Y_r <= "10100100";--2

when "0011" => Y_r <= "10110000";--3

when "0100" => Y_r <= "10011001";--4

when "0101" => Y_r <= "10010010";--5

when "0110" => Y_r <= "10000010";--6

when "0111" => Y_r <= "11111000";--7

when "1000" => Y_r <= "10000000";--8

when "1001" => Y_r <= "10010000";--9

when "1010" => Y_r <= "10111111";---

when "1011" => Y_r <= "10111111";---

when "1100" => Y_r <= "10100110";--c

when "1101" => Y_r <= "10100001";--d

when "1110" => Y_r <= "10000110";--e

when "1111" => Y_r <= "10001110";--f

end case;

end process;

end rt1;

-

电子秒表课程设计报告

电子秒表1设计课题任务及指标1通过本设计的选题方案论证设计计算安装调试资料整理撰写设计报告等环节初步掌握电子工程设计方法和组织实施…

-

电子秒表课程设计

武汉理工大学电工电子综合课程设计说明书摘要基于数字电子技术基础模拟电子技术基础和电路原理有关知识对电子秒表电路进行设计和制作该电子…

-

电子秒表课程设计报告

课程设计综合实验报告20xx20xx年度第一学期名称数字电路实验题目电子秒表设计院系电气与电子工程学院班级通信XXXX班学号XXX…

-

微机原理课程设计报告(电子秒表)

微机原理课程设计报告一设计目的培养和锻炼在学习完本门课后综合应用所学理论知识解决实际工程设计和应用问题的能力通过课程设计要求熟悉和…

-

电子秒表课程设计报告

电子信息工程专业10级学生单片机原理课程设计任务书电子秒表的设计一设计要求设计一个电子秒表与通用秒表功能类似有启动暂停复位等键计时…

-

小学食堂工作总结

晏明小学20xx——20xx学年度第二学期食堂工作总结遵照县卫生监督局、教育局、教办有关学校卫生工作的要求,认真贯彻执行食品卫生法…

-

教师“一帮一”活动总结

“一帮一”工作总结南阳中学成志荣随着课改的不断深入和全面展开,广大教师提高实施新课程、驾驭新课程能力的愿望更加强烈。对发展中的教师…

-

20xx年120急救中心年终总结

20xx年120急救中心年终总结与20xx年计划120急救中心在院领导的大力支持下、各兄弟科室的配合以及我中心全体工作人员的共同努…

-

陈凌宇+本年度个人工作总结

个人年度工作总结岁月荏苒,光阴如梭,弹指之间,20xx年已接近尾声,一年的工作转瞬又将成为历史,在忙碌中我们匆匆地送走了20xx,…

-

实验总结报告

实验报告专业:______姓名:______学号:______日期:______桌号:______________课程名称:模拟电…