实验报告---基本运算器实验-冯剑飞

中国矿业大学计算机学院实验报告

第二篇:运算器实验实验报告

八位运算器实验分析

1,运算器是计算机中的数据处理部件,其组成部件总体来说是:算术逻辑运算单元ALU、多路选通器、累加器ACC、通用寄存器和专用寄存器。运算器可读取内存单元的数据,对其进行运算,并将结果写入内存单元;还可向内存发出访问内存的有效地址。

在完成八位运算器实验时,利用VHDL语言将八位运算器的所有计算功能编写入一个程序,使其可以完成逻辑和算术运算的各种功能。

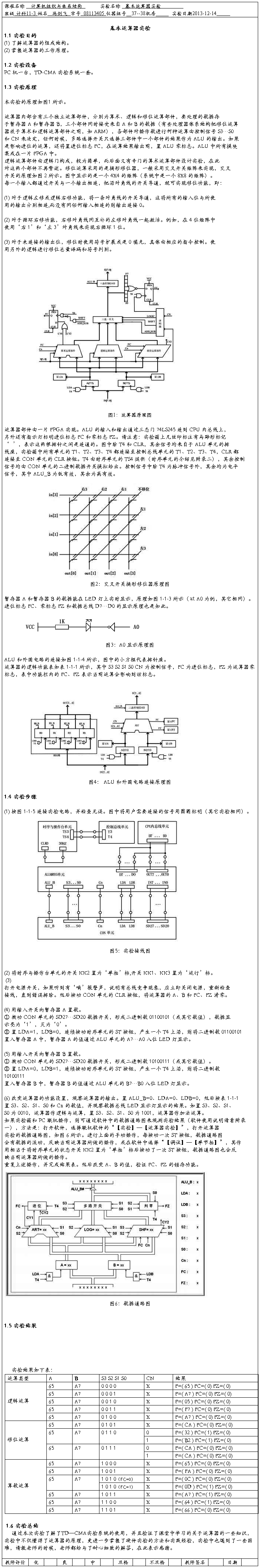

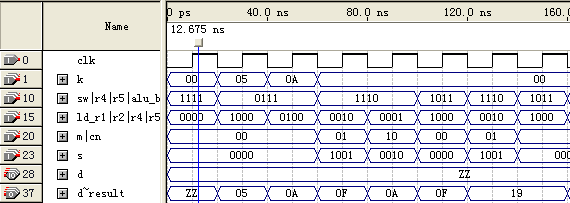

2,八位运算器的实验原理框图

3,VHDL代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity exp_r_alu is

port( clk: in std_logic;

sw_bus,r4_bus,r5_bus,alu_bus:in std_logic;

lddr1,lddr2,ldr4,ldr5: in std_logic;

m,cn: in std_logic;

s: in std_logic_vector(3 downto 0);

k: in std_logic_vector(7 downto 0);

d: inout std_logic_vector(7 downto 0));

end exp_r_alu ;

architecture rtl of exp_r_alu is

signal dr1,dr2,r4,r5,aluout,bus_reg:std_logic_vector(7 downto 0);

signal sel:std_logic_vector(5 downto 0);

begin

ldreg:process(clk,lddr1,lddr2,ldr4,ldr5,bus_reg)

begin

if clk'event and clk='1' then

if lddr1='1' then dr1<=bus_reg;

elsif lddr2='1'then dr2<=bus_reg;

elsif ldr4='1' then r4<=bus_reg;

elsif ldr5='1' then r5<=bus_reg;

end if;

end if;

end process;

alu:process(m,cn,dr1,dr2,sel,aluout)

begin

sel<=m&cn&s;

case sel is

when "000000"=>aluout<=dr1+1;

when "010000"=>aluout<=dr1;

when "100000"=>aluout<=not dr1;

when "000001"=>aluout<=(dr1 or dr2)+1;

when "010001"=>aluout<=dr1 or dr2;

when "100001"=>aluout<=not(dr1 or dr2);

when "000010"=>aluout<=( dr1 or (not dr2))+1;

when "010010"=>aluout<=dr1 or (not dr2);

when "100010"=>aluout<=(not dr1) and dr2;

when "000011"=>aluout<=x"00";

when "010011"=>aluout<=aluout-1;

when "100011"=>aluout<=x"00";

when "000100"=>aluout<=dr1+(dr1 and(not dr2))+1;

when "010100"=>aluout<=dr1+(dr1 and(not dr2));

when "100100"=>aluout<=not(dr1 and dr2);

when "000101"=>aluout<=(dr1 or dr2)or(dr1 and dr2)or x"01";

when "010101"=>aluout<=(dr1 or dr2)+(dr1 and(not dr2));

when "100101"=>aluout<=not dr2;

when "000110"=>aluout<=dr1- dr2;

when "010110"=>aluout<=dr1-dr2-1;

when "100110"=>aluout<=dr1 xor dr2;

when "000111"=>aluout<=dr1 and(not dr2);

when "010111"=>aluout<=(dr1 and(not dr2))-1;

when "100111"=>aluout<=dr1 and(not dr2);

when "001000"=>aluout<=dr1+(dr1 and dr2)+1;

when "011000"=>aluout<=dr1+(dr1 and dr2);

when "101000"=>aluout<=(not dr1)or dr2;

when "001001"=>aluout<=dr1+dr2+1;

when "011001"=>aluout<=dr1 + dr2;

when "101001"=>aluout<=dr1 xnor dr2;

when "001010"=>aluout<=(dr1 or(not dr2))+(dr1 and dr2)+1;

when "011010"=>aluout<=(dr1 or(not dr2))+(dr1 and dr2);

when "101010"=>aluout<=dr2;

when "001011"=>aluout<=dr1 and dr2;

when "011011"=>aluout<=(dr1 and dr2)-1;

when "101011"=>aluout<=dr1 and dr2;

when "001100"=>aluout<=dr1 +dr1+1;

when "011100"=>aluout<=dr1 or dr1;

when "101100"=>aluout<=x"01";

when "001101"=>aluout<=(dr1 or dr2)+dr1+1;

when "011101"=>aluout<=(dr1 or dr2)+dr1;

when "101101"=>aluout<=dr1 or(not dr2);

when "001110"=>aluout<=(dr1 or(not dr2))+dr1+1;

when "011110"=>aluout<=(dr1 or(not dr2))+dr1;

when "101110"=>aluout<=dr1 or dr2;

when "001111"=>aluout<=dr1;

when "011111"=>aluout<=dr1-1;

when "101111"=>aluout<=dr1;

when others =>aluout<=x"ff";

end case;

end process;

bus_reg<=k when(sw_bus='0' and r4_bus='1' and r5_bus='1' and alu_bus='1')else

r4 when(sw_bus='1' and r4_bus='0' and r5_bus='1' and alu_bus='1')else

r5 when(sw_bus='1' and r4_bus='1' and r5_bus='0' and alu_bus='1')else

aluout when(sw_bus='1' and r4_bus='1' and r5_bus='1' and alu_bus='0')else

d;

d<=bus_reg when (sw_bus='0' or r4_bus='0' or r5_bus='0' or alu_bus='0')else

(others=>'Z');

end rtl;

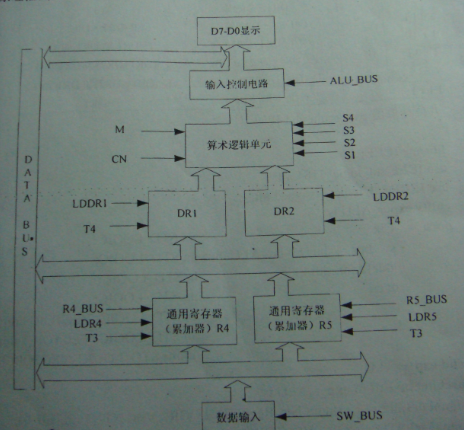

4,实验波形

其中end time 是1微秒,grid size是10纳秒

5,波形分析

k为输入端,操作员可将值输入到运算器。sw_bus置零有效,有效时将k输入的值存入寄存器。r4_bus 、r5_bus、 alu_bus均是置零有效,当其有效时分别将其值存入到寄存器。当r4_bus 、r5_bus、 alu_bus和sw_bus中有任意一个为0时,寄存器的所存储的值即可由d,d~result输出。ld_r1,ld_r2,ld_r4,ld_r5为四个寄存器,分别存储Dr1,Dr2,r4和r5的值,置一有效,例如:当其值为1000时即表示输出Dr1的值。m|cn以及s[3]是表示八位运算器的运算符号的指令码。

具体波形分析如下:(以20纳秒为单位)

①总线开关关闭,输出显示为ZZ

②输入05,由于打开了总线开关以及r1寄存器,于是在d~result输出r1的值。

③输入0A,由于打开了总线开关以及r2寄存器,于是在d~result输出r2的值。

④打开alu_bus以及r4寄存器,执行A加B指令,并将其结果显示在输出上。

⑤打开alu_bus以及r5寄存器,执行(/A)^B指令,并将其结果显示在输出上。

⑥打开r4_bus和r1寄存器,将r4的值存入到r1寄存器中,并显示到输出上。

⑦打开alu_bus和r4寄存器执行加的运算指令,完成整个复合运算,输出结果。

- 基本运算器实验报告

- 实验报告---基本运算器实验-冯剑飞

-

《计算机组成原理》运算器实验报告

《计算机组成原理》实验报告学院:专业:班级学号:AP0804114学生姓名:实验日期:指导老师:成绩评定:五邑大学信息学院计算机组…

-

基本运算器实验

湖南师范大学职业技术学院工学院实验数据报告单实验课程计算机组成原理实验题目基本运算器实验实验日期20xx年5月21日一实验目的1了…

- 计算机组成原理-实验5 基本运算器实验 实验报告

-

《计算机组成原理》运算器实验报告

《计算机组成原理》实验报告学院:专业:班级学号:AP0804114学生姓名:实验日期:指导老师:成绩评定:五邑大学信息学院计算机组…

-

组成原理实验报告(运算器、通用寄存器、移位寄存器)

西安财经学院信息学院实验报告实验名称运算器实验通用寄存器实验移位寄存器实验实验室实验楼418实验日期20xx112920xx122…

- 基本运算器实验报告

-

华中科技大学 组成原理实验报告 运算器组成实验

课程实验报告课程名称计算机组成原理专业班级学号U20xx14669姓名蒋志斌同组成员张源信报告日期计算机科学与技术学院目录一实验名…

-

组成原理实验报告1 基本运算器

计算机组织与体系结构实验报告120xx1219姓名学号班级课题基本运算器1实验目的1了解运算器的组成结构2掌握运算器的工作原理2实…

-

组成原理实验报告

计算机组成理实验报告院系计算机科学与技术专业计算机科学与工程班级计科111学号090511101姓名指导教师谢从华设计地点N620…