电子科技大学集成电路实验报告——版图部分实验报告

微电子与集成电路设计

实验报告

使用L-Edit编辑单元电路布局图

一、实验学时:4学时

二、实验目的

1、熟悉版图设计工具L-Edit的使用环境;

2、掌握L-Edit的使用技巧。

三、实验内容:利用L-Edit绘制一个反相器的版图,并利用提取工具将反相器布局图转化为T-Spice 文件。

四、实验结果:

1、本次版图设计中的设计技术参数、格点设定、图层设定、设计规则采用的是( C:\TannerLb\LEdit\TECH\mosis\morbn20.tdb)文件的。

其设计规则主要有:

2、绘制一个L=2u,W由学号确定的PMOS管掩膜版图。

先确定W。W等于学号的最后一位乘以2,若学号最后一位£4,则先加10后再乘以2。所以,要绘制的是一个L=2u,W=( 16 u)的PMOS管掩膜版图。

(当时我没注意要按学号画,是按指导书上画的,截完图会来看报告才发现)

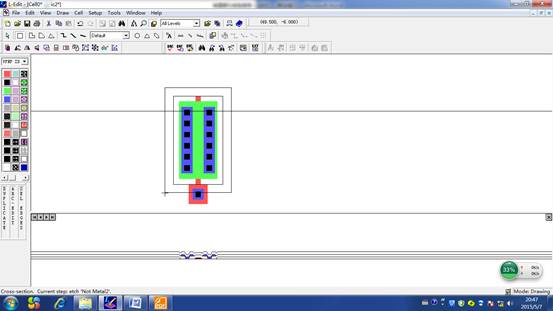

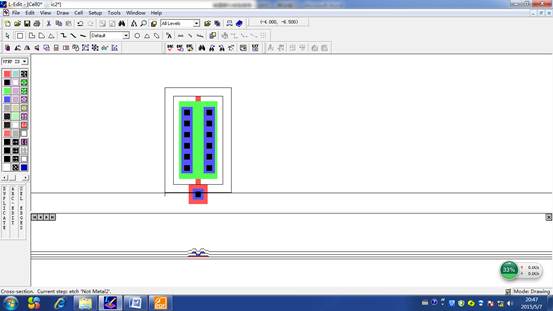

所完成的经DRC检查无错误的PMOS版图为:

该PMOS管的截面图为:

3、绘制一个L、W和上面的PMOS管相同的NMOS管掩膜版图。

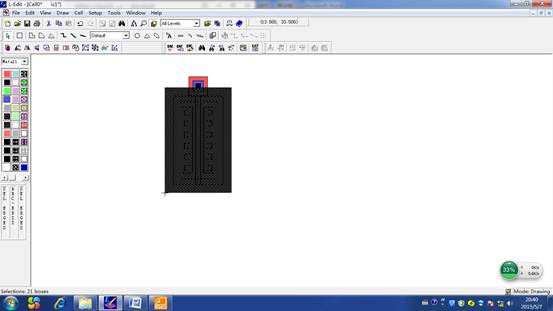

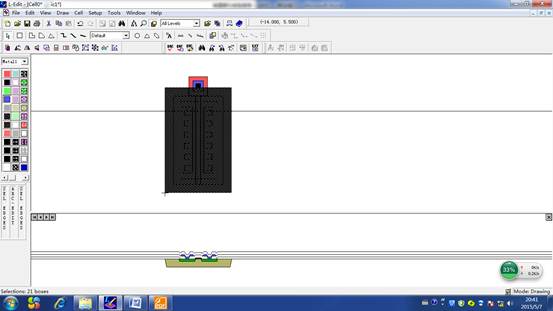

所完成的经DRC检查无错误的NMOS版图为:

该NMOS管的截面图为:

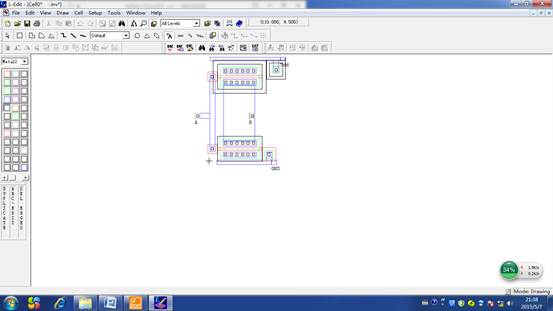

4、运用前面绘制好的nmos 组件与pmos 组件绘制反相器inv的版图。加入电源Vdd,地Gnd,输入A和输出B的标号。所完成的DRC检查无错误的版图为:

5、将反相器布局图转化为T-Spice 文件,该文件的内容为:

五、实验总结与体会:

进行任何实验时对实验原理的的掌握都是最重要的。由于实验前的准备不足,实验时遇到了很多的困难,需要好好复习MOS工艺的的基本知识。在进行版图设计时,需要严格遵循设计规则中对参数、位置的要求,任何的偏差都可能导致错误。所以每进行一步都要进行检查,修正;但有些错误可以在后续的步骤中自动解决,也需要加以注意。

第二篇:电子科技大学模拟集成电路实验报告

CMOS模拟集成电路设计

实验报告

一、工艺和设计要求

用0.18?m CMOS工艺完成一下设计:

仿真获得PMOS和NMOS的工艺参数 Kp,??,???,???,λp,??

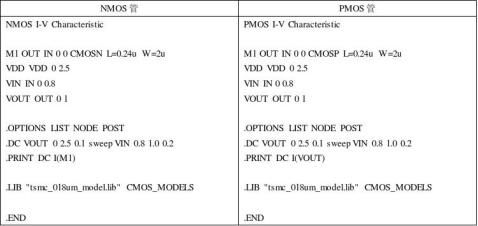

二、Hspice 编程

三、仿真结果

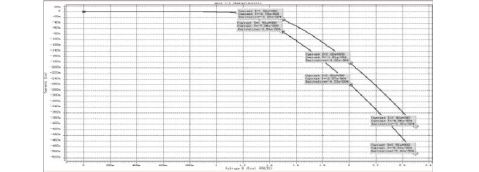

NMOS管仿真截图:

仿真结果:

PMOS管

仿真结果:

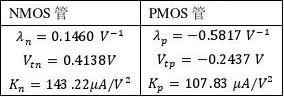

四、参数计算

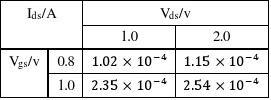

NMOS管

1???((???????)2(1+?????) 2??

12??)(0.8?????)2(1+??×1?) 1.02×10?4?=??(20.24???IDSn=

1.15×10?4?=12??)(0.8?????)2(1+??×2?) ??(20.24???

???=0.1460 ??1

12??)(0.8?????)2(1+??×1?) 1.02×10?4?=??(20.24???

12???4()(1?????)2(1+??×1?) 2.35×10?=??20.24???

????=0.4138?

??=143.22??/?2

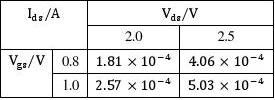

PMOS管

1?2|IDSp|=??((|???|?|???|)(1+??|???|) 2??

12??2(0.8??|???|)(1+??×2?) 1.81×10?4?=??(20.24???

12??2)(0.8??|???|)(1+??×2.5?) 4.06×10?4?=??(20.24???

???=?0.5817 ??1

12??2?4((0.8??|???|)(1+??×2?) 1.81×10?=??20.24???

2.57×10?4?=12??2)(1??|???|)(1+??×2?) ??(20.24???

????=?0.2437 ?

??=107.83 ??/?2

五、结论和分析

TSMC 0.18um实测工艺参数

NMOS场效应管参数处于正常范围内,出于未知原因PMOS场效应管的参数不太正常。仿真的时候没有在意,写报告的时候才发现PMOS管的输出特性曲线的走势似乎有些不正常。

正常情况下,??与??应当大致相同,???与???应当大致相同。在宽长比相同的情况下,由于电子的迁移率大约是空穴的两倍,??大致是??的两倍。

-

电路实验报告

动态电路的研究一、实验目的及要求:①认识和了解双踪示波器、信号发生器的基本功能和使用方法;②学习使用示波器和信号发生器进行电路实验…

- 南京理工大学电路实验报告超详细版

-

中国石油大学(华东)20xx年春三相交流电路实验报告

中国石油大学华东现代远程教育实验报告课程名称电工电子学实验名称三相交流电路实验形式在线模拟现场实践学生姓名号年级专业层次网络14春…

-

东南大学模拟电路实验报告(三)

东南大学电工电子实验中心实验报告课程名称:电子电路实践第三次实验实验名称:单极低频放大电路(基础)院(系):电气工程专业:电气工程…

- 武汉大学单级放大电路实验报告

-

集成电路设计实验报告

西安科技大学集成电路设计综合实验报告集成电路设计实验报告1学院电控学院班级微电0901姓名学号0906090123西安科技大学集成…

-

集成电路综合设计实验报告

集成电路设计综合实验报告学院电控学院班级微电子1001班姓名xxx学号xxxxxxxxxx一实验目的1培养从版图提取电路的能力2学…

-

集成电路-CAD设计报告

南通大学电子信息学院实验报告册课程名称班级姓名学号学年第一目的和要求课程设计是教学中的一个重要环节对学生来说是一次工程技术工作的锻…

-

集成电路版图设计报告

集成电路版图设计报告集成电路版图设计报告一设计目的1通过本次实验熟悉Ledit软件的特点并掌握使用Ledit软件的流程和设计方法2…

-

集成电路版图设计报告

黑龙江大学电子工程学院实验报告课程名称集成电路版图设计专业集成电路设计与集成系统班级学号学生姓名年月日实验名称集成电路版图设计一实…

-

大连海事大学数字逻辑电路课程设计实验总结报告

数字逻辑电路课程设计实验总结报告题目一:用J-K触发器设计13进制加法计数器一、设计过程:参见设计实验报告(真值表,卡诺图)。二、…