数字系统设计综合实验报告

数字系统设计综合实验报告

实验名称:1、加法器设计

2、编码器设计

3、译码器设计

4、数据选择器设计

5、计数器设计

6、累加器设计

7、交通灯控制器设计

班级:

姓名:

学号:

指导老师:

实验1 加法器设计

1) 实验目的

(1) 复习加法器的分类及工作原理。

(2) 掌握用图形法设计半加器的方法。

(3) 掌握用元件例化法设计全加器的方法。

(4) 掌握用元件例化法设计多位加法器的方法。

(5) 掌握用Verilog HDL语言设计多位加法器的方法。

(6) 学习运用波形仿真验证程序的正确性。

(7) 学习定时分析工具的使用方法。

2) 实验原理

加法器是能够实现二进制加法运算的电路,是构成计算机中算术运算电路的基本单元。目前,在数字计算机中,无论加、减、乘、除法运算,都是化为若干步加法运算来完成的。加法器可分为1位加法器和多位加法器两大类。1位加法器有可分为半加器和全加器两种,多位加法器可分为串行进位加法器和超前进位加法器两种。

(1)半加器

如果不考虑来自低位的进位而将两个1位二进制数相加,称半加。实现半加运算的电路则称为半加器。若设A和B是两个1位的加数,S是两者相加的和,C是向高位的进位。则由二进制加法运算规则可以得到。

(2)全加器

在将两个1位二进制数相加时,除了最低位以外,每一位都应该考虑来自低位的进位,即将两个对应位的加数和来自低位的进位三个数相加,这种运算称全加。实现全加运算的电路则称为全加器。

若设A、B、CI分别是两个1位的加数、来自低位的进位,S是相加的和,C是向高位的进位。则由二进制加法运算规则可以得到:

3) 实验内容及步骤

(1) 用图形法设计半加器,仿真设计结果。

(2) 用原件例化的方法设计全加器,仿真设计结果

(3) 用原件例化的方法设计一个4为二进制加法器,仿真设计结果,进行定时分析。

(4) 用Verilog HDL语言设计一个4为二进制加法器,仿真设计结果,进行定时分析。

(5) 分别下载用上述两种方法设计4为加法器,并进行在线测试。

4)设计

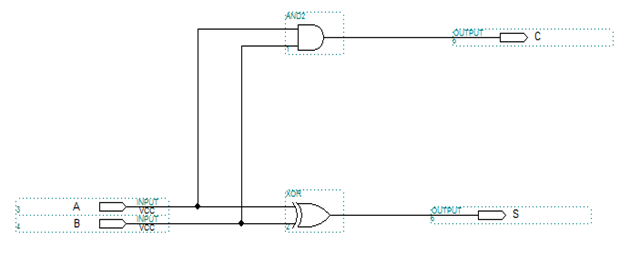

1)用图形法设计的半加器,如下图1所示,由其生成的符号如图2所示。

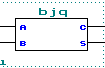

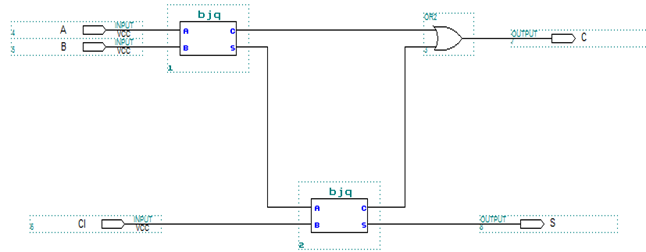

2)用元件例化的方法设计的全加器如图3所示,由其生成的符号如图4所示。

图三:

图四:

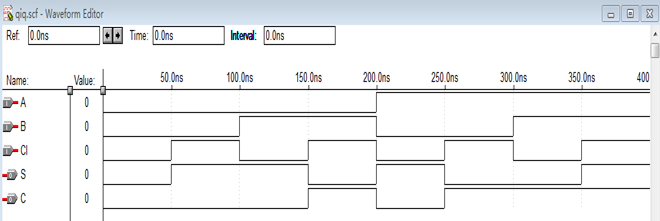

5)全加器时序仿真波形如图下图所示

6)心得体会:

第一次做数字系统设计实验,老师给我们讲了用图形法设计的全过程。在这次过程中,我进一步加强对理论知识的学习,将理论与实践结合起来。实验过程中遇到了一个小问题是生成半加器符号,后来发现缺了File/Create Default这一步。通过这一次的失误,我明白了做事要认真!最后将实验做出来了,体味了成功的喜悦!通过这次实验我复习了加法器的分类及工作原理,

并掌握了用图形法设计半加器的方法,掌握了用元件例化法设计全加器的方法,掌握了用元件例化法设计多位加法器的方法,掌握了用Verilog HDL语言设计多位加法器的方法,学习了运用波形仿真验证程序的正确性,学习定时分析工具的使用方法。

实验2 编码器设计

1) 实验目的

(1) 复习编码器的构成及工作原理。

(2) 掌握用Verilog HDL语言设计编码器的方法。

(3) 掌握用图形法设计优先编码器的方法。

(4) 掌握用Verilog HDL语言设计优先编码器的方法。

(5) 进一步学习运用波形仿真验证程序的正确性。

2) 实验原理

编码器(Encoder)的逻辑功能是将输入的每一个高、低电平信号编成一个对应的二进制代码。目前,经常使用的编码器有普通编码器和优先编码器两类。

(1) 普通编码器

在普通编码器中,任何时刻只允许输入一个编码信号,否则输出将发生混乱。图2.2.1是3位二进制编码器框图,它的输入是I0~I7八个高电平信号,输出是3位二进制代码Y2、Y1、Y0,为此,又称为8线-3线编码器。其输出与输入的对应关系如表2.2.1所示。

(2) 优先编码器

在优先编码器(Priority Encoder)中,允许同时输入两个以上的编码信号。不过在设计优先编码器时已将所有的输入信号按优先顺序进行排队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。优先编码器经常用于具有优先级处理的数字系统中,例如,中断管理系统通常用优先编码器实现。8线-3线优先编码器74147的真值表如表2.2.2所示。

3)实验内容及步骤

(1)用Verilog HDL语言设计8线——3线普通编码器,仿真设计结果。

(2)用图形法设计实现74148功能的优先编码器,仿真设计结果,进行定时分析。

(3)用Verilog HDL语言设计8线——3线优先编码器,仿真设计结果,进行定时分析。

(4)分别下载用上述两种方法所设计的优先编码器,并进行在线测试。

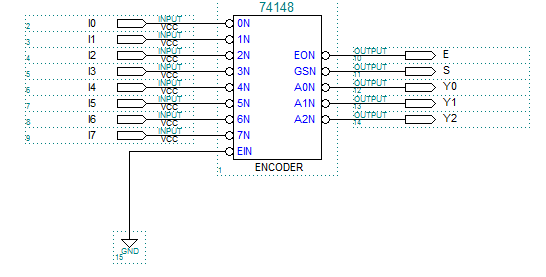

2)用图形法设计的优先编码器74148原理图如下:

4)优化编码器功能仿真波形如下图:

5)心得体会:

这一次做数电学过的优先编码器,感觉还是很轻松的。在实验过程中没怎么遇到太大的问题,感觉就是速度慢了一点,说明平时训练的少,所以我就想平时还需多练习,在确保正确的前提下,再提高速度!通过这次实验我复习编码器的构成及工作原理,掌握了用Verilog HDL语言设计编码器的方法,掌握了用图形法设计优先编码器的方法,掌握了用Verilog HDL语言设计优先编码器的方法,进一步学习运用波形仿真验证程序的正确性。

实验3 译码器设计

1) 实验目的

(1) 复习二进制译码器及显示译码器的构成及工作原理。

(2) 掌握用Verilog HDL语言设计二进制译码器的方法。

(3) 掌握用Verilog HDL语言设计显示译码器的方法。

(4) 进一步学习运用波形仿真验证程序的正确性。

2) 实验原理

译码器是数字系统中常用的组合逻辑电路,其逻辑功能是将每个输入的二进制代码译成对应的高、低电平信号并输出。译码是编码的反操作。常用的译码器电路有二进制译码器、二-十进制译码器和显示译码器三类。

(1)3线-8线译码器是二进制译码器的一种。其输入为一组3位二进制代码,而输出则是一路高、低电平信号。图2.3.1是3线-8线译码器74138的逻辑框图。其中,A2、A1、A0为3位二进制代码输入端,Y0’~Y7’是8个输出端,S1、S2’、S3’为3个输入控制端。它们之间的关系如表2.3.1所示。

(2)七段数码显示译码器

为了能以十进制数码直观地显示数字系统的运行数据,目前广泛使用七段数码显示译码器来显示字符,因这种字符显示器由七段可发光的线段拼合而成,又称为七段数码管。

半导体数码管的每条线段都是一个发光二极管。如果七个发光二极管的公共端是阴极并且接在一起,则称为共阴极数码管,反之,称为共阳极数码管。

半导体数码管可以用TTL或CMOS集成电路直接驱动。为此,就需要使用显示译码器将BCD代码译成数码管所需要的驱动信号,以便数码管以十进制数字显示出BCD代码所表示的数值。如图2.3.2所示。

3)实验内容及步骤

(1)用Verilog HDL语言设计3线——8线译码器,仿真设计结果。

(2)用Verilog HDL语言设计七段数码显示译码器,仿真设计结果,进行定时分析。

(3)下载七段数码显示译码器,并进行在线测试。

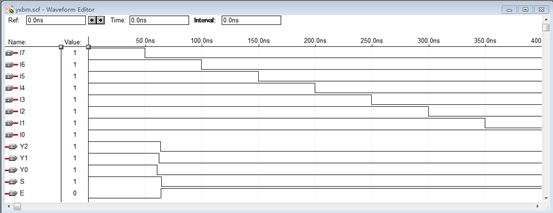

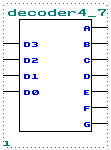

用Verilog HDL语言设计的七段数码显示译码器程序decoder4_7如下:

module decoder4_7(a,b,c,d,e,f,g,D3,D2,D1,D0);

output a,b,c,d,e,f,g;

input D3,D2,D1,D0;

reg a,b,c,d,e,f,g;

always @(D3 or D2 or D1 or D0)

begin

case({D3,D2,D1,D0})

0:{a,b,c,d,e,f,g}=7'b1111110;1:{a,b,c,d,e,f,g}=7'b0110000;

2:{a,b,c,d,e,f,g}=7'b1101101;3:{a,b,c,d,e,f,g}=7'b1111001;

4:{a,b,c,d,e,f,g}=7'b0110011;5:{a,b,c,d,e,f,g}=7'b1011011;

6:{a,b,c,d,e,f,g}=7'b1011111;7:{a,b,c,d,e,f,g}=7'b1110000;

8:{a,b,c,d,e,f,g}=7'b1111111;9:{a,b,c,d,e,f,g}=7'b1111011;

default:{a,b,c,d,e,f,g}=7'bx;

endcase

end

endmodule

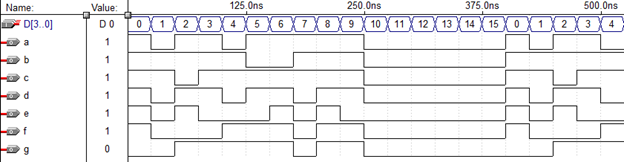

3)七段数码显示译码器的功能仿真波形如下图:

4)心得体会:

这次老师教了我们新的一种数字系统设计方式,用Verilog HDL语言来设计,刚开始有一点生疏,经过和同学们交流讨论下,顺利的完成了实验。实验过程中遇到了一些问题:输入代码时,出现漏字母,没区分大小写等等。实验效率和实验水平还待在平时加强练习,总结反思。通过这次实验我复习了二进制译码器及显示译码器的构成及工作原理,掌握了用Verilog HDL语言设计二进制译码器的方法,掌握了用Verilog HDL语言设计显示译码器的方法,进一步学习运用波形仿真验证程序的正确性。

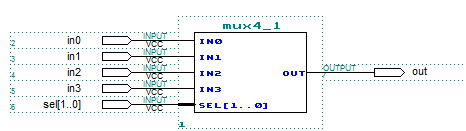

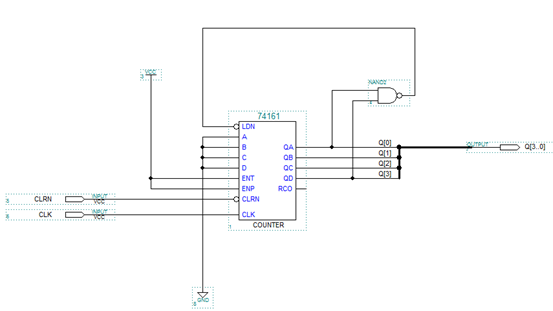

实验4 数据选择器设计

1) 实验目的

(1) 复习数据选择器的构成及工作原理。

(2) 掌握用Verilog HDL语言设计数据选择器的方法。

(3) 进一步加深对仿真结果和仿真过程的理解。

2) 实验原理

数据选择器又叫多路开关,简称MUX(Multiplexer).数据选择器的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号,数据选择器原理示意图如图2.4.1所示。常用的数据选择器有双四选一数据选择器74153、八选一数据选择器74151。其中,74151的逻辑图如图2.4.2所示,其真值表如表2.4.1所示。

3)实验内容及步骤

(1) 用Verilog HDL语言设计四选一数据选择器,仿真设计结果。

(2) 用Verilog HDL语言设计实现74151功能的数据选择器,仿真设计结果。

(3)下载74151数据选择器,并进行在线测试。

module mux4_1(out,in0,in1,in2,in3,sel);

output out;input in0,in1,in2,in3;

input[1:0] sel;

reg out;

always @(in0 or in1 or in2 or in3 or sel)

begin

if(sel==2'b00) out=in0;

else if(sel==2'b01) out=in1;

else if(sel==2'b10) out=in2;

else out=in3;

end

Endmodule

3)四选一数据选择器的功能仿真波形如下图:

4)心得体会:

这次实验,我是在上课之前做好的,心里还是很有把握的!输入的代码经软件检查都没有问题,只是在实验过程中有一个问题没有解决,就是在做仿真图形时,sel的输入波形不会输入,经过自己看书解决了这个问题,就是在做图形仿真界面选时钟周期赋值,并将value赋予B11。通过这次实验我感到无比的自豪,也对这实验有了点自信!通过这次实验我复习了数据选择器的构成及工作原理,掌握了用Verilog HDL语言设计数据选择器的方法,进一步加深对仿真结果和仿真过程的理解。

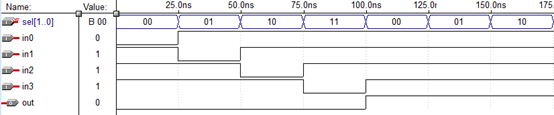

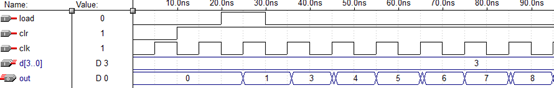

实验5 计数器设计

一、 实验目的:

1、 复习计数器的构成及工作原理;

2、 掌握用Verilog HDL 语言设计计数器的方法;

3、 掌握用图形法设计计数器的方法;

4、 进一步掌握时序逻辑电路的仿真方法。

二、 实验原理:

计数器是数字系统中使用最多的时序电路。计数器最常见的用途是能对时钟脉冲进行计数。按计数器的计数容量来分类,计数器可分为二进制计数器、十进制计数器、任意进制的计数器三类,其中,二进制计数器的模值等于2……n(n为触发器个数)。可以用已有固定进制的计数器通过外电路的不同连接方式来构成任意进制的计数器,具体有反馈清零、反馈置数、同步级联(并行连接)、异步连接(串行连接)、整体置零、整体置数等方式。常见的计数器芯片有74160(十进制)、74161(4位二进制)、74192(双时钟可逆十进制)等。

3)实验内容及步骤

(1)用图形法设计一个十进制计数器,仿真设计结果。

(2)用Verilog HDL语言设计一个十进制计数器(要求加法计数;时钟上升沿触发;异步清零,低电平有效;同步置数,高电平有效),并进行仿真验证。

(3)下载所设计的十进制计数器,并进行在线测试。

1)用图形法设计的十进制计数器如下图所示

2)用Verilog HDL语言描述的十进制计数器程序count10.v如下:

module count10(clk,d,clr,load,out);

input clk,clr,load;

input [3:0] d;

output [3:0] out;

reg [3:0] out;

always @(posedge clk or negedge clr)

begin if(! clr)out <=0;

else if(load) out<=d;

else if(out==9) out<=0;

else out<=out+1; end

endmodule

3)十进制计数器的功能仿真波形如下图所示:

4)心得体会:

这次实验没有什么难度,用图形法或Verilog HDL语言做都可以,用图形法做的时候存在了一个小错误,总线用错了,最后在同学的帮助下完成了实验。在提高自己实验效率和实验水平上,我决定在课余之时多练习,以培养自己兴趣,希望自己在实验上更上一层楼!通过这次实验我复习了计数器的构成及工作原理,掌握了用Verilog HDL 语言设计计数器的方法,掌握了用图形法设计计数器的方法,进一步掌握了时序逻辑电路的仿真方法。

实验6 累加器设计

一、 实验目的:

1、 了解累加器的工作原理;

2、 掌握多成次结的设计思路;

3、 掌握综合应用原理图和文本相结合的设计方法。

二、 实验原理:

在运算器中,专门存放算术或逻辑运算的一个操作数和运算结果的寄存器被称为累加器。他能进行加、减、读出、移位、循环移位和求补等操作,是运算器的主要组成部分。累加器的主要功能是对数据进行累加,并可以暂时运算结果。

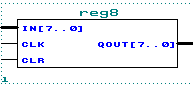

本实验要求设计一个简易的8位累加器ACC,用于对输入的8位数据进行累加。可以把累加器分为两个模块:一个是8位全加器,一个是8位寄存器。全加器负责对不断输入的数据和进位进行累加,寄存器负责暂存累加和,把累加和输出并反馈到累加器输入端,以进行下一次的累加。划分好模块后,再把每个模块的端口和连接关系设计完毕,就可以设计各个功能模块了。

3)实验内容及步骤

(1)用Verilog HDL语言分别设计8位全加器和8位寄存器,生成符号,并分别进行仿真验证。

(2)用图形法设计8位累加器,生成符号,并进行仿真验证。

(3)下载该累加器,并进行在线测试。

(4)设计

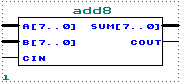

1)用Verilog HDL语言设计的8位加法器add8.v如下图,由其生成的符号如图1所示:

module add8(sum,cout,a,b,cin);

output[7:0] sum;

output cout;

input[7:0] a,b;

input cin;

assign {cout,sum}=a+b+cin;

Endmodule

图一:8位加法器的符号

2)用Verilog HDL语言设计的8位寄存器reg.v如下,由其生成的符号如图2所示:

module reg8(qout,in,clk,clr);

output[7:0] qout;

input[7:0] in;

input clk,clr;

reg[7:0]qout;

always @(posedge clk or posedge clr)

begin if(clr) qout=0;

else qout=in;

end

Endmodule

图二:8位寄存器符号

3)用图形法设计的8位累加器如下图所示

4)8位累加器的功能仿真波形图如下图所示

5)心得体会:

这次实验,我收获非常大。实验过程中我遇到加法器的符号,寄存器符号调不出来,过后经反思发现没有选择File/Creat Default,过后调出符号后,在做累加器顶层模块电路原理图时又发现了问题,原来是在文件夹里有多余的.gdf文件导致对实验结果的干扰!最后仿真的时候,又忘了将In[7..0],OUT[7..0]的Value分别改为D80和D0。通过这次实验我了解了累加器的工作原理,掌握了多成次结的设计思路,掌握了综合应用原理图和文本相结合的设计方法。

实验7交通灯控制器设计

一、 实验目的:

1、 了解交通的控制器的工作原理;

2、 掌握用Verilog HDL 语言设计多进程的方法;

3、 掌握数字系统层次设计方法,学会利用总线表示电路的连接。

二、 实验原理:

1、 交通灯系统要求

1) 在十字路口的A方向和B方向个设计红(R)、黄(Y)、绿(G)、左拐(L)四盏灯。

2) 4盏灯按合理的顺序亮灭,如表所示。

3) A方向是主干路,车流量大,红、绿、黄、左拐灯亮时间分别是:55s、40s、5s、15s。

B方向是次干道,红、绿、黄、左拐灯亮时间分别是:65s、30s、5s、15s。

A方向红灯时间=B方向绿灯时间+B方向黄灯时间*2+B方向左拐时间。

B方向红灯时间=A方向绿灯时间+A方向黄灯时间*2+A方向左拐时间。

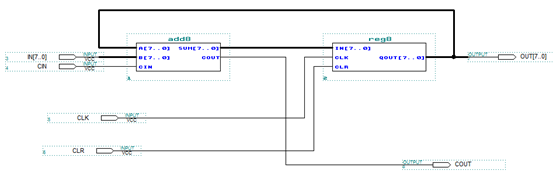

2、 系统总体结构设计

系统总体结构如图所示。包括总控制模块及A、B两方向控制及倒计时模块、显示译码模块。

3)实验内容及步骤

(1)用Verilog HDL语言设计交通灯控制器的控制及倒计时模块,仿真设计结果。

(2)用Verilog HDL语言设计交通灯控制器的显示译码模块,仿真设计结果。

(3)用原理图法设计顶层模块,仿真设计结果。

(4)下载所设计的交通灯控制器,并进行在线测试。

1)用Verilog HDL语言描述的控制模块程序trafficl.v如下

module traffic1(CLK,EN,LAMPA,LAMPB,ACOUNT,BCOUNT);

output[7:0] ACOUNT,BCOUNT;output[3:0] LAMPA,LAMPB;

input CLK,EN;

reg[7:0] numa,numb;reg tempa,tempb;

reg[2:0] counta,countb;

reg[7:0] ared,ayellow,agreen,aleft,bred,byellow,bgreen,bleft;

reg[3:0] LAMPA,LAMPB;

always @(!EN)

begin

ared<=8'd55;ayellow<=8'd5;

agreen<=8'd40;aleft<=8'd15;

bred<=8'd65;byellow<=8'd5;

bgreen<=8'd30;bleft<=8'd15;

end

assign ACOUNT=numa;

assign BCOUNT=numb;

always @(posedge CLK)

begin

if(EN)

begin

if(!tempa)

begin tempa<=1;

case(counta)

0:begin numa<=agreen;LAMPA<=2;counta<=1;end

1:begin numa<=ayellow;LAMPA<=4;counta<=2;end

2:begin numa<=aleft;LAMPA<=1;counta<=3;end

3:begin numa<=ayellow;LAMPA<=4;counta<=4;end

4:begin numa<=ared;LAMPA<=8;counta<=0;end

default:LAMPA<=8;

endcase

end

else

begin

if(numa>1) numa<=numa-1;

if(numa==2) tempa<=0;

end

end

else begin LAMPA<=8;counta<=0;end

end

always @(posedge CLK)

begin if(EN)

begin if(!tempb)

begin tempb<=1;

case(countb)

0:begin numb<=bred;LAMPB<=8;countb<=1;end

1:begin numb<=bgreen;LAMPB<=2;countb<=2;end

2:begin numb<=byellow;LAMPB<=4;countb<=3;end

3:begin numb<=bleft;LAMPB<=1;countb<=4;end

4:begin numb<=byellow;LAMPB<=4;countb<=0;end

default:LAMPB<=8;

endcase

end

else

begin

if(numb>1) numb<=numb-1;

if(numb==2) tempb<=0;

end

end

else begin LAMPB<=8;countb<=0;end

end

endmodule

2)用Verilog HDL语言描述的显示译码模块bcd2.v如下

module bcd2(D7,D6,D5,D4,D3,D2,D1,D0,a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2);

input D7,D6,D5,D4,D3,D2,D1,D0;

output a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2;

reg a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2;

always @(D7 or D6 or D5 or D4 or D3 or D2 or D1 or D0)

begin

case({D7,D6,D5,D4,D3,D2,D1,D0})

8'd0:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111110_1111110;

8'd1:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111110_0110000;

8'd2:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111110_1101101;

8'd3:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111110_1111001;

8'd4:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111110_0110011;

8'd5:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111110_1011011;

8'd6:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111110_1011111;

8'd7:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111110_1110000;

8'd8:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111110_1111111;

8'd9:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111110_1111011;

8'd10:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110000_1111110;

8'd11:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110000_0110000;

8'd12:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110000_1101101;

8'd13:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110000_1111001;

8'd14:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110000_0110011;

8'd15:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110000_1011011;

8'd16:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110000_1011111;

8'd17:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110000_1110000;

8'd18:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110000_1111111;

8'd19:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110000_1111011;

8'd20:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1101101_1111110;

8'd21:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1101101_0110000;

8'd22:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1101101_1101101;

8'd23:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1101101_1111001;

8'd24:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1101101_0110011;

8'd25:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1101101_1011011;

8'd26:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1101101_1011111;

8'd27:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1101101_1110000;

8'd28:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1101101_1111111;

8'd29:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1101101_1111011;

8'd30:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111001_1111110;

8'd31:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111001_0110000;

8'd32:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111001_1101101;

8'd33:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111001_1111001;

8'd34:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111001_0110011;

8'd35:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111001_1011011;

8'd36:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111001_1011111;

8'd37:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111001_1110000;

8'd38:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111001_1111111;

8'd39:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1111001_1111011;

8'd40:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110011_1111110;

8'd41:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110011_0110000;

8'd42:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110011_1101101;

8'd43:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110011_1111001;

8'd44:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110011_0110011;

8'd45:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110011_1011011;

8'd46:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110011_1011111;

8'd47:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110011_1110000;

8'd48:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110011_1111111;

8'd49:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b0110011_1111011;

8'd50:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1011011_1111110;

8'd51:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1011011_0110000;

8'd52:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1011011_1101101;

8'd53:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1011011_1111001;

8'd54:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1011011_0110011;

8'd55:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1011011_1011011;

8'd56:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1011011_1011111;

8'd57:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1011011_1110000;

8'd58:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1011011_1111111;

8'd59:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1011011_1111011;

8'd60:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1011111_1111110;

8'd61:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1011111_0110000;

8'd62:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1011111_1101101;

8'd63:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1011111_1111001;

8'd64:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1011111_0110011;

8'd65:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'b1011111_1011011;

default:{a1,b1,c1,k1,e1,f1,g1,a2,b2,c2,k2,e2,f2,g2}=14'bx;

endcase

end

Endmodule

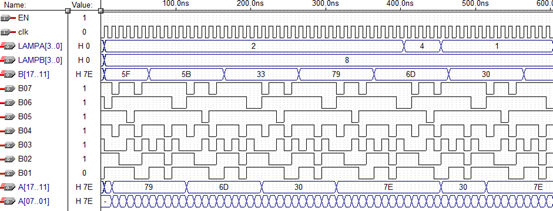

4) 用图形法设计的顶层模块如图5,仿真结果如图6所示

图五:

图六

5)心得体会:

这一次输入代码很多,我还是认真的将代码输入完,综合之前的经验,交通灯实验还是在自己的预料中结束了!通过这次实验我了解了交通的控制器的工作原理,掌握了用Verilog HDL 语言设计多进程的方法,掌握了数字系统层次设计方法,学会了利用总线表示电路的连接。

-

数字系统设计综合实验报告

数字系统设计综合实验报告实验名称1加法器设计2编码器设计3译码器设计4数据选择器设计5计数器设计6累加器设计7交通灯控制器设计班级…

-

东北大学数字系统设计实验报告

数字系统设计实验报告姓名学号计数器设计实验1实验目的1学习计数器不同设计方法2学习掌握VHDL中不同输出类型在具体应用时的区别OU…

-

复杂数字系统设计实验报告

复杂数字系统设计实验报告光学与光学工程系王启星物理学院SA15038040一实验标题多功能数字种的设计二实验目的任务和要求1数字系…

-

PLD与数字系统设计实验报告

PLD与数字系统设计实验报告A组实验四数字密码锁1实验要求使用Xilinx公司的Spartan3S400AN开发板上的相关模块利用…

-

数字系统设计与Verilog HDL实验报告(一)

数字系统设计与VerilogHDL实验报告一班级自动1003班姓名刘洋学号06101103实验一ModelSim认识及四位比较器一…

-

南昌大学数字钟设计实验报告

数字电路与逻辑设计实验实验报告题目学院信息工程学院系电子信息工程专业班级学号学生姓名同组同学指导教师递交日期23页第1页共南昌大学…

-

数电课程实验报告——数字钟的设计

数字电子技术课程设设计题目班级学号学生姓名指导教师时间计报告数字钟的设计20xx年12月27日20xx年1月2日数字电子技术课程设…

-

数字电路设计实验报告

数字电路设计实验报告引言本课程是面向智能车制作的课程但是主要讲述的是一些关于智能车制作的一些最基本的基础知识比如说一些单片机的知识…

-

数字电压表设计实验报告

数字电路课程设计报告课题数字电压表0目录一摘要2二设计任务及要求2三设计总体方案2四单元电路的设计3五调试过程及结果分析6六心得感…

-

电子线路设计课程设计实验报告-多功能数字钟设计

实验报告多功能数字钟设计姓名学号班级一实验目标1掌握可编程逻辑器件的应用开发技术设计输入编译仿真和器件编程2熟悉EDA软件使用3掌…

-

电子系统设计与实习报告

电子系统设计与实习报告实训任务一温度显示系统电路原理图PCB版图绘制一设计目标1完成温度显示系统的设计完成接收处理温度信号和控制八…