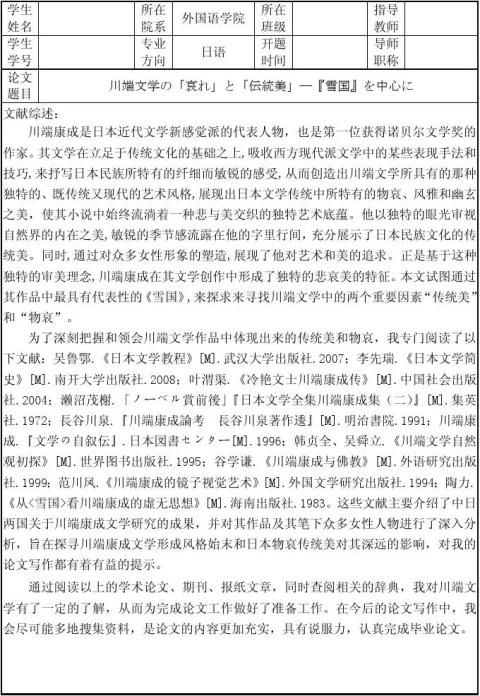

川端文学论文开题报告

学士学位论文(设计)开题报告

注:所有相关表格内的填写内容中文为小四号宋体,日文为MS Mincho小四号 行距1.25

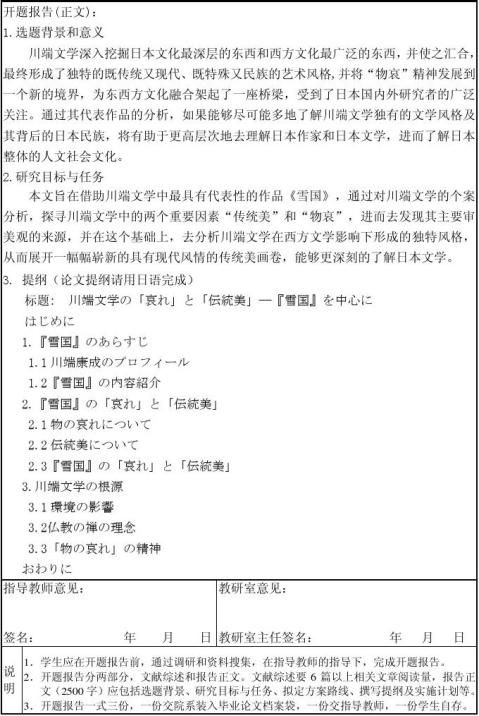

第二篇:博士论文开题报告-文献综述

文 献 综 述

0 引言... 1

1.大规模集成电路的发展以及铜互连工艺的概述... 2

1.1.大规模集成电路的发展概况... 2

1.2.ULSI中铝互连线的发展... 4

1.3.ULSI中铜互连线工艺的提出、发展及存在的问题... 5

1.3.1.铜互连工艺的提出... 5

1.3.2.铜互连技术的主要问题... 8

2.铜互连的扩散阻挡层的发展现状的概述... 10

3.扩散基本理论以及铜互连薄膜中的二维扩散研究的现状... 12

3.1.Fick扩散定律及扩散系数... 13

3.1.1.Fick第二扩散定律... 13

3.1.2.扩散系数的确定及Arrhenius公式... 14

3.2.薄膜扩散理论... 14

3.2.2.单晶薄膜的扩散动力学理论的研究... 15

3.2.3.多晶薄膜扩散动力学理论的研究... 16

3.3.溶质对晶粒间界扩散的影响... 21

3.3.1溶质在高温时增加晶粒间界扩散... 21

3.3.2溶质在低温时减小晶粒间界的扩散... 22

3.4.铜薄膜中铜原子层间的扩散失效... 22

4.铜互连膜合金化的研究现状... 23

5.本课题的研究思想、研究目标和研究内容及可行性分析... 25

5.1.本课题的研究思想... 25

5.2.研究的内容、研究目标及拟解决的关键问题... 25

6.年度研究计划及预期研究结果... 28

7.目前的初步研究结果... 28

参考文献... 31

0 引言

金属化是集成电路一道重要的工序,在集成电路制造工艺中Al是最早使用的内连线材料,然而随着集成电路集成度的不断提高,铝线逐渐不能适应新的要求。其中电阻率偏高和易产生电迁移失效是Al线的主要不足。采用Cu作为内连线材料有以下优点:(a) 电阻率低。Cu的电阻率是1.7 μΩ·cm,比Al的电阻率2.7 μΩ·cm(200℃)低,降低了RC延迟,提高了集成电路的速度。(b) 降低损耗,窄的线宽消耗更少的能量。(c) 高的布线密度。窄的线宽意味着单位面积上可以有更高的布线密度,同时意味着减少布线的层数。(d) 高的抗电迁移能力。Cu的熔点比Al高,因此有更好的抗电迁移能力。

虽然Cu有良好的电学性能,但是集成电路是一个体系,引入Cu可能会产生新的力学和电学问题,引入Cu后主要产生以下问题: (a) Cu对Si有很强的扩散能力。Cu扩散到Si中去会与Si发生反应导致集成电路失效。(b) Cu与Si基体的结合强度不高,易脱落。(c) Cu在低温下(<200℃)易氧化,而且不会形成致密的氧化膜以防止进一步氧化。(d) Cu在热循环过程中要承受比Al更大的热应力。

为了解决上面的问题通常采用如下两种措施:(a)一般在Cu与Si基底之间镀一层扩散阻挡层以减缓Cu与Si基底的扩散和反应,同时提高Cu膜与Si基底的结合强度。(b)在Cu中加入合金元素以提高Cu的抗氧化、抗电迁移能力,同时提高Cu的力学性能。由于采用常规的气相沉积方法获得的扩散阻挡层的台阶覆盖性差,薄膜较厚,因此,合金化作为一种潜在的有效提高界面结合力以及阻止铜硅互扩散的方法,引起了越来越多的人的关住。

国内外已经对合金元素加入到铜互连线中的影响进行了较多的研究,然而,关于合金元素对铜/硅界面处的相互作用、界面反应以及元素间相互扩散的影响的报道还很少。近来,M. J. Frederick 和G. Ramanath的一篇文章对Cu-Mg/SiO2薄膜系统的界面发应以及相互扩散进行了报道。结果表明合金元素的加入对提高铜互连膜的性能较大影响。

本文就是针对铜互连工艺中的影响集成电路质量的铜硅互扩散,根据二维薄膜材料的扩散特点,对导电薄膜材料铜的扩散规律,铜硅界面相互作用以及合金元素对它们的影响进行研究和分析,以期能够消除或者减薄目前常用的扩散阻挡层。

1.大规模集成电路的发展以及铜互连工艺的概述

1.1.大规模集成电路的发展概况

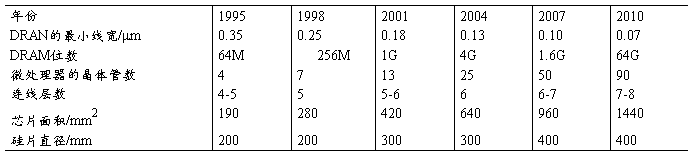

九十年代以后,大规模集成电路(Large Scale Integration,LSI)工艺的发展仍然依照摩尔定律[1](摩尔定律:每三年器件尺寸缩小2/3,芯片面积约增加1.5倍和芯片中的晶体管数目增加4倍。这就是由Intel公司创始人之一的Gordon E. Moore博士1965年总结出来的规律,被称为摩尔定律)所预言的发展速度急剧增加。集成电路技术目前已发展到甚大规模阶段,即ULSI(Ultra Large-Scale Integration)。每一个芯片所含的元器件数已达1亿个,相应其微细加工工艺己到达深亚微米级(小于等于0.35 μm)技术,并将继续向0.25 μm、0.18 μm、0.l μm发展,器件性能则向着更高速、低功耗方向发展。SIA[2](Semiconductor Industry Association)在95年就曾预测未来10年内互连线的发展趋势是:IC的特征尺寸将达到0.07 μm,线宽0.08 μm,布线间距0.12 μm,介质厚度0.5 μm,电源电压将降到1伏,工作频率将达到0.1GHZ。而实际的发展己突破了这一预测。现在微细加工技术己从0.6 μm提高到0.18 μm的水平; 0.18 urn的IG位动态随机存取存储器(Dynamic Random Access Memory DRAM)己研制成功;256 M位的DRAM己进入大量生产阶段;具有64位速度位 IGH的微处理器己宣告研制成功[3]。表1-1为世界集成电路技术发展趋势预测[4]。目前0.25 μm和0.18 μm已开始进入大生产。0.15 μm和0.13 μm大生产技术也已经完成开发,具备了

表1.1 世界集成电路技术发展趋势

Table 1.1 the development of technology world IC

大生产的条件。

随着集成电路特征尺寸的减小和集成密度的提高,金属互连在整个集成电路芯片中所占面积和成本愈来愈高。在深亚微米VLSI,曾有人统计过,一个芯片需要5-6层布线,其内部连线的总长度可达四公里,任何一点的互连线缺陷对芯片来说都是致命的。而一个复杂系统的失效,往往仅仅是由于一个芯片的故障引起的,因为对于一个串连系统,只要一个器件的失效就会导致整个系统的瘫痪,而对于一个并联系统,一个器件的失效会导致其他器件因承受过量应力而迅速毁坏。

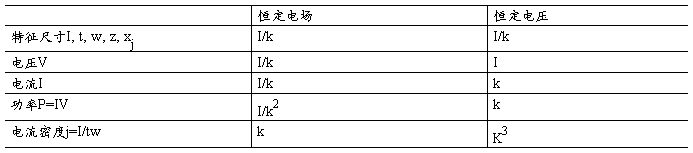

现在的电子系统要求工作在更高的工作频率下,这要求更高的工作电流密度,也就要求更高的可靠性。但是,根据器件等比例缩小[5](Scaling-down)的基本原理,器件特征尺寸的缩小导致了电流密度的上升,而金属化系统所受的影响最为严重。由1989年Gaginj[6]等人分析研究了尺度效应对金属化电流密度的影响,见表l-2。其中k为器件特征尺寸缩小的倍数,也就是金属化系统要缩小的倍数。从表中可见,当特征尺寸卜降k倍时,会使电阻、电流密度增大,产生的焦耳热急剧增加,加速了器件的失效。

表1-2 尺度效应对金属化布线参数的影响

Table 1-2 The scale effect in metallization interconnect

同时,随着互连线横截面积的减小,互连线层数的增加,导致RC时间常数增大,使得减小器件特征尺寸,提高晶体管工作频率和IC传输速度的努力受到制约。据估计,在0.25 μm技术时,互连引线RC时间常数引起的时间延迟己与晶体管本身的延迟相当;当特征尺寸进一步减小时互连引线的时间延迟将成为突出问题。这一部分可以用以下公式来描述[7]:

τ = RC = (ρL/Wt) *(Kε0LW/tILD)

其中τ是指 total signal delay, R是指金属层的电阻, C是指介电层的电容,ρ是互联金属的电阻率,L是指长度,W是指长度,t是指厚度,K是介电常数。由公式可见,选用电阻率比较小的金属材料作为互联材料,和选用介电常数比较小的介电材料是降低信号延时、提高时钟频率的两个主要方向。也是互连线材料选用的重要原则之一。

1.2.ULSI中铝互连线的发展

器件中的金属化工艺是指硅器件及集成电路在完成芯片制造工艺之后,制作欧姆接触和金属连接来完成整个电路的功能。集成电路的金属化的要求是:①与n型、P型硅衬底都形成欧姆接触:②与绝缘膜的粘阻性好;③阻抗低,最好在4×10-9Ω.cm以下;④结构稳定,不易发生电迁移及腐蚀现象;⑤易刻蚀;③淀积工艺简单;①成本低。

在采用铜互连线以前,金属化系统的两大分支是铝金属化系统和金金属化系统。由于金抗电迁徙能力远高于铝,而且其电阻率也远低于铝,因此在大功率器件中用的较多。但是,因为金的成本远高于铝,而且金/硅界面互溶问题严重,所以,在VLSI和小功率器件中普遍采用铝金属化系统。

铝应用于金属化系统中,具有以下的优点而被半导体器件和集成电路生产厂家广泛采用:①电阻率小:②与热生长的SiO2或淀积的介质膜有良好的粘附性;③能与半导体形成较低的欧姆接触;④便于淀积和光刻。

但是,随着微细加工线条尺寸的缩小,铝互连线的缺点也越来越显示出来[3,8,9]。首先铝的电阻率偏高(2.7 μΩ·cm),RC延迟效应较强,降低集成电路的速度;其次,铝的熔点低,容易产生电迁移失效:即当集成电路工作时,铝互连线内会有一定的电流通过,导致铝互连线中的铝离子出现热激发,与电子产生动量交换,并沿着电子流的方向迁徙,这种传输过程在高温(T>200 ℃)和大电流密度(j>=106 A/cm2)的作用下尤为显著。经过几小时至几百小时后,铝布线就会出现空洞、裂纹和晶瘤,从而造成集成电路开路失效,这就是电徙动现象,也称为电迁徙或电迁移[3]。产生电迁移失效的内因是铝布线内部结构的非均匀性,外因是高温和大电流密度。铝布线的条宽越窄,发生电迁移失效的几率就越大。随着集成电路集成度的不断提高,要求集成电路的特征尺寸越来越小,这样继续采用铝布线会严重影响集成电路的可靠性。

在高温下(大于400 ℃),硅会向铝中融解,形成化合物。时间越长,温度越高,融解的硅就越多,就形成了渗透坑。以后就是渗透坑逐渐长大的阶段,因为渗透坑表面自由能最小,所以硅饱和以后小坑逐渐长大,坑数减少,坑尺寸增大,最后导致短路或开路失效。同时,铝金属膜还存在较为严重的腐蚀,在通电的情况下,铝膜会发生电解腐蚀,造成器件失效。据统计有,有30~50%的集成电路失效是由铝互连线失效引起的。而且,铝的机械强度小,在工艺中容易划伤。

另外,互连线尺寸大,单层布线少;低温下不能沉积形成高纵横比的通道;易与高分子材料粘附;很难平面化等也成为限制Al互连线广泛应用的缺点。其中电阻率偏高和易产生电迁移失效是Al互连线的主要不足[9]。

到了ULSI阶段,铝金属化布线系统随着互连引线横截面积的减小和互连线层数增加,互连线电阻变大,RC时间常数增大,使减小器件特征尺寸,提高晶体管工作频率和IC传输速度的努力受到制约,成为深亚微米集成电路速度提高的瓶颈。

综上所述,铝互连线已成为制约微电子技术发展的主要技术因素,使研究新的互连材料成为必然趋势。

1.3.ULSI中铜互连线工艺的提出、发展及存在的问题

1.3.1.铜互连工艺的提出

为了克服铝布线抗电迁移能力差的弱点,国外对铝布线作了种种的改进,例如:采用含2%硅或1%铜的铝合金布线:增大铝的晶粒尺寸;采用介质膜覆盖铝线,介质膜P2O5·SiO2,Si4·N3SiO2,Al2O3·SiO2等:采用以金为主的多层金属布线:以及使用铜互连[10-12]。

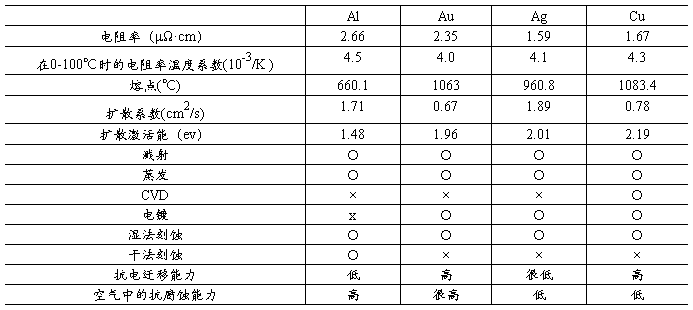

表1.3 几种不同互连线金属性能的比较

Table 1.3 The comparison of characteristic in metal interconnect material

从八十年代初开始,各大公司就开展了寻找铝的替代物的研究(见表1.3)。经过研究和比较,最后纷纷采用了铜互连技术。一般来讲,0.18 μm以下的IC布线必须要部分或全部采用铜互连线。1994年,欧洲西门子公司赞助了一个名为COIN(Copper Interconnection)的研究项目[13],重点研究铜互连技术,美国Motorola公司已成功研制了高性能0.18 V,0.2 μm CMOS铜布线技术,它的第一批产品是静态随机存取存储器(Static Random Access Memory,SRAM)。 IBM公司0.25 μm ULSI中采用全新的铜互连技术。此后,世界著名的半导体公司纷纷投入财力、物力、和人力,开展铜布线的研究与开发,并取得了丰硕的成果。

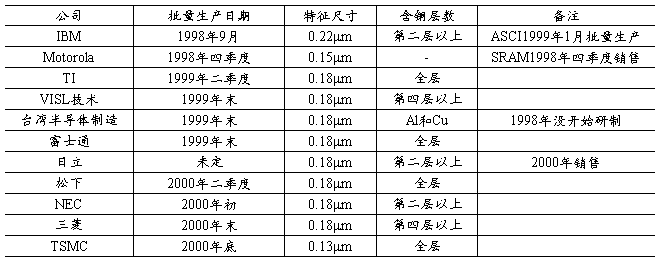

表1.4给出了世界主要半导体公司采用铜布线的进展情况[14]。从表l.4中可知,美国是首先采用铜布线的国家,IBM公司是开路先锋,日本比美国约晚两年左右,美国IBM公司于1997年9月在世界上首先研制成功CMOS-7铜布线工艺,并在1998年9月1日开始批量生产铜互连线商用IC,如400MHz POWER PC740/750微处理器,它主要用干台式、笔记本式PC和高档消费类电子设各。APPLE公司首先将IBM公司的铜布线IC用干第一流的主机,小型计算机和工作站,1998年底出样机,1999年批量生产。MOTOROLA和AMD公司联合开发了铜布线技术,用于新一代IC,如蜂窝电话和联网装置用嵌入式IC、台式IC中微处理器等,MOTOROLA公司子于1998年四季度批量生产铜布线500MHz POWER PC芯片,AMD公司将铜布线技术用于K7微处理器,子1999年上市,TI公司子1999年下半年将铜布线用于更先进的DSP,其处理速度可比原来的产品快10倍。

经大量实践证明,正如图表所示的那样的,铜互连与铝互连相比有如下优点[15-18]:

1)铜的电阻率比铝低,铜电阻率1.7 μΩ·cm,铝的电阻率为2.7 μΩ·cm,铜的电阻率仅

表1.4给出了世界主要半导体公司采用铜布线的进展情况

Table 1.4 the development of copper interconnect in the main semiconductor company

(续)

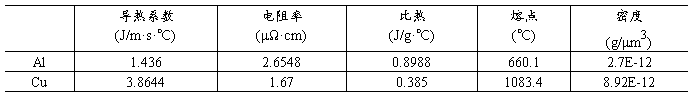

为铝的60%(见表1-5)使铜互连中的RC延迟明显减小,相应的互连线的功耗降低很多。铜与铝相比,导热系数是铝的3倍,散热性能更加优良。且当互连线线宽缩小到< 0.25 μm 时,Al及其合金的电阻率已不能再满足使互连的时延同步降低的要求。铜与铝的基本参数比较如表1.4所示。

表1.5 铜与铝基本参数的比较

Table 1.5 the comparison of the basic parameter of copper and aluminum

2)与传统的铝互连线相比,铜具有抗电迁移和应力迁移特性强等优点。在相同的条件下,铜发生电迁移的电流密度上限是5×106A/cm2远大于铝的上限2×105A/cm2,比较相同晶粒尺寸下的电迁移性能[18],铜是0.77 ev左右,纯铝为0.48 ev,Al-4%Cu为0.57 ev,铜

互连线的抗电迁移性能提高了约两个数量级,大大提高了集成电路的可靠性[19]。在大的电流密度下,Al易发生电迁移。而且在300 ℃左右的工艺温度下,Al薄膜上会形成突起,穿透相邻互连线之间的电介质绝缘层造成短路。因为铜的熔点要高于铝的熔点,铜互连线可以承受更大的电流密度,从而可以缩短连线的长度,减少布线的层数,提高集成的密度,降低集成电路的成本。

3)铜互连线与低介电常数(k < 4)的材料(取代布线层间的SiO2)相结合,可以进一步减小寄生电容。根据文献[20]中的模拟结果,若降低K材料与铜互连结合使用,可以简化工艺,降低成本,并将RC延时降低到原来铝互连的1/4~1/6。

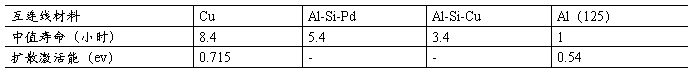

表1-6为微电子可靠性物理实验室对中科院微电子中心生产的铜互连进行了电学加速实验结果[21]。在T=150 ℃,J=3.5×106 A/cm2下,互连线宽度为1 μm的铜与铝及铝合金的中值寿命(互连线失效的数量达到测量互连线总数的50%所需要的时间)和扩散激活能的比较结果。铜互连线与铝互连相比中值提高8倍左右。铜作为互连线金属化材料优势是明显的。

表1.6 不同互连材料的中值寿命及扩散激活能

Table 1.6 MTF value and Diffusion Activation energy of diffusion materials interconnects

因此,综上所述,铜是一种比较理想的互连材料,铜布线代替铝布线是一种发展趋势。它可使局域互连的传输速度改善10%,使整体互连的传输速度改善50%,保证集成度提高的同时也能提高速度性能。Cu还具有与通常采用的扩散势垒材料的反应性低等优点。

铜互连技术的研究和应用虽然取得了很大的进展,但由于采用了全新的材料和制造工艺,目前尚未达到成熟应用阶段,其技术尚待改善,但在不久的将来,铜布线代替铝来提高互连的可靠性是可以预料的。

1.3.2.铜互连技术的主要问题

与铝互连线相比,铜互连线虽然在改善RC延迟和可靠性方面有着很大的优势,当在实际应用中还存在着较大间题,这些问题影响着铜互连线的推广和应用。铜互连线技术的主要缺点是;

1.铜的工艺问题。采用铜互连线技术虽然可以简化工艺,但是铜的图形化加工十分困难[22]。对于铝互连线,主要是采用铝的氯化物来实现对铝的刻蚀。而对于铜,其氯化物或氟化物在低温下都是不易挥发的,不能采用传统干法对它进行等离子刻蚀,无法达到一定的刻蚀速率。而如果加温到200 ℃以上,会使传统的光刻胶融化。如果采用化学汽相沉积(CVD)或物理汽相沉积(PVD)沉积铜,由干铜的粘附性较差,需要先成长一层粘附层,增加了工艺的复杂度。关于铜互连及其相关工艺的研究及发展情况,已经进行了大量的报道[23-30],这里就不再累述。尽管这些工艺在最近5年迅速发展,但是对于它们的深入基础理论的研究还不够,特别是从材料科学的领域还可以进行大量研究工组。

2.铜互连线中的失效机理问题。铜互连线作为一种新技术,在材料。工艺、布线结构上均有别于铝互连线,所以有其特殊的失效模式和失效机理。铜互连线中的失效主要为电迁移失效和应力失效。其中包括诸如小尺寸接触和通孔的电迁移特性及热效应;多层互连中不同层互连线的电迁移行为;多层膜结构对电迁移的影响;不同膜沉积工艺对其本身晶体结构和相邻膜晶体结构、特性的影响等。可以说,自从铜互连工艺提出以来,其电迁移以及应力失效就一直是一个研究的重点,关于这方面的文章包括薄膜微观结构[31-35]、应力失效[36-40]及二者的关系[42-44]和薄膜中的电迁移及电迁移过程中应力模拟分析[44-48]更是类不胜数。近年来的研究表明,形成竹节状的晶粒组织结构对互联膜的抗电迁移性能有很大的提高[49-50]。

3.铜互连线表面的氧化问题。铜很容易在空气中氧化和硫化。如果铜被氧化,其电阻会直线上升,造成器件的不稳定。所以在实际应用中,铜甚至不应在较高的温度(高于100 ℃)下直接暴露在空气中,一般应在其上加钝化层。文献[51]对铜互连的表面氧化及其氧化机制进行了详细的报道。常见的防止铜互连膜的氧化是在表面应用一层阻挡层,S. P. Murarka的研究表明,添加合金元素可能会成为一种防止铜互连氧化的有效的方法[52]。目前,关于合金元素对铜互连薄膜的影响的研究正引起越来越多的人的注意[53-59],而这也为本次课题的提供了一定理论依据。

4.铜的沾污问题,也称“铜中毒”。铜在硅中属于填隙性杂质,如果铜原于扩散进入硅器件,就会产生深能级受主杂质而降低器件的性能。虽然铜原于在介质中的扩散速度并不快,但是在有电场偏置的情况下,铜离子可以快速的扩散。目前,关于铜在硅中的扩散还没有一个确定的表达式,常用的铜在硅中的本征扩散可由式(2-l)来表示[60]:

D = D0 exp(- ) = 4.7×10-3(cm2/s) exp(-

) = 4.7×10-3(cm2/s) exp(- )

)

一旦铜原子进入硅中,就会在硅中迅速扩散。使器件的性能受到很大的负面影响。铜在200 ℃下容易与硅界面反应形成CuSi3高阻化合物,降低其绝缘性能,引起介质穿通,使器件性能大犬降低[11,61]。

综上所述,Cu在低温(< 200 ℃)下空气中很易氧化,其氧化层不具备防护作用;与常用的电介质薄膜材料附着力差;在较低温度下形成Cu 的硅化物等等所有这些缺点都会对器件可靠性造成伤害。为了解决上面的问题通常采用如下两种措施:(a)一般在Cu与Si基底之间镀一层扩散阻挡层以减缓Cu与Si基底的扩散和反应,同时提高Cu膜与Si基底的结合强度。(b)在Cu中加入合金元素以提高Cu的抗氧化、抗电迁移能力,同时提高Cu的力学性能。

2.铜互连的扩散阻挡层的发展现状的概述

目前在Cu与Si,Cu与SiO2之间加一合适的扩散阻挡层是成功应用Cu材料的关键。当前研究最多、最具吸引力的阻挡层材料是难熔金属(W, Ta, Ti, Mo, Cr)以及它们的氮化物。因为它们具有高的熔点、高热稳定性、优良的电导特性,以及与介质材料具有良好的附着性。[62-71]

以下是几种常用的阻挡层

A)纯金属

选择纯金属作为扩散阻挡层首先是因为金属有良好的导电性。所选择的金属应该与上下两种物质有很强的化学稳定性,且不互溶或互溶度很小。在集成电路制造工艺中W、Ta都是常用的阻挡层。利用纯金属作为阻挡层产生的主要问题是晶界扩散。纯金属在室温不能以非晶态存在,一般来说是多晶,而晶界扩散是薄膜中扩散的主要方式,这也是纯金属作为扩散阻挡层的主要缺点。

B)单晶阻档层

Tu和Rosenberg[72]研究了Pb/Ag/Au多层膜的扩散现象。其中一组试样中Ag膜和Au膜为单晶薄膜,另外一组试样Ag膜和Au膜为多晶薄膜,它们的平均晶粒尺寸为3.5 μm。其中Au与Ag互溶,且与Pb形成化合物,而Ag与Pb不发生反应而且互溶度很小。对单晶薄膜的那组试样,多层膜在200℃退火48 h后,发现Ag膜完好,在可观测的范围内没有发现Pb和Au发生相互扩散,而对Ag膜为多晶的那组试样在200 ℃退火24h后发现在Pb-Au的界面有PbAu生成。这个实验表明单晶薄膜有很好的阻挡效果,这是因为单晶薄膜没有晶界、位错等扩散的快速通道。由于单晶薄膜对材料和工艺过程要求都很苛刻,如与基底材料的晶格匹配,故理论研究有价值,但在实际的集成电路生产工艺中很难采用单晶薄膜作为扩散阻挡层。

C)化合物阻挡层

化合物阻挡层突出的优点在于它优良的热稳定性和化学稳定性。金属的氧化物、氮化物是理想的阻挡层,它们对Cu,Au,Ag有很好的化学稳定性,而且这儿种金属的氮化物非常稳定,有很高的熔点。另外,金属阻挡层和单晶阻挡层的研究表明晶界是影响阻挡层阻挡效果的重要因素,化合物阻挡层中氧原子、氮原子如果在晶界、位错等快速扩散通道处塞积,将大大提高阻挡层的阻挡效果但作为一种理想的阻挡层必须同时具有很强的导电性。Nelson [73]研究表明Ti, Zr, W, Mo, Ta的氮化物和硼化物的导电性比纯金属还好,表1.5是文献[74]

表2.1 Ti、Zr、Ta、W、Mo的单质、氮化物、硅化物、硼化物、碳化物的电阻率

Table2.1 The resistivity of Ti、Zr、Ta、W、Mo and of nitrides、silicides bordides、and carbides of these materials

收录的几种常用化合物阻挡层的电阻率。可以看出化合物阻挡层的电阻率和纯金属相差不

多,甚至有更低的电阻率。

D) 非晶阻挡层和纳米晶阻挡层

非晶薄膜的晶界排列不规则,是非常理想的阻挡层[75]。利用非晶薄膜作为阻挡层,最大的问题是非晶阻挡层的晶化温度,因为非晶薄膜是一种亚稳、非平衡的结构。研究表明[76],通常非晶薄膜的晶化温度约为1000 ℃,因此完全可以用作阻挡层。纯金属一般不能以非晶的形式存在,而非金属单质的非晶电阻率太高不适合作为阻挡层。较好的非晶阻挡层是金属和非金属的化合物。其中(Mo、Ta、Ti、Zr、W)-Si-N的三元化合物是目前研究较多的非晶阻挡层[68,75],纳米晶阻挡层同样是性能非常好的阻挡层[76],纳米晶阻挡层、非晶阻挡层的出发点与单晶阻挡层的想法相似,都是减少晶界的数量,但纳米晶阻挡层和非晶阻挡层在制备上要求不是很苛刻,成本不是很高,因此有实际应用价值。非晶阻挡层和纳米晶阻挡层往往依赖于制备工艺,对于同种化合物,用离子束辅助磁控溅射制备得到的是纳米晶或者是非晶,而一般的磁控溅射沉积的则是多晶薄膜。应该指出的是扩散阻挡层不能从根本上抑制Cu与Si发生反应。因为Cu与Si的扩散依然存在,它只能减缓上述反应,阻挡层的失效是一个时间的函数。

绝大多数扩散阻挡层材料的热稳定温度均在550 ℃以上. 原子层沉积的WNxCy 是目前最好的阻挡层材料[77],W也是很好的阻挡层材料,多用于元器件中需要做成欧姆接触的部位。为了防止Cu外扩散到Si中破坏器件,必须对分布在IC各层中所有部位上的Cu导线和插件接头进行全封闭式的包敷。这样,互连中的另一个主要挑战是要显著减小包裹铜互连线的阻挡层厚度。当互连线的特征尺寸减小时,电阻较大的20nm厚的阻挡层将成为互连线剖面的重要部分,使其导电性能退化。因此,需要一种更薄的阻挡层,但仍能保持有效且与可能的纳米多孔低k介质材料相兼容,这就可能需要采用能对组分和厚度进行原子层控制新的生长工艺技术。因此,包敷的阻挡层应该足够薄,以使Cu导线的截面尽量大。在冶金上要求阻挡层薄膜是稳定的,不与Cu发生反应,但与Cu具有好的粘附性。阻挡层薄膜的表面特性和微结构对后续沉积生长的Cu 膜的结构和晶粒大小有强烈影响,它决定了Cu导线的电迁移可靠性,因此要求势垒薄膜的微结构对沉积Cu具有某种籽晶的作用。

综上所述可知,随着集成电路的集成化发展,对扩散阻挡层的工艺和性能要求越来越苛刻。并且由于采用常规的气相沉积方法获得的扩散阻挡层的台阶覆盖性差,薄膜较厚,在互连线尺寸越来越小的今天,扩散阻挡层在一定程度上减小了Cu的可用空间。从而限制了铜互连工艺的发展和应用。因此,寻求另外一种方法来阻止铜硅的互扩散,改善界面结合力就成为材料科学者们非常感兴趣的课题。

3.扩散基本理论以及铜互连薄膜中的二维扩散研究的现状

扩散是固体材料中的一个重要现象,也是材料科学研究领域中的一个重要的方面,目前对三维体材料中的扩散已经研究的相当普遍,而对二维薄膜材料中的扩散问题研究的相对薄弱些。但是随着电子工业的发展,特别是集成电路行业迅速发展,对于薄膜材料的需求越来越大薄膜材料中的扩散问题也越来越成为影响集成电路质量的重大问题之一,特别是近年来铜互连和原子层沉积工艺的出现,防止铜扩散也是关键的技术。本项目是针对影响集成电路质量的扩散问题,从材料科学的角度进行分析,根据二维薄膜材料的扩散特点,重点研究作为导电薄膜材料铜的扩散规律。应当说明的是本项目是根据集成电路有关工艺所涉及的有关扩散的基础问题,从材料科学固体物理角度进行多学科、综合性分析探讨,而不是对具体的制造工艺(例如铜互连和原子层沉积工艺等)进行研究。

3.1.Fick扩散定律及扩散系数

3.1.1.Fick第二扩散定律

1858年菲克(Fick)参照了傅立叶(Fourier)于1822年建立的导热方程,获得了物质从高浓度区向低浓度区迁移的定量公式,即Fick第一扩散定律和Fick第二扩散定律。这是针对固体材料中的体扩散而言的。由于大部分的扩散都是一个非稳态过程(即各点浓度随时间而变化),这里我们主要对Fick第二扩散方程及其解进行一下讨论:

Fick第二扩散定律: =

= (

(

)

)

其中 为晶格扩散系数,如果

为晶格扩散系数,如果 和浓度无关,则上式可写成:

和浓度无关,则上式可写成: =

=

Fick方程的解按照扩散系统的边界条件的不同而不同。下面主要讨论一下二种情况:

1) 薄膜源扩散

设想在一根很长的金属棒的一段镀上一薄层溶质,其总质量为 然后将它与另一根相同的金属棒B焊接起来,把薄层夹在中间。两棒不含溶质(即C=0),其横截面均匀,在一定温度下退后,那么可得到如下的溶质浓度C沿

然后将它与另一根相同的金属棒B焊接起来,把薄层夹在中间。两棒不含溶质(即C=0),其横截面均匀,在一定温度下退后,那么可得到如下的溶质浓度C沿 方向分布和退火时间t的关系式:

方向分布和退火时间t的关系式:

C= exp (-

exp (- ) (3.1)

) (3.1)

若薄膜源物质向一方扩散,则扩散解相应为C= exp (-

exp (- )

)

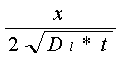

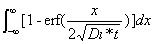

2) 半无限长物体的扩散

半无限长物体的扩散特点式,表面浓度保持恒定,而物体的长度大于 时,则扩散解对应为:

时,则扩散解对应为:

C=C0 [1-erf ( )] (3.2)

)] (3.2)

其中erf (β)= 定义为误差函数,

定义为误差函数, =

=

其初始条件为t=0时, >0, C=0;

>0, C=0;  < 0, C=C0 其中,D为晶格扩散系数。

< 0, C=C0 其中,D为晶格扩散系数。

此公式适用于铜薄膜在扩散阻挡层以及单晶硅衬底和多晶硅衬底的高温体扩散。

3.1.2.扩散系数的确定及Arrhenius公式

根据式(3.1)就可以用实验的方法把扩散系数 求出来:先做出c-x的关系曲线,如果把lnc对

求出来:先做出c-x的关系曲线,如果把lnc对 2做曲线图,我们应该得到一根直线,其斜率为

2做曲线图,我们应该得到一根直线,其斜率为 ,退火时间已知,就可以求出扩散系数

,退火时间已知,就可以求出扩散系数 。

。

由扩散系数的表达式  =

= 0exp(-Q/RT ) 得到ln

0exp(-Q/RT ) 得到ln =ln

=ln 0-Q/RT

0-Q/RT

显然,ln 与1/T成直线关系,ln

与1/T成直线关系,ln 0为截距,为斜率。如果在几个不同的温度下测得相应的扩散系数,就可以在半对数坐标系中绘出它们的关系直线。

0为截距,为斜率。如果在几个不同的温度下测得相应的扩散系数,就可以在半对数坐标系中绘出它们的关系直线。

3.2.薄膜扩散理论

由于在铜互连工艺中的失效问题大都是由于铜硅互扩散形成高阻硅化物(即所谓铜中毒)以及电迁移,应力迁移和层间扩散失效等造成的(但主要是以铜互连线电迁移失效为主),而这一切都与铜原子的在铜薄膜,衬底以及界面处的扩散有关,即可以说铜原子的扩散可以说是铜互连失效的一个主要原因。因此,研究二维薄膜中原子的扩散规律就具有了重要的实践意义。

薄膜技术在许多方面都要求详细地了解金属薄膜间的相互扩散或相互作用,这是研究这类现象的重要激励因素,并且就研究这个现象本身的价值来说,它已经具有足够的意义。1971年以后,由于韦弗[78]写的评论的结果,显著地增加了实验研究薄膜间相互扩散的数量。实际上,早在1942年,Coleman和Yagley就对Au、Pb薄膜之间的相互扩散进行了系统的研究。然而由于当时实验仪器和方法的限制,薄膜扩散研究还存在很大的困难。人们一直努力试图通过直接测量截面的深度分布来确定扩散的系数,直到D.Gupta等人用背溅射截面连续剥离的方法而使薄膜的研究有了一个新的转折点[79]。随后,Eicke R. Weber对硅中3d族元素的扩散做了系统的研究和报道,并对3d族元素在Si中以带电形式存在,并在高温以及低温下不同的扩散机理进行阐述[80]。而自从铜互连工艺发展以来,特别是近年来,人们对铜以及过渡族元素在Si中的扩散形式以及扩散规律进行了较多的研究[81-89]。

金属薄膜中相互扩散有着与众不同的特征,最突出的一点是在低温下大规模的物质传输过程,它不仅是由于可观测到的扩散时间可以很短,所以传输距离短,也由于薄膜能够包含大量缺陷的性质所造成的。一般情况之下,扩散距离是远小于平均的点缺陷间距,但是在电子薄膜中,即使是在低温下,由于晶界等扩散系数大于体扩散系数,因此,点缺陷的平均间距小于低温扩散距离。点缺陷的间距缺陷,除了控制着相互扩散过程之外,还能够显著提高参加扩散或参与反应的物质的数量,这些在平衡相图的概念中是不可理解的。因此,尽管关于薄膜扩散论题方面有着丰富的实验数据,但是至今还没有提出一个针对薄膜中大规模相互扩散的详细理论[90]。

3.2.2.单晶薄膜的扩散动力学理论的研究

在实际应用中很少有用单晶薄膜的,但是测量特殊生长的单晶薄膜间的相互扩散,能够提供有关块体扩散率和激活能的明确数值。而这些数值,对于解释较为复杂实用的多晶薄膜的扩散过程来说,具有根本性的意义。

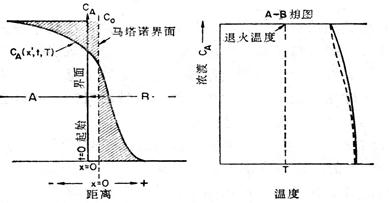

以二个可相互混容的金属A和B的单晶薄膜之间产生平面型的相互扩散为例,如图3.1

所示。图示出了合成的有效马塔诺界面,它是深度尺度的起始点。阴影面积是相等的。相图指出,温度T时,在 上将没有突变点。这样,A试样的原子有效传输可用

上将没有突变点。这样,A试样的原子有效传输可用 AB(X)来描述,这里

AB(X)来描述,这里 AB(

AB( )=

)= ACB(

ACB( )+

)+ BCA(

BCA( )。

)。

由菲克第二定律 : =

= (

(

) (3.3)

) (3.3)

图3.1 不同扩散速率时,单晶可混容试样A和B的相互扩散。

Fig.3.1 interdiffusion of the miscible unit crystals A and B at different diffusivities

如果在任何瞬间时间t中的距离用相对于Matano界面的 ’来测量,以取代在同一时间t时相对起始界面的

’来测量,以取代在同一时间t时相对起始界面的 ,那么方程式就可以简化。图3.1中说明了这种情况。其中Matano界面(

,那么方程式就可以简化。图3.1中说明了这种情况。其中Matano界面( ’=0)是在满足下列条件时,从物理学界面(

’=0)是在满足下列条件时,从物理学界面( =0)转化过来的,也就是说,图3.1上的阴影区是相等的。

=0)转化过来的,也就是说,图3.1上的阴影区是相等的。

=

= (3.4)

(3.4)

然后可以证明CA( ,t)只是变量

,t)只是变量 的函数,这样式(2)可以写成

的函数,这样式(2)可以写成

-

=

=

(3.5)

(3.5)

用相应的进行积分,得到 (C=C1)=

(C=C1)=

(3.6)

(3.6)

和体扩散的方程解一样,式(3.6)提供了一个手段,它是能够利用实验测定的,借助于这个扩散样品中C随深度的变化可求得浓度函数的数值,可以直接从C相对的实验曲线中计算出斜率和积分,然后给出在实验温度时的扩散率,从而得到一曲线,由此求得激活能的实验值。

3.2.3.多晶薄膜扩散动力学理论的研究

对于目前通常采用的金属多晶薄膜,固态扩散有三个途径:晶格扩散、晶界扩散和表面扩散,我们称之为短路扩散。其中晶格扩散是依靠空位的移动来完成,晶界扩散指离子流沿晶粒界面间隙扩散,表面扩散的途径是金属薄膜表面。对于多晶膜而言,是以晶界扩散为主。实验发现,三种扩散均是各向异性的,杂质的存在对扩散速率有一定的影响。一般来说,若杂质的加入带来新缺陷,则扩散加速。

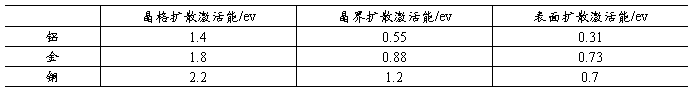

表3.1 为不同金属薄膜的扩散激活能的比较

Table 3.1 Diffusion activation energy value of different metal film

表面扩散和晶界扩散较容易,晶格扩散最难。因为晶界和界面处的位错密度大,空位浓度高,晶格畸变较大,能量较高。而晶格扩散主要是以空位扩散为主,晶格扩散比起晶界扩散难度加大。一般而言,晶界的扩散激活能约为晶格的扩散激活能的0.6-0.7,金属外表面的扩散激活能比晶界的还要小。即一般来说表面扩散那系数最大,其次是晶界扩散系数,而点阵扩散的体扩散系数最小。

3.2.3.1.晶界扩散的特性

通常用示踪原子法观测晶界扩散现象,在试样表面涂以溶质或溶剂金属的反射醒同位素的示踪原子,加热到一定温度并且保温一定的时间。示踪原子由试样表面向晶粒与晶界内扩散,由于示踪原子沿晶界的扩散速度快于点阵扩散,因此示踪原子在晶界的浓度会高于在晶粒内,与此同时,沿晶界扩散的示踪原子又由晶界向其两侧的晶粒扩散。即其浓度分布形成一个等浓度线在晶界上比晶粒内部的深度大得多的分布。

晶界扩散具有结构敏感性,在一定温度下,晶粒越小,晶界扩散越显著;晶界扩散与晶粒位相、晶界结构有关;晶界上杂质的偏析或淀析对晶界扩散均有影响。

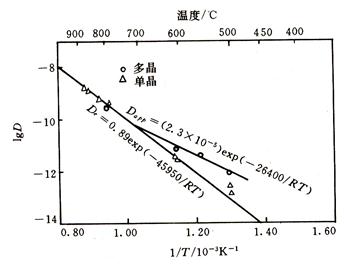

晶界扩散所起的作用因温度的高低差别很大,如图3.2所示[91]。

在较低的温度范围内,多晶体直线关系的斜率为单晶体的1/2,但是在700 ℃以上,两条直线相遇,而后是单晶体直线的延长,这说明温度低时,晶界激活能比晶内小得多,晶界扩散起重要作用;随着温度升高晶内得空位浓度逐渐增加,扩散速度加快,故占截面比例很小得晶界扩散,随温度得升高逐渐被晶内扩散所掩盖。

图3.2 Ag在单晶和多晶体中的自扩散系数

Fig.3.2 Self-diffusion coefficient of Ag in unit crystal and polycrystal

3.2.3.2.晶界扩散的理论模型

已经证明,与单晶薄膜不同,由于晶界的影响,在低温下多晶薄膜中也可以发生大规模的相互扩散。现在已经知道,沿晶粒间界的扩散要比通过块体晶格扩散快几个数量级。关于晶粒间界的扩散现象,虽然早在1936年已经可以在资料中找到,但是正式地讨论它是在1951年,由费希尔,霍夫曼和特恩布尔进行的。经过这些年精心设计的晶粒间界扩散实验,已经提高了我们对晶粒间界的结构和化学的认识。现在,由于薄膜技术对制造平面微电子学元件的重要性,有许多学术年会致力于低温扩散和应用于薄膜的问题。然而由于扩散途径的多样性,多晶薄膜之间的低温扩散率不能用单一的扩散机理的概念来描述,相应地,晶粒间界扩散实验的数学解析一般要比晶格内部扩散的更为复杂。由于晶粒间界的扩散很少能够脱离晶格,所以扩散物质很可能渗入到相邻的晶格中去。它的渗透程度决定了动力学的模型。下面主要对二种晶界扩散的模型进行讨论。

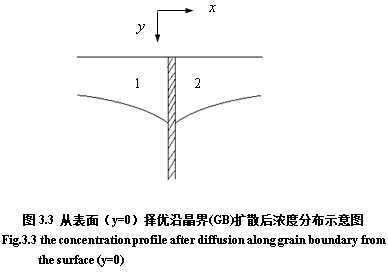

1. 晶界扩散的Fisher模型[91]

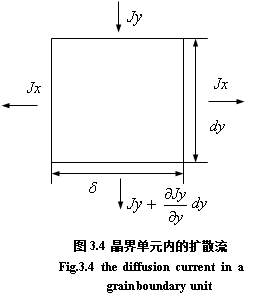

为了确定晶界的扩散系数DG,Fisher设计了一个实验。取双晶粒晶体,其表面垂直于晶界,在表面涂覆一层放射性同位素随之进行扩散。如图3-3所示,由于晶界扩散比晶内扩散快得多,因此,对于晶粒1或2来说,除了有垂直于表面的扩散以外,还有垂直于晶界的扩散流。其可能的浓度分布也示于图3.3中。

设晶界宽度为 ,在其上沿

,在其上沿 方向取一段

方向取一段 。如图3.4所示,先研究这一小段晶

。如图3.4所示,先研究这一小段晶

界内的扩散问题。

假设任何垂直于轴的平面 (平行于图示所在平面)都是对称平面,因此, =0。设取该小晶界单元的厚度为单位厚度,即取1,则在扩散过程中,该小单元晶界内的浓度变化率为:

=0。设取该小晶界单元的厚度为单位厚度,即取1,则在扩散过程中,该小单元晶界内的浓度变化率为: =

= {

{ [

[ -(

-( +

+ ·

· )-2

)-2 ·

· ]=-

]=- -

-

(3.7)

(3.7)

式中 -在晶界内沿方向的扩散流量;

-在晶界内沿方向的扩散流量;

-在晶粒内(1和2)沿着x轴方向(垂直于晶界)的扩散流量。

-在晶粒内(1和2)沿着x轴方向(垂直于晶界)的扩散流量。

设晶粒内的扩散系数为Dl*,则:

=-

=- l

l │x=

│x=

设晶界扩散系数为 b*

b* ,由此得晶界内的扩散方程为:

,由此得晶界内的扩散方程为:

=

= b*

b* +

+

l*(

l*( )x=

)x= (3.8)

(3.8)

晶粒1内的扩散方程为:

=

= l*(

l*( +

+ +

+ ) (3.9)

) (3.9)

设所研究的扩散问题的初始、边界条件为:

C=C0 当 =0 和t ≥ 0;C=0 当

=0 和t ≥ 0;C=0 当 =0 和t=0

=0 和t=0

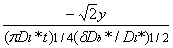

则对晶界和晶内扩散方程的解,必须同时满足扩散方程(3.8)和(3.9),同时在边界上是连续的。Fisher分析了(3.8)和(3.9)的数值解,为了简化扩散方程的解,可以假设晶界上各点的浓度Cb(y,t)扩散开始后不久,即已确定,在以后继续扩散的任何时刻,均为定值。这样,可以把晶粒分割成平行于表面的许多薄片,对每一薄片内的扩散问题,处理成边界浓度为定值的一维扩散,因而有扩散方程的解为:

C( ,

, ,t)=Cb(

,t)=Cb( )[1-erf (

)[1-erf ( )] (3.10)

)] (3.10)

把各片中的等浓度的点联系起来,得到:

C( ,

, ,t)=C0exp[

,t)=C0exp[ ]×[1-erf (

]×[1-erf ( )]

)]

求每一片平行于自由表面的厚的薄片中的放射性物质量,此量正好等于由晶界吸收的放射性物质量,可以得到:C( ,t)=C0exp[

,t)=C0exp[ ]×

]× =C0exp[

=C0exp[ ]·K (3.11)

]·K (3.11)

这就是晶界扩散的Fisher模型的解。绘制lnC对 的关系图,得到一条直线,其斜率为:

的关系图,得到一条直线,其斜率为: ,按表面涂层的半无限系统中扩散物质的浓度分布公式推知,lnC有

,按表面涂层的半无限系统中扩散物质的浓度分布公式推知,lnC有 2直线关系。这差异,说明Fisher的处理是近似的。

2直线关系。这差异,说明Fisher的处理是近似的。

目前的半导体材料大都是沉积形成的多晶膜,由于金属薄膜沉积过程中的杂质污染,薄膜中存在着大量缺陷,包括点缺陷、线缺陷和面缺陷。正是这些缺陷的存在,极大地影响了金属离子的微观扩散机制,对金属薄膜的电迁移以及可靠性造成了极大的影响。尤其是空位与晶界这两种缺陷对可靠性的影响最大。因此,Fisher的晶界扩散模型对提高铜互连工艺可靠性,改善工艺具有重要的理论指导意义。

2. 晶界扩散的惠普尔(Whipple)扩散模型[90]

解析模型的讨论可分成四个主要的部分:(1)相应于B类动力学的孤立间界,即假设任何间界都是相互孤立的,而扩散流在x方向上,在很远时才趋近于零值;(2)相应于A类动力学的、具有相互作用扩散场的平行晶粒间界,即有大量的晶格扩散;(3)相应于C类动力学的晶粒间界扩散,在晶格内其扩散长度接近于零;(4)在驱动力作用下的晶粒间界扩散。

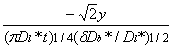

对于孤立间界的晶界扩散,根据Whipple的扩散模型,由勒克莱尔推导,可从下列表达式计算间界扩散率:

=(

=( )-3/5 (

)-3/5 ( )1/2 (

)1/2 ( )5/3 (3.12)

)5/3 (3.12)

其中 =(

=( -1)(

-1)( );

); =

= ;

; 为溶质偏析系数;

为溶质偏析系数; 和

和 分别为晶界和晶格扩散系数;

分别为晶界和晶格扩散系数; 为晶界宽度。

为晶界宽度。

莱文和麦卡勒姆用数学运算说明了量值 几乎和

几乎和 无关。对于无限源,

无关。对于无限源, =0.78,这样式(3.12)可以变形为

=0.78,这样式(3.12)可以变形为

=0.661(

=0.661( )-3/5 (

)-3/5 ( )1/2 (3.13)

)1/2 (3.13)

由Fick第二扩散定律得到,通过式(3.13)就可以求出晶界扩散系数

由Fick第二扩散定律得到,通过式(3.13)就可以求出晶界扩散系数 。

。

3.3.溶质对晶粒间界扩散的影响

在薄膜元件金属化的可靠性和损坏过程中,添加的溶质对晶粒间界中溶剂原子扩散过程的影响具有特别重要的意义。在元件中,为了达到例如增加衬底的粘附力这样目的而进行多级金属化,或为了例如防止腐蚀和金属成分之间的相互扩散而设置阻挡层。就是通过这些阻挡层发生溶质效应的。为了改善其特殊的性质,有时把溶质直接掺合到薄膜中去。但是并不是所有的溶质都减小晶粒间界的扩散的,纵观这方面的资料,可能遇到许多可能的趋向:某些减小晶粒间界的扩散,另一些则增加扩散,而在某些情况下又没有可测量到的效应[90]。

溶质使固体中晶粒间界能降低的作用是早已经知道的,并已由默尔和杭德罗斯在热力学德基础上进行了讨论。麦克莱恩针对固体中平衡的晶粒间界偏析推导了下列方程式

Cb=C0exp( )/[1+ C0exp(

)/[1+ C0exp( )] (3.14)

)] (3.14)

式中 Cb是晶粒间界中的溶质浓度,C0是晶格中的溶质浓度; 则是由此派生的、溶质在晶粒间界和晶格位置上的结合自由能之差。杭德罗斯把吉布斯能的降低定理和式(3.11)相结合,得到

则是由此派生的、溶质在晶粒间界和晶格位置上的结合自由能之差。杭德罗斯把吉布斯能的降低定理和式(3.11)相结合,得到

γbp-γb=RTφln[1+ C0exp( )] (3.15)

)] (3.15)

式中γbp是纯溶剂金属的晶粒间界能;φ取决于晶粒间界渗透饱和的程度,取其为1。

为了解释所报导的添加溶质对晶粒间界扩散的各种效应,把式合并,取晶粒间界饱和系数等于1,并把各项重新排列,得到

[( )(

)( )]1/2 -1=C0exp(

)]1/2 -1=C0exp( ) (3.16)

) (3.16)

3.3.1溶质在高温时增加晶粒间界扩散

因为对于低浓度合金总能满足C0≤1,所以在一些高温情况时式(3.16)中的右端乘积足够小,因而可以忽略。这样,式(3.16)简化为

( ) (

) ( )≈1 (3.17)

)≈1 (3.17)

如果 始终比

始终比 大,那末将要求

大,那末将要求 小于

小于 ,这是一种情况;在高温时,合金中的晶粒间界扩散和纯金属中的相比是增加了,但是此效率只能在有限的温度范围内才适用。因为比值本身是随温度增加而下降,进而趋近于1。

,这是一种情况;在高温时,合金中的晶粒间界扩散和纯金属中的相比是增加了,但是此效率只能在有限的温度范围内才适用。因为比值本身是随温度增加而下降,进而趋近于1。

3.3.2溶质在低温时减小晶粒间界的扩散

在温度较低时,即使在低浓度合金中C0≤1,但乘积C0exp( )≥1因此,虽然

)≥1因此,虽然 也不大可能大到足以满足关系式,显然,要求

也不大可能大到足以满足关系式,显然,要求 >1,所以,其结果是由于添加了溶质,溶剂的晶粒间界扩散减小。

>1,所以,其结果是由于添加了溶质,溶剂的晶粒间界扩散减小。

当然,以上讨论的效应之间应该存在着一个没有作用的区域,因为它们之间有交叉。

一般说来,溶质对晶粒间界扩散的各种效应的作用系数,可以设想就是溶质-晶粒间界的相互作用系数( Ea和

Ea和 Sa),以及在晶格中和在晶粒间界中的自体扩散参数,也就是说纯金属和合金溶剂的

Sa),以及在晶格中和在晶粒间界中的自体扩散参数,也就是说纯金属和合金溶剂的 、

、 、

、 、

、 。因此在这些信息并不完全适用的情况时,就没有可能广泛地、可靠地预测溶质效应。而且可以想象,能够探测到这些效应的温度范围也将受到玷污杂质和薄膜生长条件地影响。

。因此在这些信息并不完全适用的情况时,就没有可能广泛地、可靠地预测溶质效应。而且可以想象,能够探测到这些效应的温度范围也将受到玷污杂质和薄膜生长条件地影响。

3.4.铜薄膜中铜原子层间的扩散失效

在常规的具有阻挡层的铜互连结构线中,铜原子层间扩散的机理[92-93]是铜原子通过铜薄膜和介质层的界面中存在晶粒边界或空洞等缺陷穿过界面,到达硅表面,首先在界面形成积累,随着铜原子的增多,再进一步扩散到硅体内,引起器件性能的下降。铜原子层间扩散主要是通过界面扩散,当然晶格扩散也起着破坏性的作用。因此必须防止铜污染。其中一种方法即是寻找一种能够阻止铜向硅或二氧化硅中扩散的扩散阻挡层将铜互连线包起来。铜原子的扩散能力和铜互连线微观结构关系紧密。特别是晶粒尺寸及均匀性和互连线的晶体学结构取向对铜互连线的抗电迁移和应力迁移能力有决定作用。晶粒尺寸越大,如果晶界大于互连线的宽度,形成竹节结构,将大大降低电迁移时金属离子沿晶界扩散的能力。晶粒尺寸的均匀性提高,有利于防止原子扩散时空洞和小丘等缺陷的形成。铜互连线薄膜中如果存在织构,例如{111}织构膜有较强的抗电迁移性能。而对于铜原子向二氧化硅和硅中的扩散,合适的扩散阻挡层可以有效的防止铜原子的层间扩散。目前集成电路工艺中防止铜的扩散都是用覆盖一层扩散阻挡层的方法,这个工艺工时长、成本高、而且阻挡层本身也会与硅基底发生反应、扩散等。当然尽管这些工艺在最近5年迅速发展,但是对于它们的深入基础理论的研究还不够,特别是从材料科学的领域还可以进行大量研究工组。

4.铜互连膜合金化的研究现状

由于阻挡层在铜互连工艺上的限制性,人们就在努力寻求另一种有效的方法,以期能够取代扩散阻挡层的应用。合金化作为常用的改善材料性能的方法,也成为一种潜在的有效提高界面结合力以及阻止铜硅互扩散的方法,引起了越来越多的人的关住。

众所周知,合金元素的作用是多方面的。但一般说来,合金元素在固溶体中的都能起到强化的作用的。在铜互连薄膜中,合金元素的选取一般要满足以下几个原则:(a) 有很好的抗腐蚀能力,能够保护铜不被氧化;(b) 能够提高Cu膜的力学性能;(c) 能提高Cu膜的抗电迁移能力;(d) 使Cu膜的电阻率增加不多。可供选择的合金元素有:Al[94],Mg[95],Zr[96],Cr[97],B[98]等。前人对这些合金元素的作用都进行了详细的研究和报道。选择Al、Mg的原因在于是它们使电阻率增加不多,更重要得是能够在退火处理后在Cu膜表面形成一层致密的氧化膜,因此具有非常好的抗氧化性能[94][95]。Lanford[98]采用离子注入B的方法来合金化Cu膜,结果表明合金膜的抗氧化能力明显增强。选择Zr、Cr的优点在于它们与Cu的固溶度非常小,Zr在Cu中的500 ℃溶解度小于0.01at%[96]。Cr在室温与Cu不互溶,1075 ℃下Cr在Cu中的溶解度约为0.8%[97]。由于它们与Cu的固溶度非常小,而沉积态的合金膜是一种亚稳的、过饱和的结构,在退火处理过程中Zr、Cr原子将从Cu基体析出,向晶界、界面、表面扩散,这可以显著降低合金膜的电阻率。文献[96]表明合金元素在晶界、界面、表面处的积累能够极大地提高合金膜的抗电迁移能力。

我们注意到采用A1、Mg作为合金元素的优点和Zr、Cr的优点不同。两者的电阻率都比较低,采用A1、Mg作为Cu的合金元素的优点在于抗氧化能力比较强,而采用Zr、Cr的Cu合金有很好的抗电迁移能力。集成电路制造过程中一般须经过较高温度退火处理,降温时易在薄膜内形成很大的热应力,往往导致薄膜形成孔洞、小丘、断裂或者与基体脱落[99]。文献[100]表明Zr、Cr原子在晶界、表面、界面的分布可以对薄膜起到强化作用,同时Zr、Cr可以优先与氧发生反应。

关于合金溶质元素对薄膜晶界扩散(包括抗电迁移性能),薄膜的微观结构,薄膜热稳定性的影响,前人也进行了一定程度的研究。D. Gupta等人的一项研究表明[101],1.2at%Ta的添加对Au薄膜的低温(204 ℃~395.5 ℃)下的点阵扩散以及晶界自扩散有着深刻的影响:随着合金溶质元素的加入,点阵扩散的激活能减小,扩散系数增大;而晶界扩散的激活能增大,扩散系数减小。这可能与溶质原子的跳动,晶界的分割以及激活能的增大有关。并且对晶界扩散的激活能以及晶界扩散和溶质元素晶界偏聚的相互作用进行了计算[102]。W. H. LEE,Y. K. KO[103]等对Cu(Mo)/SiO2/Si,以及Ti/Cu(Mo)/SiO2/Si多层膜系统的微观组织结构进行了研究。结果表明,Cu(Mo)合金膜在退火过程中发生Cu、Mo分离现象,Mo向膜的外表面扩散,导致无Mo的Cu膜形成,并且晶粒长大,薄膜呈现强烈的(111)织构;而在Ti/Cu(Mo)/SiO2/Si结构中,由于Ti的阻挡作用,没有出现分离现象,而织构依然存在。同样,在Y. K. KO,J. H. HANG等的研究[104]中,Cu(Mo) Cu(Ag)合金膜在退火过程中溶质元素向表面扩散,(111)织构明显。这可能是由于Cu-Mo,Cu-Ag与是不互溶合金系统,无端际固溶体,因此元素Mo、Ag在Cu膜的晶界偏聚,增大了界面能。在退火过程中合金元素扩散减小应变,并且出现(111)织构以减小系统能量。而(111)织构对金属离子的扩散有很大的影响。然而,C. H. Lin,J. P. Chu[105]的研究认为溶质元素W的添加之所以提高了Cu合金膜的热稳定性,减小了Cu、Si的互扩散可能是由于一方面合金元素W的加入提高了Cu层错能,减小了薄膜内的孪晶缺陷,从而减小了Cu向Si中的扩散;另一方面合金元素W的加入提高了硅化物的形成激活能。

近来,M. J. Frederick 和G. Ramanath[106]对Cu-(5at%-12at%)Mg/SiO2结构进行了研究。结果表明,合金膜在退火过程中发生Mg向膜/基底界面的偏聚,并且在界面处的SiO2处发生发应,形成MgO。随着MgO的形成,薄膜电阻增大,但这一氧化物层的形成提高了Cu和SiO2的界面结合力,并且减少了Si向Cu中的扩散。他们的研究认为这是由于提高了Si向Cu扩散的激活能。

综上分析可知,在薄膜中通过对一些主要的扩散通道如晶界、界面等的控制,可以有效地控制薄膜中原子的扩散过程,其中最主要的方法即是合金化。可以设想,在铜膜中加入超过低温固溶度的含量的某些合金元素,以在晶界、晶粒内部或者其它界面形成溶质元素的沉积物,从而阻止铜的扩散。这样,合金元素需要满足一下几点要求[96]:

1.合金元素需要能够在较低的温度下形成沉积物。考虑到集成电路的应用,沉积温度应该在500℃以下。

2.合金元素的固溶度应该足够小,以保证在低温退火过程中在晶界、表面和界面处形成足够的沉积物。

3.退火后的铜合金电阻率必须小于Al的电阻率(<3μΩ·cm)。

5.本课题的研究思想、研究目标和研究内容及可行性分析

5.1.本课题的研究思想

目前集成电路工艺中防止铜的扩散都是用覆盖一层扩散阻挡层的方法,但正如前所述,由于对扩散阻挡层的性能要求越来越高,致使这个工艺工时长、成本高、而且阻挡层本身也会与硅基底发生反应、扩散等。本项目提出合金化方法即在纯铜中加入少量其它合金元素形成铜合金,在不降低(或少降低)导电率的前提下,降低铜在硅中的扩散能力,其目的是取消扩散阻挡层或者减薄扩散阻挡层。这具有一定的理论基础。首先根据现有的扩散理论,金属的自扩散激活能与点阵中原子间的结合力(即键力)有关:金属熔点越高,原子间的结合力越强,则原子越不容易离开其平衡位置,因而自扩散激活能越大。如果添加元素溶入到溶剂金属铜基体,使得铜合金的熔点升高,则可以预想能够减小铜的扩散系数。根据铜合金相图,Pt、Rh、Pd、Ni等合金元素均是满足这一要求的合适添加元素。这也就是铜合金化对扩散影响的基本理论依据之一。其次,在另一方面来说,根据晶界扩散模型,结合以上的研究结果,可以设想在互连铜膜中添加不互溶合金元素如Cr、Mo、W、Nb等,由于这些元素与Cu不形成端际固溶体,这样在退火过程中就可能会在合金膜的晶界处偏析,从而能够在不明显降低合金膜电导率的情况下显著降低晶界扩散系数,减小铜向硅中的扩散(或铜、硅的互扩散)。

5.2.研究的内容、研究目标及拟解决的关键问题

研究薄膜态铜和硅之间的相互扩散机理,重点在晶界扩散所起的作用。通过理论计算和实验分析探索降低铜在硅或者扩散阻挡层介质中扩散能力的途径,为取消或减薄现行扩散阻挡层提供理论依据。

通过理论计算和实验分析研究下列问题

1.薄膜状态铜和硅之间的相互扩散问题-体扩散和晶界扩散

作为系统研究,研究内容包括铜在硅中的扩散、硅在铜中的扩散,但铜在硅中的扩散为重点。既涉及体扩散也涉及晶界扩散,以晶界扩散为重点。所以着重探讨材料不同结晶状态(多晶、单晶、非晶)对扩散的影响,其目的是探讨晶界扩散的作用。

a) 单晶硅和不同状态铜(多晶 非晶)之间的扩散

b) 多晶硅和不同状态铜(多晶 非晶)之间的扩散

c) 非晶硅和不同状态铜(多晶 非晶)之间的扩散

2.薄膜铜和作为阻挡层介质材料之间的扩散

选用重金属W、Mo、Ta及其氮化物作为阻挡层介质

3.合金化对铜在硅中扩散的影响

在纯铜中加入微量元素,在不改变或少量增加电阻率的前提下,研究合金化铜在硅中的扩散情况,力图降低铜在硅中的扩散能力。

拟解决的关键问题

1.由于薄膜厚度是在纳米或微米数量级,因此要详细计算这段扩散距离中的所有和扩散有关的数据,但计算所需的各个参数不全,必要时要自己做实验求得参数。

2.研究合金化对铜在硅中扩散能力影响时,铜合金溅射薄膜的获得,包括溅射用合金靶的制备都是要解决的关键问题。

3.实验过程中,要测定薄膜内元素的分布及表面反应产物的分析,在透射电镜和Auger能谱分析方面,特别是在试样制备上都有相当难度。

拟采取的研究方案及可行性分析

研究方案 包括理论计算和实验操作两部分

1)理论计算:研究铜在硅和阻挡介质层(如MOWTA及其氮化物)中的扩散规律,根据铜硅相图、热力学和动力学一些基本原理进行分析,计算不同温度下铜在硅及其它介质层中的扩散能力。

分别计算体扩散和晶界扩散,并比较二者之间的差别。

根据薄膜特点,重点计算扩散距离在纳米或微米数量级时扩散数据。

理论计算的技术路线为:

计算公式的选择-所用参数确定-具体计算-结果评价

2).实验操作:为简化操作工艺,所有薄膜均采用PVD溅射制备,然后用透射电镜和Auger能谱仪分析铜元素在介质界面的分布状态,从而得到有关扩散的数据。

-材料结晶状态对扩散性能的影响

基底单晶硅上溅射铜得到单晶硅和非晶铜的扩散组合

基底单晶硅上溅射铜再退火,得到单晶硅和多晶铜扩散组合

用非晶、多晶硅作基重复上述两过程

-合金化对铜在硅中扩散性能的影响

在单晶硅基底上溅射合金化后的铜膜(采用合金铜靶溅射)

铜在扩散阻挡层介质(重金属、氮硅化物)中的扩散

单晶硅基底上先溅射一层阻挡层介质再溅射一层铜

在上述扩散薄膜制备后,再进行微观分析,分析界面处铜元素的分布以及界面反应产生的铜的化合物。

实验操作的技术路线:

溅射靶材制备-用溅射法制备各种要求的薄膜-界面处铜元素的微观分析

可行性分析

在理论计算方面,体扩散基于Fick第一和第二扩散定律的扩散方程时比较经典的,子晶界扩散上基于Fisher理论的计算也是成熟的,因此计算整体上还是可行的。在试验操作方面,关键是透射电镜试样的制备,溅射制备出合格的薄膜试样,其他分析都是可进行的。而利用现有的最新技术还是可以制备出这类试样。

添加元素(合金化)来降低铜在硅中的扩散能力的机理是:通过合金化增加点阵中原子件的结合力,使扩散激活能增大,以降低原子扩散系数。目前在Cu-Pd、Cu-Au合金系中已证明如果添加合金元素溶入到溶剂金属之后能使熔点升高,则其中原子扩散系数会减小。因此我们在纯铜中可以通过合金化来降低铜的扩散系数。

本项目的特色与创新之处

项目特色

本项目是根据集成电路中最新的铜互连和原子层沉积工艺中存在的问题提炼出其科学本质-铜在薄膜中的扩散,从材料科学角度对二维薄膜材料的扩散进行深入研究,为集成电路制造提供理论支持。

创新之处

1.通过分析单晶、多晶和非晶态基底与上层薄膜中的扩散现象,研究晶界扩散在薄膜材料中的重要性。

2.提出通过合金化来改变铜在硅中扩散能力的设想,扩大了金属作为功能材料使用时的合金设计思路。

6.年度研究计划及预期研究结果

年度研究计划

2005.3-2005.12计算在不同温度下Cu在Si中的扩散能力,包括体扩散,晶界扩散。如果有些参数不能找到,则要做实验确定参数。溅射试验所用靶材的制备,包括纯铜靶、铜合金靶以及硅化物靶。根据现有集成电路中的铜互连工艺状况,确定我们相应的溅射工艺。

2006.1-2007.1铜薄膜以及铜合金薄膜的溅射,包括在单晶硅上直接溅射纯铜膜以及铜合金膜得到单晶硅-非晶铜或者铜合金膜的结合,经过退火处理得到单晶硅-多晶铜以及铜合金膜的结合。测定铜合金薄膜的导电(电阻)性能。综合比较纯铜薄膜和铜合金薄膜的导电性和扩散性能。然后用透射电镜和Auger能谱仪进行观察分析。着重分析Si基体中铜元素的分布状况,界面出合金元素的分布状况以及铜和硅表面生成金属间化合物的状况。用Auger能谱仪分析不同深度Cu元素的分布。

2007.1-2007.9分析试验结果,建立纯铜膜以及铜合金膜在硅中理论扩散模型,用Fick体扩散以及Fisher晶界扩散模型解对铜在硅中的元素深度分布进行拟合,找出扩散的规律。结合各合金元素在薄膜中的存在形式分析其对铜硅互扩散的影响。

7.目前的初步研究结果

由于根据报道,合金元素的添加能够显著影响铜互连薄膜的电阻,如图7.1所示。

图7.1 合金元素(1at%)对铜电阻率的影响

Fig.7.1 Influence of Solute Elements (1at%) on the Resistivity of Copper

因此根据合金化思想及上述的3个选取原则,我们初步选取Cr、Mo、Nb、Ni合金元素作为研究对象,对其单元合金化甚至二元及多元合金化薄膜进行系统的研究,并与纯铜膜进行对比,研究在单晶硅以及多晶硅中的扩散规律。

1.靶材的制备

制备正混和热(△H>0)的合金体系的亚稳态合金比制备负混和热(△H>0)体系的亚稳态合金要困难的多(如Cu-W薄膜的△H>35.5KJ/mol、Cu-Mo薄膜的△H>28KJ/mol),因而采用常规合金熔炼的方法很难制备高熔点,难溶合金(Cu-Cr、Cu-Mo等)薄膜。因此,我们采用将原子百分比换算为面积百分比的方法,结合溅射靶材中的具体数据制备简易的合金靶材。合金靶材示意图如图7.2所示。

图7.2 合金靶示意图

Fig 7.2 The sketch map of Cu-M (Metal) alloy target

2.合金薄膜的成分、结构表征

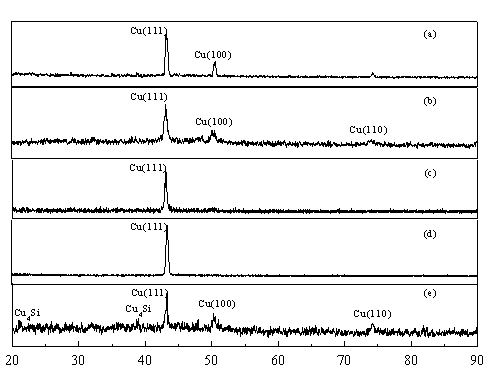

作为第一阶段的研究,我们设计了名义成分为Cu-2at%Cr、Cu-2at%Mo、Cu-2at%Nb、Cu-2at%Ni合金成分。目前,对于单晶硅(Si(100))上的Cu-Cr、Cu-Mo薄膜的能谱分析结果表明:名义成分为Cu-2at%Cr的合金薄膜实际成分约为Cu-1.26at%Cr、Cu-2.18at%Mo。

目前,对单晶硅上磁控溅射纯铜膜以及Cu-2.18at%Mo合金膜的x-射线研究结果表明,原沉积Cu膜在室温下溅射呈现多晶结构,在经过400℃真空退火后,有铜硅化合物出现。而原沉积的Cu-2.18at%Mo合金膜以及在经过400℃低温真空退火后,具有强烈的(111)织构,如图7.3所示。这与W.H.LEE,Y.K.KO等[103]以及Y.K.KO,J.H.JANG等[104]人的研究结果是一致的。众所周知,由于面心立方结构的(111)面为密排面,原子结合紧密程度高,因此这将很可能影响铜硅间的互扩散。当温度上升到530℃时,Cu-2.18at%Mo合金膜出现了铜硅化合物。

3.薄膜厚度表征

采用表面轮廓仪对初步得到的纯铜膜、Cu-1.26at%Cr、Cu-2.18at%Mo薄膜的厚度进行测量。测量结果表明薄膜厚度约为326nm。

4.薄膜电阻测量

用QJ84数字型直流电桥,采用改进型Van der Pauw法对薄膜电阻进行测量。测量结果表明,合金膜的电阻增大很大,与文献报道有很大差异,这可能与此次薄膜厚度太薄有关。在随后的实验中应对实验参数进行改进。

参考文献

1. 李志坚,周润德. ULSL器件、电路与系统. 科学出版社,1987:24-38

2. K. Rahamat,O.S. Nakagawa,et al. A Scaling Scheme for Interconnect in Deep-Submicron Process. International Electron Devices Meeting Technical Digest,1995:245-248

3. 吴德馨. 迈向二十一世纪德集成电路. 世界科技研究与发展,1999,21(4):1-4

4 刘平. 铜基集成电路引线框架材料发展概况. 材料开发与应用,1998,13(3):39-41

5 徐蕸生. MOS数字大规模及超大规模集成电路. 清华大学出版社,1990:59-77

6 P.A. Gargini,C.Tseng and M.H. Woods. IEEE/PROC,IRPS. 1989:66

7 Microconductor international. 铜互连工艺. Applied Material China. 2004

8 S. C. Sun. Process Technologies for Advanced Metallization and Interconnect Systems. Iedm,1993:97-765

9 S. P. Murarka. Multilevel interconnections for ULSA and GSI era. Materials Science and Engineering,1997,R19,87-151

10 J. R. Lloyd,J. Clements,et al. Copper Metallization Reliability. Microelectronics Reliability,1999,39. 1595-1602

11 C–K. Hu,J. M. E. Harper. Copper Internationals and Reliablity. Materials Chemistry and Physics,1998,52,5-16

12 吴**. 国家自然基金申请书.

13 J. Torres,J. L. Mermet,et al. Copper Based Metallization for ULSI Circuits. Solid State Technology,1998,10,119-120

14 D. Edelstein,J. Heidenreich,et al. Full Copper Wiring in a Sub-0.25μm CMOS ULSI Technology,International Electron Devices Meeting Technical Digest,1977,773-776

15 S. P. Murarka. Proceedings of the Workshop on “Tungsten and Other Advanced Metals for ULSI Appications 1990”. Ed. by G. C. Smith and R. Blunarthal. MRS, Pittsburgh, PA, 1991,179

16 S. P. Murarka. In the Proc of Int Conf. On Adv. Microelectronic Devices and Processing (Tohoku Univ.,Sendai Japan),1994,March 3-5,321

17 S. P. Murarka,R. J. Gutmann,A. E. Kaloyeros and W. A. Landford. Advanced multilayer metallization schemes with copper as interconnection metal. Thin Solid Film,1993,236,257

18 S. Venkatesana,A. V. Gelatos. A High Performance 1.8 V 0.20μm CMOS Technology with Copper Metallization. IEDM,1997,769-773

19 R. Gonella. Key Reliablity Issuues for Copper Integration of Damascene Architecture. Microelectronic engineering,2001,55,245-255

20 Alvin L.,S. Loke. Kinetics of copper drift in low-k polymer interlevel dielectrics. IEEE Transaction Electronics,1999,11(146),11-16

21 杨振良,徐可为.硕士学位论文. 西安交通大学. 20030401

22 Jackson R. L.,Broadbent E.,Cacouris T,et al. Proceeding and Integration of Copper Interconnects. Solid State Technology,1998,41(3),49

23 翁寿松. 铜布线及其设备[J]. 电子工业专用设备,1999,3,13

24 Ronald J. Gutmann,T. Paul Chow,et al. Copper Metallization Manufacturing Issues For Future ICS. Mat. Res. Soc. Symp. Proc.,1994,337,41-57

25 Hu. C-K,Luther B.,Kaufman F. B.,et al. Copper Interconnection Intergration and Reliability.[J] Thin Solid Films,1995,262,84-92

26 Terry L. Alford,et al. Copper-based Metallization and Interconnections for Ultra-Large-Scale Intergration Applications. Thin Solid Films,1995,262,ⅶ-ⅷ

27 Popov K. I.,Kostic T. M.,Nikolic N. D.,et al. A New Approach to Metal Electrodeposition at a Periodically Changing Rate,Part I the Reversing Overpotential Method[J]. J Electroanalytical Chemistry,1999,464(2),245-251

28 R. Rosenberg,D. C. Edelstein,C-K. Hu.,et al. Copper Metallization for High Performance Silicon Technology. Annu. Rev. Mater. Sci.,2000,30,229-262

29 陈智涛. 集成电路片内铜互连技术的发展. 微电子学. 2001,24,4

30 翁寿松. 90nm工艺及其相关工艺. 微纳电子技术. 2003,40(4),32

31 L. M. Gignac,K. P. Rodbell,C. Cabral,et al. Characterization of Plated Cu Thin Film Microstructures. Mat. Res. Soc. Symp. Proc,Vol.564,373-378

32 D. Weiss,O. Kraft and E. Arzt. Microstructural Development of Dispersion Strengthened Cu Thin Films. Mat. Res. Soc. Symp.Proc,Vol.564,259-364

33 J. M. E. Harper,C. Cabral J. R.,P. C. Andricacos,et al. Mechanism for Microstructure Evolution in Electroplated Copper Thin Films. Mat. Res. Soc. Symp. Proc,Vol.564,387-392

34 W-M. Kusche,A. Kreschman and R-M. Keller Texture of Thin Films. J. Mater. Res.,1998,Vol.13,No.10,2962-2968

35 D. P. TRACY and D. B. KNORR. Texture and Microstructure of Thin Copper Films. Journal of Electronic Materials,1993,Vol.22,No.6,611-616

36 P. Chaudhari,S. Mader and J. F. Freedman. Mechanisms of Stress Relief in Thin Films. J. Vac. Sci. Technol, 1969,Vol.6,No.4,618-621

37 Shute. C. J.,et al. Determination of Yielding and Debonding in Al-Cu Thin Films from Residual Stress Measurement via Diffraction. J. Mater. Res,1991,6,950

38 M. A. Korhonen,W. R. Lafortaine,et al. Stress-Induced Nucleation of Void in Narrow Aluminum-based Metallization on Sillicon Substrates. J. Appl. Phys.,1991,70(11),6774-6781

39 Hidekazu Okabayashi. An Analytical Open-Failure Lifetime Model for Stress-Induced Voiding in Aluminum Lines. IEEL transactions on electron devices,1993,40(4),782-788

40 罗东 钟涛兴. ULSI铜互连线微观结构和应力研究. 硕士学位论文(TN47),北京工业大学 20050201

41 Thompson,Carl V. Stress and Grain Growth in Thin Films. Journal of the Mechanics and Physics of Solids,1996,Vol.44,No.5,657-673

42 R. Jakkaraju,A. L. Greer. Texture and Hillocking in Sputter-deposited Copper Thin Films. Journal of Materials Science:Materials in Electronics,2002,13,285-294

43 Young-Chang,Joo Soo-Jung,Hwang and Hyun Park. The Effect of Grain Boundary Characteristics on Microstructure and Stess Void Evolution in Electroplated and Sputtered Cu Films. Materials Science Forum,2003,vol.426-432,3481-3486

44 R. Rosenberg,A. F. Mayadas and D. Gupta. Grain Boundary Contribution to Transport. Surface science,1972,31,566-585

45 H. M. Breitling and R. E. Hummel. Electromigration in Thin Sliver, Copper, Gold, Indium, Tin, Lead and Magnesium Films. J. Phys. Chem. Solids.,1972,Vol.33,845-852

46 F.M.D’HEURLE AND A. GANGULEE Electrotransport in Copper Alloy Films and The Defect Mechanism in Grain Boundary Diffusion. Thin Solid Films,1975,25,531-544

47 Gian Luigi and Andrea Scorzoni. Interaction Between Electromigration and Mechanical-Stress-Induced Migration:New Insight by a Simple,Wafer-Level Resistometric Technique. IEEE transaction on electron devices,1991,38(3),465-479

48 R.Rosenberg,Inhibition of electromigration damage in thin films. The Journal of Vacuum Science and Technology,1997,Vol.9,No.1,263-270

49 C-K. Hu. Electromigration Failure Mechanisms in Bamboo-Grained Al(Cu) Interconnections. Thin solid films,1995,260,124-134

50 Hu. C.-K.,Lee K.Y.,et al. Electromigration Drift Velocity in Al-Alloy and Cu-Alloy Lines. Journal of the Electrochemical Society,1996,Vol.143,No.3,1001-1006

51 J. Bardeen,W. H. Bratton and W. Schockley. Journal of Chemical Physics,1946,14,714

52 S. P. Murarka,J.M.Neirynck,et al. Copper Interconnection Schemes: Elimination of the Need of Diffusion Barrier/Adhesion Promoter by the Use of Corrosion-Resistant Low-resistivity-doped Copper. Proceedings of SPIE - The International Society for Optical Engineering,1994,2335,80-90

53 Jian Li and J. W. Mayer,E. G. Colgan. Oxidation and Protection in Copper and Copper Alloy Thin Films. Journal of Applied Physics,1991,Volume 70,Issue 5,2820-2827

54 Itow,Y. Nakasaki,et al. Self-aligned Passivation on Copper Interconnection Durability Against Oxidizing Ambient Annealing. Applied physics letter,1993,63,934

55 P. J. Ding,W. A. Lanford,S. Hymes and S. P. Murarka. Annealing of Boron-implanted Corrosion Resistant Copper Films. Journal of Appiled Physics,1994,74,1331

56 P. J. Ding, W. Wang, and W. A. Lanford. Thermal Annealing of Buried Al Barrier Layers to Passivate the Surface of Copper Films. Applied Physics Letters,1994,Volume 65,Issue 14,1778-1780

57 W. A. Lanford,P. J. Ding,W. Wang,S.Hymes,S. P. Muraka. Low-temperature Passivation of Copper by Doping With Al or Mg. Thin solid films,1995,262,234-241

58 W. A. Lanford,P. J. Ding,W. Wang,S.Hymes,S. P. Muraka. Surface and Interface Modification of Copper for Electronic Application. Materials Research Society Symposium – Proceedings,337,217-224

59 王晓震,王二敏,赵新清. 离子注入铜膜后的氧化行为. 航空材料学报,1999,Vol.19,No.4,22-26

60 Gas P. and Bernardini. J. Surf. Sci.,1978,72,365

61 Ching-Yu Yang,J. S. Jeng,J. S. Chen,Grain Growth Agglomeration and Interfacial Reaction of Copper Interconnects. Thin Solid Films,2002,420/421,398-402

62 J. S. Reid,R. Y. Liu,Paul Martin,et al. W-B-N diffusion Barriers for Si/Cu Metallizations. Thin Solid Films,1995,262,218-223

63 A. Kohn,M. Eizenberg,et al. Evaluation of electroless deposited Co(W,P) thin films as diffusion barriers for copper metallization. Microelectronic Engineering,2001,55,297–303

64 刘洪图,吴自勤. 超大规模集成电路的一些材料物理问题(ⅰ)-Cu互连和金属化. 物理,2001,30(12),757-761.

65 Steven Smith,Wei-Min Li,Kai-Erik Elers,Klaus Pfeifer. Physical and Electrical Characterization of ALCVDTM TiN and WNxCyused as a Copper Diffusion Barrier in Dual Damascene Back End Structures (08.2). Microelectronic Engineering,2002,64,247–253

66 M. Moriyama,T. Kawazoe,M. T. anaka. M. Murakami. Correlation Between Microstructure and Barrier Properties of TiN Thin Films Used Cu Interconnects Thin Solid Films,2002,416,136-144

67 S-H Kim,S. S. Oh,et al. Atomic-layer-deposited WNxCy Thin Films as Diffusion Barrier for Copper Metallization, Appl. Phys. Lett.,2003,21,4486

68 陆华,屈新萍等. 超薄W-Si-N作为铜和硅之间的扩散阻挡层. 半导体学报,2003,24,612-615。

79 Z.L.Yuan, D.H.Zhang, C.Y.Li et al. A New Method for Deposition of Cubic Ta Diffusion Barrier for Cu Metallization. Thin Solid Film.434 (2003)126-129

70 Z.W.Yang, D.H.Zhang, C.Y.Li et al. Barrier Layer on Reliabilities of Copper Metallization. Thin Soild Films. 462-463 (2004)288-191

71 S. W. Loh,D. H. Zhang,C. Y. Li,et al. Study of Copper Diffusion into Ta and TaN Barrier Materials for MOS Devices. Thin Solid Films,2004,462-463,240-244

72 K. N. Tu,R. Rosenberg. Mass Transport in Layered Polycrystalline Thin Films. Thin Soild Films, 1972,13,163-167

73 C. W. Nelson. Proc. Int. Symp. Hybid. Microelectronics,1969,431.

74 M-A. Nicolet. Diffusion barriers in thin film. thin solid films,1978,52,415-443

75 J. S. Reid,E. Kolawa,C.M.Garland. Amorphous (Mo Ta or W)-Si-N diffusion barriers for Al metallization,Journal of Appiled Physics,79(2),1109-1115

76 A. E. Kaloyer,E. Eisenbraun. Ultrathin diffusion barriers/liners for Gigascale copper metallization Annual Review of Materials Science.,2000,30,363-385

77 Soo-Hyun Kim, Su Suk Oh, et al. Atomic-layer-deposited WNxCy Thin Films as Diffusion Barrier for Copper Metallization. Applied Physics Letters, Volume 82,Issue 25,4486-4488

78 C. Weaver. in Physics of thin films, Vol.6,M.H.Francombe and R.W.Hoffman, Eds., Acadenic Press, New York,1971

79 P. A. Turner. Thin-film Diffusion-Review. The Journal of Vacuum Science and Technology,Vol.9,No.1,262

80 Eick. R. Weber. Transition Metals in Silicon. Appl. Phys.A:30,1983,1-22

81 R. N. Hall, J. H. Racette. Diffusion and Solubility of Copper in Extrinsic and Intrinsic Germanium, Silicon, and Gallium Arsenide. J. Appl. Phys.,1964,Vol.35,No.2,379-391

82 K. Nakashima,M. Iwami and A. Hiraki. Low Temperature Diffusion of Au into Si in the Si (substrate)-Au (film) System. Thin Solid Film,1975,25,423-430

83 D. Gupta. Diffusion in Several Materials Revelant to Cu Interconnection Technology Materials Chemistry and Physics,1995,41,199-205

84 A. A. Istratov,E. R. Weber. Electrical Propertities and Recombination Activity of Copper, Nickel and Cobal in Silicon. Appl. Phys. A 66,1998,123-136

85 Andrei A. Istratov,Christoph Flink,et al. Intrinsic Diffusion Coefficient of Interstitial Copper in Silicon. Physical Review Letters,1998,Vol.81,No.6,1243-1246

86 W. P. Gillin,D. J. Dunstan. Diffusion in Semiconductors. Computational Materials Science,1998,11,96-100

87 A. A. Istratov,C. Flink,et al. Diffusion, Solubility and Gettering of Copper in Silicon. Materials Science and Engineering B72,2000,99-104

88 Andrei A. Istratov and Eicker R. Weber. Physics of Copper in Silicon. Journal of the Electrochemical Society,2002,149 (1),G21-G30

89 H. Bracht. Copper Related Diffusion Phenomena in Germanium and Silicon. Materials Science in Semconductor Processing,2004,7,113-124

90 J. M. 波特,K. N. 杜,J. W. 迈耶等著. 张永康 译. 国防工业出版,1983,304

91 金属中的扩散 夏立芳,张振信 编著. 哈尔滨工业出版社,1989,130-134

92 J. Baumann,et al. W/TiN Double Layers as Barrier System for Use in Cu Metallization. Microelectronic Engineering,1997,(37/38) 229-236

93 S.C.Sun,et al. CVD and PVD Transition Metal Nitrides as Diffusion Barriers for Cu Metallization. 1998 5th International Conference on Solid-state and Intergrated Circuit Technology Proceedings,1998,243-246

94 P. J. Ding,W. A. Lanford,S. Hymes,S. P. Muraka. Effect of the Addition of Small Amounts of Al to Copper: Corrosion, Resistivity, Adhension, Morphology, and Diffusion. J. Appl. PHYS. 1994,75,3627-3631

95 P. J. Ding,W. A. Lanford.. Oxidation Resistant High Conductivity Copper Films. Appl. Phys. Lett.,1994,64,2897-2899

96 Y. Lgarashi,T.Ito. Electromigration Properties of Copper-Zirconium Alloy Interconnect. J. Vac. Sci. Technol. B16,1998,2745-2750

97 C. Cabral,E. Harper,K. Holloway,D. A. Smith,R. G.. Schad. Preparation of Low Resistivity Cu-1 at.%Cr Thin Film By Magnetron Sputtering. J. Vac. Sci. Tech. A10,1992,1706-1712

98 P. J. Ding,W. A. Lanford. Annealing of Boron-impalnted Corrosion Resistant Copper Films. J. Appl. Phys.,1993,74,1331-1334

99 M. D. Thouoless. Nodeling the Development and Relaxation of Stresses in Films. Annu. Rev. Mater. Sci. 1995,25,69-96

100. E. Arzt,W. D. Nix. Model for the Effect of Line Width and Mechanical Strength on Electromigration Failure of Interconnects With “Near-bamboo” Grain Structures. J. Mater. Res.,1991,6(4),731-736

101 D. Gupta and R. Rosenberg. Effect of a Solute Addition (Ta) on Low Temperature Self-diffusion Process in Gold. Thin solid films,1975,25,171-180

102 D. Gupta. Grain-boundary Energies and Their Interaction With Ta Solute From Self-diffusion in Au and Au-1.2at%Ta Alloy. Philosophical Magazine,1976,Vol.33,No.1,189-197

103 W. H. LEE,Y. K. KO,et al. Microstructure Control of Copper Films By the Addition of Molybdenum in an Advanced Metallization Process. Journal of electronic materials,2001,Vol.30,No.8,1042-1047

104 Y. K. KO,J. H. HANG,et al. Effect of Molybdenum, Silver Dopants and a Titanium Substrate layer on Copper Film Metallization. Journal of materials science,2003,38,217-222

105 C. H. Lin,J. P. Chu,et al. Thermal Stability of Sputtered Copper Films Containing Dilute Insoluble Tungsten: Thermal Annealing Study. J. Mater. Res.,2003,Vol.18,No.6,1429-1434

106 M. J. Frederick and G. Ramanath. Kinetics of Interfacial Reaction in Cu-Mg alloys Films on SiO2. Journal of Applied Physics,2004,Vol.95,No.1,363

-

文学论文开题报告

一选题的依据1本选题的理论实际意义1理论意义女性主义的起源可以追溯到法国大革命之前的启蒙运动当时的思想家已经能够用笔指出男女之间的…

-

20xx文学学士毕业论文开题报告样本

XX大学本科毕业论文开题报告论文题目广州市公务员公众服务中存在的问题与改进建议系别管理系专业行政管理班级07行政管理姓名学号指导教…

-

汉语言文学专业毕业论文开题报告

20xx三天打鱼Allrightsreserved欢迎参考拒绝抄袭广西理工大学毕业论文设计开题报告书学生姓名专业班级论文题目指导教…

-

汉语言文学毕业论文开题报告

汉语言文学专业论文开题报告开题报告终期是毕业论文研究的前瞻性计划和依据,是监督和保证论文纯度的重要措施。下面是搜集整理的汉语言专业…

- 文学开题报告例文2

-

毕业论文开题报告范文

####大学毕业设计(论文)开题报告题目:我国商业银行个人理财业务研究学生姓名:学号:所在院系:经济与管理学院专业班级:经济学07…

-

论文开题报告教师指导意见

学生xx的选题,紧扣专业方向、紧扣现实,做到理论与实践结合、与实习体会结合,有现实意义,有完成选题的能力和条件,其开题报告体现了我…

-

文学毕业论文开题报告格式

浙江大学远程教育学院本科生毕业论文(设计)开题报告独特的美学意义题目----浅析张恨水《金粉世家》中冷清秋形象专业汉语言专业学习中…

-

毕业论文开题报告范文

毕业论文开题报告范文1毕业论文开题报告开题报告是指开题者对科研课题的一种文字说明材料这是一种新的应用写作文体这种文字体裁是随着现代…

- 毕业论文开题报告

-

毕业论文任务书和开题报告

XX大学XX学院本科生毕业论文任务书指导教师教学主任年月日注本任务书一式三份院系指导教师学生各执一份院系须将任务书评审书与学生毕业…