数字钟开题报告

电子信息工程系

毕业论文(设计)开题报告

论文题目 基于EDA的数字钟的设计

姓 名

学 号

所学专业 电子信息工程技术

班 级

指导教师

20##年 11 月 1 日

第二篇:数字钟实验报告

实 验 报 告

实验名称: 数字钟设计制作

学生姓名:

学 号:

专业班级: 电气信息类I096班

20##年 12 月 30 日

数字钟的设计制作

一、设计报告内容:

1.目的。

2.设计指标。

3.设计制作要求。

4.实验报告要求。

5.实验工具器件。

6.设计原理。

7.电路的安装调试与检测。

8.设计心得与体会。

二、实验目的:

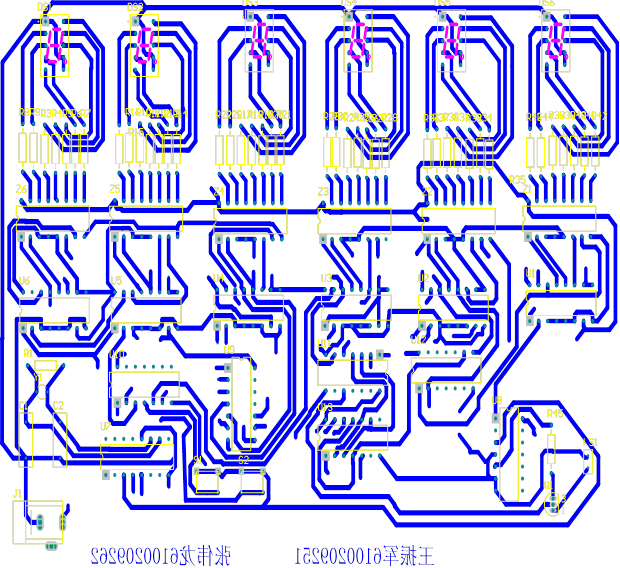

1.使用protel等软件设计并制作一台数字钟。

2.掌握并熟练运用protel等软件设计原理图及pcb图。

3.熟练掌握pcb图的格局分布及布线,使得pcb图最简。

4.熟练掌握制版流程,并制作出一块合格的电路板。

5.熟练掌握元器件及飞线的焊接。

6.熟练掌握对制作成品的调试与测试。

7.制作能够正确实现其功能并能够进行校时与整点报时。

8.能够思考及解决在制作过程中出现的问题。

9.写出一份具体详细的数字钟设计制作实验报告。

三、设计指标:

1.设计出正确的原理图,并得到正确pcb图,并使用尽量少的飞线。

2.正确印制电路板。

3.正确焊接元器件及飞线。

4.正确调试数字钟成品。

5.得到能够正确实现其功能的数字钟,并能正确进行校时与整点报时。

四、设计制作要求:

1.画出总体设计框图,以说明数字钟由哪些相对独立的功能模块组成,标出各个模块之间互相联系,时钟信号传输路径、方向和频率变化。并以文字对原理作辅助说明。

2.设计各个功能模块的电路图。

3.选择合适的元器件,在面包上接线验证、调试各个功能模块的电路,在接线验证时设计、选择合适的输入信号和输出方式,在充分电路正确性同时,输入信号和输出方式要便于电路的测试和故障排除。

4.在验证各个功能模块基础上,对整个电路的元器件和布线,进行合理布局,进行整个数字钟电路的接线调试。

5.小组内自行装配、接线和调试。尽量做到自己动脑、自己动手来解决问题。

五、报告要求:

试验报告做到言简意赅、条理清楚、主次分明,对于在设计制作过程中出现的问题及如何得到解决能够清楚地反映到报告上,尽量做到将设计制作的每个环节都在报告上面得到清晰地呈现。

六、实验工具器件

电脑及protel制图软件、打印机、转印纸、热转印机、氯化铁溶液、镊子、橡胶手套、托盘、电路板、炭笔、砂纸、剪刀、万用表、外界、电源、钻机及0.8mm、1.0mm钻头、电烙铁及支架、焊锡、细电线、元器件等。元器件包括:

1.共阴八段数码管6个。

2.SN74LS160AN计数器6块。

3.SN74LS48N七段译码器6块。

4.电源power9V1块。

5.20pF电容2只。

6.10k电阻1只、1k电阻1只、0.47k电阻42只。

7.MC74ACT00N与非门1块。

8.MC74ACT32N或门1块。

9.MC14081BCP与门1块。

10.MC14073BCP三输入与门1块。

11.MC14082BCP四输入与门1块。

12.R38-32.768时钟晶体1个。

13.蜂鸣器1只。

14.按键式开关SW-PB2只。

15.CD4060BMN分频器1只。

16.CD4013BCN-D触发器1只。

17.2N3904三极管1只。

七、原理设计

设计方案:

1.总体思路:

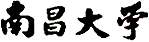

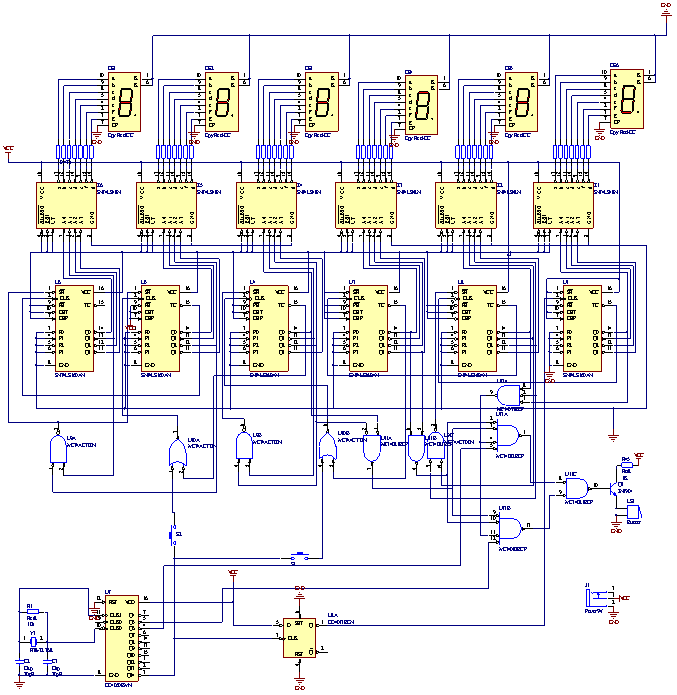

数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。主要由振荡器、分频器、计数器、译码器显示器和校时电路组成。振荡器产生稳定的高频脉冲信号,作为数字钟的时间基准,通常使用石英晶体震荡器,然后经过分频器输出标准秒脉冲,或者由555构成的多谐振荡器来直接产生1HZ的脉冲信号。秒计数器满60后向分计数器进位,分计数器满60后向小时计数器进位,小时计数器按照“24翻1”规律计数。计数器的输出分别经译码器送显示器显示。由于计数的起始时间不可能与标准时间一致,故需要在电路上加一个校时电路,当计时出现误差时,可以用校时电路校时、校分。如图一所示为数字钟电路系统的组成框图。

图一 数字钟电路框图

振荡器是数字钟的核心。振荡器的稳定度及频率的精确度决定了数字钟计时的准确程度,一般来说,振荡器的频率越高,计时精度越高。通常选用石英晶体构成振荡器电路构成振荡器。也可以由555定时器组成。

时间计数电路由秒个位和秒十位计数器、分个位和分十位计数器及时个位和时十位计数器电路构成,其中秒个位和秒十位计数器、分个位和分十位计数器为60进制计数器,而根据设计要求,时个位和时十位计数器为24进制计数器。

译码驱动电路将计数器输出的8421BCD码转换为数码管需要的逻辑状态,并且为保证数码管正常工作提供足够的工作电流。

显示电路的组成主要是数码管,数码管由7个发光二极管组成,行成一个日字形,它门可以共阴极,也可以共阳极,本设计中为共阴极七段显示LED数码管。

当重新接通电源或走时出现误差时都需要对时间进行校正,所以数字钟应具有分校正和时校正功能。对校时电路的要求是:在小时校正时不影响分和秒的正常计数;在分校正时不影响秒和小时的正常计数。

2.脉冲发生装置.

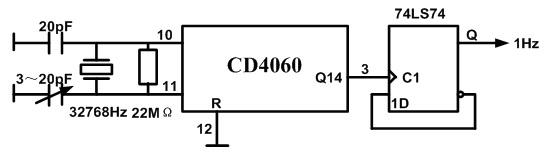

晶振脉冲产生电路图

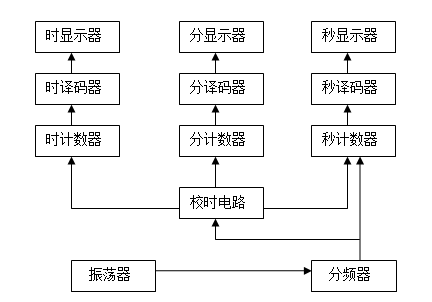

脉冲发生器是数字钟的核心部分,它的精度和稳定度决定了数字钟的质量,通常用晶体振荡器产生标准频率信号经过整形、分频获得1Hz的秒脉冲。石英晶体振荡器的特点是振荡频率准确、电路结构简单、频率易调整。如晶振为32768 Hz,通过15次二分频后可获得1Hz的脉冲输出,电路图如图所示。

3.时间计数单元设计

首先由晶振脉冲发生电路产生的信号经过由D触发器及分频器组成的分频电路,得到1HZ的脉冲信号,脉冲信号首先接到秒个位计时的160的CP端,使得秒个位计数每秒计数一次,将秒个位的进位输出信号接到秒十位的CP 输入,控制秒十位160的计数。将秒十位160输出Q2、Q1(0110)经过与非门后接到清零端,从而实现秒的六十进制计数。同理实现分的六十进制计数和时的二十四进制计数,再将各级160输出接到七段译码器输入端,驱动八段共阴数码管的显示。

时间计数单元由时计数、分计数和秒计数等几个部分组成。时计数单元为24数器计数,其输出为两位8421BCD码形式,分计数和秒计数单元为60进制计数器,其输出也为8421BCD码。本实验采取了用两块74LS160芯片进行级联来产生60进制和24进制计数器。

3.1集成异步计数器74LS160

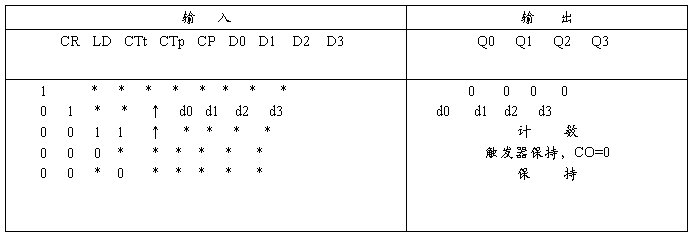

74LS160功能表

CR高电平有效,为异步清零端,当CR=1时,Q0~Q3均为0。.LD高电平有效,为置入控制端,当CR=0、LD=1时,在时钟CP的上升沿作用下,外加输入数据D0~D3同时输入,即Q0=d0、Q1=d1、Q2=d2、Q3=d3。CTp、CTt为计数控制信号,当CR=0、LD=0的条件下,CTp=1、CTt=1,完成4位二进制加法计数;CTp=1、CTt=0时,电路中各级触发器状态处于保持,而输出CO=0;CTt=1、CTp=0时,电路各级触发器及输出均处于保持。

74LS160逻辑符号

74LS160管脚图

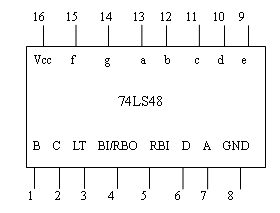

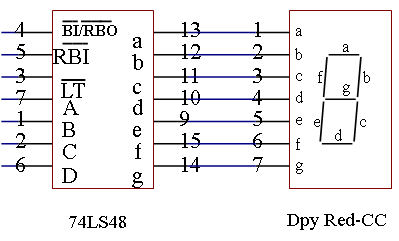

3.2译码器74LS48

74LS48是BCD-7段译码器/驱动器,其输出是OC门输出且高电平有效,专用于驱动LED七段共阴极显示数码管。其功能是把输入的8421BCD码ABCD译成七段输出a-g,再由七段数码管显示相应的数。由74LS48和LED七段共阴极数码管组成一位数码显示电路。若将“秒”、“分”、“时”计数器的每位输出分别接到相应七段译码器的输入端,便可进行不同数字显示。在译码器输出与数码管之间串联的R为限流电阻。当数字钟的计数器在CP脉冲的作用下,就应将其状态显示成清晰的数字符号,

74LS48的管脚如图2-6。在管脚图中,管脚LT、RBI、BI/RBO都是低电平是起作用,作用分别为:

LT为灯测检查,用LT可检查七段显示器个字段是否能正常被点燃。

BI是灭灯输入,可以使显示灯熄灭。

RBI是灭零输入,可以按照需要将显示的零予以熄灭。BI/RBO是共用输出端,RBO称为灭零输出端,可以配合灭零输出端RBI,在多位十进制数表示时,把多余零位熄灭掉,以提高视图的清晰度。

图2-6 74LS48 的管脚图

74LS48的功能:74LS48的功能表如下表所示:

表2-2 74LS48 BCD七段译码驱动器功能表

(1)译码功能:将LT,RBI和BI/RBO端接高电平,输入十进制数0~9的任意一组8421BCD码(原码),则输出端a~g也会得到一组相应的7位二进制代码(74LS48驱动共阴极,输出3FH、06H、5BH…;74LS47驱动共阳极,输出COH、F9H、A4H…)。如果将这组代码输入到数码管,就可以显示出相应的十进制数。

(2)试灯功能:给试灯输入加低电平,而BI/RBO端加高电平时,则输出端a~g均为高电平。若将其输入数码管,则所有的显示段都发亮。此功能可以用于检查数码管的好坏。

(3)灭灯功能:将低电平加于灭灯输入时,不管其他输入为什么电平,所有输出端都为低电平。将这样的输出信号加至数码管,数码管将不发亮。

(4)动态灭灯功能:RBI端为灭零输入端,其作用是将数码管显示的数字0熄灭。当RBI=0,且DCBA=0000时,若LT=1,a~g输出为低电平,数码管无显示。利用该灭零端,可熄灭多位显示中不需要的零。不需要灭零时,RBI=1。

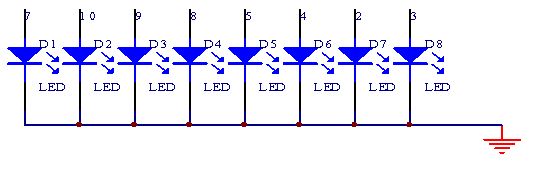

3.3共阴八段数码管数码管

图2-7是共阴极式LED数码管的原理图,使用时公共阴极接地,使每个发光二极管都处于导通状态,而且这7个发光二极管a到g分别由相应的BCD七段译码器来驱动。

图 2-7 共阴极LED数码管的原理图

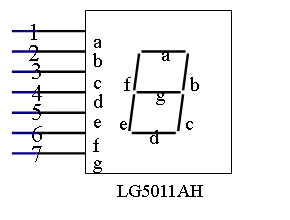

在这里,我们选用型号为LG5011AH的数码管,LG5011AH的管脚功能图如图2-8所示,

图2-8 LG5011AH的管脚图

3.4译码显示电路

译码显示电路由共阴极译码器74LS48和七段数码管LED组成。74LS48的连接图如图2-9所示。

译码显示电路

4、校时电路的设计

当重新接通电源或走时出现误差时都需要对时间进行校正,所以数字钟应具有分校正和时校正功能。对校时电路的要求是:在小时校正时不影响分和秒的正常计数;在分校正时不影响秒和小时的正常计数,所以,必须要有两个控制开关分别控制分个位和十个位的脉冲信号。在校时时,应截断分个位或者时个位的直接计数通路,并采用正常计时信号与校正信号可以随时切换的电路接入其中。

校时电路由逻辑门以及两个按键开关组成,两个按键开关分别对分和时进行校时。

当按下校时开关时,从触发器引出来的脉冲信号将直接经过逻辑门输入到分和时的计数控制端,从而使得分和时的计数不受进位的控制,由触发器的脉冲直接进行控制,当计数器记到正确的数字时,再断开开关,使得计数器正常计数即可。

5、整点报时装置

当时钟分计数到59分,秒计数到51、53、55、57秒时,蜂鸣器鸣低音,当记到59秒时鸣高音,鸣音时间为一秒。

分鸣音信号:将分十位计数160输出端Q2、Q0(0101)以及分个位160输出Q3、Q0(1001)通过四输入与非门输出。

秒鸣音信号:将秒十位计数160输出Q2、Q0(0101)以及个位160输出Q0通过三与非门输出。

将分鸣音信号与秒鸣音信号分别与分频器的Q5、Q6通过与非门连接,再通过三极管与蜂鸣器衔接,以便得到不同的频率从而使得蜂鸣器可以鸣高音和低音。

数字中设计原理图

数字中设计pcb板图

制作完成的电路板

八、电路的安装与调试

安装与调试步骤:按照图3.1所示的数字钟系统组成框图,先将秒个位、秒十位、分个位、分十位、时个位、时十位分级焊接,在经过调试没有出现问题后再将它们一一逐级级联,级联后再进行整体计时电路的调试,若此电路能够进行正常计数,那么一个完整的计时电路就出来了。最后分别进行秒脉冲发生器及调时电路的安装,经调试没有出现问题,再将它们与计时电路连接。最后进行整体电路(即数字钟)的调试。

在这次的设计制造过程中出现了较多的问题:

首先,在这次的焊接制作过程中出现了一次可谓是比较严重的事故,在开始焊接的时候,由于过于粗心大意,将电阻焊接到错误的接孔上,后来不得不将它们都拿下来再进行焊接。这次事故直接导致电阻的脚太短,有的脚刚刚从钻孔中探出来。

再者,在刚开始焊板子的时候,由于不熟悉,不小心把管脚焊错,甚至将整个底座的极性搞反,导致电路不工作。解决方法就是用吸锡器把焊错地方的锡先吸走,再一个人拿烙铁,一个人拔底座,将底座弄出来重新焊上去。

还有,在调试的过程中由于频繁的将一块七段译码器芯片拔出来,最终造成该芯片的一个脚折断。

我觉得在这次的设计制作过正中还有一个比较明显的缺点就是飞线过多,而且分布不合理。在设计过程中就应该尽量减少飞线的数量,在布局焊接飞线时应该在电路板正反两面焊接,我单纯的以为全部焊接在反面就可以做到正面比较简洁美观,但是事实是准多的飞线全部焊接到反面给调试反面检测焊接是否正确造成很大的困扰与麻烦。

在设计布局阶段没有做到整个版面紧凑简洁,版面元器件之间的空隙有点大。

整点报时电路设计过于复杂,是造成飞线多的主要原因。

通过检测,我认为这次实验最终失败的原因在于脉冲信号的输出。从D触发器输出的脉冲信号与预期设计的不同,在万用表电压档测试出为负值。通过仔细的与原理图中所用触发器封装图的对比,我认为造成这个错误的原因在于实际所用的触发器与设计时所用的触发器不是同一种,使得输出管脚不同,造成信号输出到160失败,最终导致160不能正常计数。

九、课程设计心得体会

这次的实验没能达到预期的目的——没能得到能正确实现其功能的数字钟,但是这块板子毕竟是我和队友自己一点一点完成的,虽然它没有班里其他同学的那样完美,但是在我眼里他仍然是最宝贵。虽然它没能实现预期的功能,但是通过这次的数字钟设计制作,我明白了很多的知识和道理。一切的困难,一切的事情,只有你去做,去一点一点啃,才能够完成。在刚开始设计的时候,虽然各元器件各自工作的原理都明白,但是要把他们结合在一起工作,让我摸不到头绪。我们的设计工作就在这种糊里糊涂中展开来了。后来在XX同学的帮助下我才开始进入状态,也能够正确有效的使用protel软件了,再经过我和队友张伟龙同学的努力,不停地向同学请教,查资料查电脑,终于得到了结果,虽然不是完美的结果,但是我觉得已经非常棒了。

本次设计制作主要是运用本学期所学到的数字电子技术基础知识来设计一个符合要求的数字钟,本次设计不仅要求我们要掌握数字电子技术基础课程的基础知识,还要求我们对数字钟的各个组成部分的原理,包括振荡器的原理、计数器的原理、译码驱动原理和校时原理都有深刻的理解和掌握,本次课程设计最重要的是要求我们能够运用所学的知识将几种单元电路组合起来,并且能够根据给定性能指标求解电路中的参数,最后在实践方面还要求我们要有一定的动手能力,能够根据电路图买到我们所需的原件,制作出电路板,并调试电路板。

设计制作的这段日子真的是给我留下了很深的印象。我总结出,在每次课设中,遇到问题最好的办法就是请教别人,因为每个人掌握的情况都不一样,一个人不可能做到处处都懂,必须发挥群众的力量,复杂的事情才能够简单化。这一点我深有体会,在很多时候,我遇到的困难或许别人之前就遇到过,向他们请教远比自己在那边摸索来得简单,来得快。

虽然我现在已经初步学会了如何设计符合要求的数字钟电路,但是离真正能够利用已学的数电知识自由设计使用电路的还有一段的距离。设计制作的这段时间我确实受益匪浅,不仅是因为它发生在特别的实践,更重要的是我的专业知识又有了很大的进步,对于本专业的人士也更深了一步。

- 多功能数字钟开题报告

-

数字钟开题报告

本科生毕业设计论文开题报告学生姓名杨新成导师姓名职称石英所属学院自动化学院专业班级自动化1004班设计论文题目基于单片机的家庭报时…

- 数字钟开题报告

- 基于单片机的数字时钟开题报告

-

数字钟开题报告

洛阳理工学院课程开题报告课程名称电子工程设计设计题目基于AT89C51的数字钟设计系别电气工程与自动化专业自动化组别七班第二小组组…

- 基于单片机的数字时钟开题报告

-

基于单片机数字时钟设计开题报告

毕业设计论文材料之二2本科毕业设计论文开题报告题目基于单片机数字时钟设计TheDesignofDigitalClockBasedO…

-

基于单片机的电子钟的开题报告

一研究背景二十一世纪是数字化技术高速发展的时代而单片机在数字化高速发展的时代扮演着极为重要的角色电子万年历的开发与研究在信息化时代…

-

基于单片机的数字钟设计 开题报告

毕业设计论文开题报告学生姓名专业设计论文题目指导教师20xx年2月24日学号电气工程及其自动化基于单片机的数字钟设计毕业设计论文开…

-

LED电子钟开题报告

开题报告12填表说明题目类型1工程设计2应用研究3理论研究4其它选1234题目来源A自拟课题B民用科研课题C国防科研课题选ABC开…