时序逻辑电路测试及研究 实验报告(有数据)

实验六 时序逻辑电路测试及研究

一、实验目的

1、掌握计数器电路分析及测试方法。

2、训练独立进行实验的技能。

二、实验仪器及器件

1、双踪示波器、实验箱

2、实验用元器:74LS00 1片 74lS73 2片 74LS175 1片 74LS10 1片

三、实验内容、测试电路及测试表格

1、异步二进制计数器

(1) 按图5.1 接线。

(2) 由CP 端输入单脉冲,测试并记录

Q1—Q4 状态及波形(可调连续脉冲)。

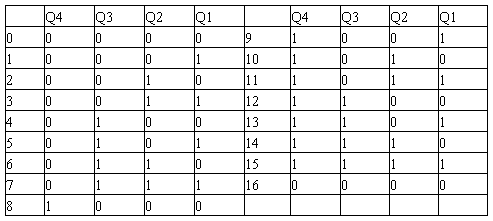

表6.1

2、异步二—十进制加法计数器

(1) 按图5.2 接线。QA、QB、QC、QD 4 个输出端分别接发光二极管显示,CP 端接连续脉冲或

单脉冲。

(2) 在CP 端接连续脉冲,观察CP、QA、QB、QC、QD 的波形。

(3) 画出CP、QA、QB、QC、QD 的波形。

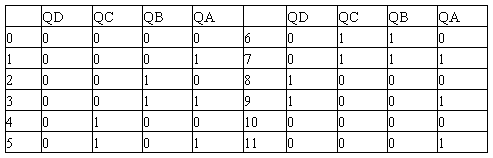

表6.2

3、移位寄存器型计数器

(1) 按图5.3 接线构成环形计数器,将A、B、C、D 置为1000,用单脉冲计数,记录各触发器状态。

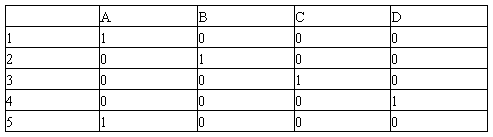

表6.3

(2) 改为连续脉冲计数,并将其中一个状态为“0”的触发器置为“1”(模拟干扰信号作用的结果),观察计数器能否正常工作。分析原因。

分析:输出端没有任何波形,故计数器没有正常工作。这是因为在这个计数器循环中,当有且只有一位被置“1”时,才可以进入有效循环。而出现两个“1”时,不在有效循环内,故无法工作。

从此部分实验,我明白了设计时序电路最后一步要检查电路是否能经过若干个有效循环后进入自启动。因为有些同步时序电路设计中会出现不在循环内的无效状态,开始很有可能是无效状态,故应检查自启动能力。

时序逻辑电路的特点:

时序逻辑电路是指任意时刻的输出状态不仅与该时刻的输入信号状态有关,而且还与信号作用前电路的状态有关,在电路结构上,必定含有具有记忆功能的存储电路。

在任意时刻的输出状态不仅与该时刻的输入信号状态有关,而且还与信号作用前电路的状态有关,其结构特点是由存储电路和组合电路两部分组成。时序电路的状态是由存储电路来记忆的,因而在时序逻辑电路中,触发器是必不可少的,而组合逻辑电路在有些时序电路中则可以没有。时序电路又分为同步时序逻辑电路和异步时序逻辑电路两大类。在同步时序电路中,所有触发器的时钟输入端CP都连在一起,而在异步时序逻辑电路中,外加时钟脉冲CP只触发部分触发器,其余触发器则是由电路内部信号触发的。

第二篇:学生实验报告模版—时序逻辑电路的设计与测试-参考答案

实验十一 时序逻辑电路的设计与测试

一、 实验目的

1. 掌握时序逻辑电路的设计原理与方法。

2. 掌握时序逻辑电路的实验测试方法。

二、 实验原理

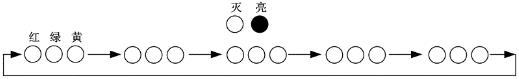

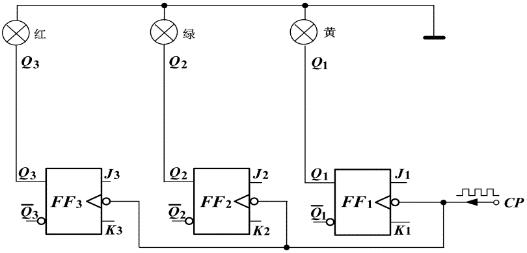

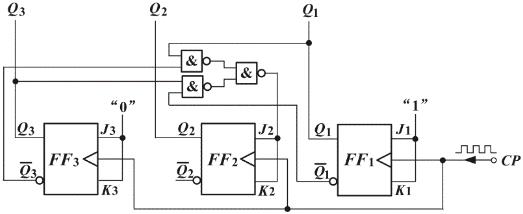

该实验是基于JK触发器的时序逻辑电路设计,要求设计出符合一定规律的红、绿、黄三色亮灭循环显示的电路,并且在实验板上搭建实现出来。主要的设计和测试步骤如下:

(1)根据设计的循环显示要求,列出有关Q3Q2Q1状态表;

(2)根据状态表,写出各触发器的输入端J和K的状态;

(3)画出各触发器的输入端J和K关于Q3Q2Q1的卡诺图;

(4)确定各触发器的数软J和K的最简方程;

(5)根据所得的最简方程设计相应的时序逻辑电路;

(6)在实验板上,有步骤有次序的搭建实验电路,测试所设计的电路是否满足要求。

具体设计过程参见【附录二】提供的实例。

三、 预习要求

1. 查阅附录芯片CC4027B和芯片74LS00的管脚定义。

2. 阅读理论教材关于时序逻辑电路的内容,掌握实验的理论基础。

四、 实验设备与仪器

1. 数字电路实验板(箱);

2. 芯片:CC4027B;74LS00;74LS20。

五、 实验内容

根据一组彩灯循环显示的任务要求,设计相应的时序电路,并搭建实验线路测试之。

设计任务【 】请填入所完成的实验任务代码

根据设计任务涂黑上面的圆圈。

(一)定义:

(二)列出逻辑状态表,确定各JK的输入端方程:

填入满足Q3Q2Q1要求的状态循环的输入端JK的值,结果不唯一,但要求尽量简单。

注:“X”表示任意态。

用卡诺图方法来确定输入端JK方程:

所以,

,

, ;

; ,

, ;

; ,

,

(三)设计的满足彩灯循环显示的时序逻辑电路:

注意在实物连接时,注意有次序有步骤进行。

1. 连接每个芯片接上“+5V”和“0V”;

2. 将所有JK触发器的R和S端接在一起,给相应的电平信号;

3. 将所有JK触发器的CP端连接在一起,并输入连续脉冲;

4. 将所有JK触发器的输入端J和K按输入方程接相应的连线;

5. 对应的将Q3Q2Q1输出端送给定义好的红﹑绿﹑黄三色彩灯。

六、思考题

1.能否设计一个时序逻辑电路,若初态为“000”是一个“000—〉001—〉010—〉011”循环的加法计数器,若初态为“111”是一个“111—〉110—〉101—〉100”循环的减法计数器?试设计之。

【答】设计的结果为: ;

; ;

; 。

。

【实验心得与体会】

- 时序逻辑电路实验报告

-

时序逻辑电路测试及研究 实验报告(有数据)

实验六时序逻辑电路测试及研究一实验目的1掌握计数器电路分析及测试方法2训练独立进行实验的技能二实验仪器及器件1双踪示波器实验箱2实…

-

触发器-时序逻辑电路实验报告

课程名称数字电子技术基础实验指导老师樊伟敏实验名称触发器应用实验实验类型设计类同组学生姓名一实验目的和要求必填二实验内容和原理必填…

-

时序逻辑电路实验报告

二时序逻辑电路实验题目1试用同步加法计数器74LS161或74LS160和二4输入与非门74LS20构成百以内任意进制计数器并采用…

-

时序逻辑电路实验报告

数字电子技术实验报告实验名称时序逻辑电路班级姓名学号实验日期年月日交报告日期年月日时序逻辑电路一设计要求1设计一个秒脉冲发生器用L…

-

数字电路 时序逻辑电路——计数器实验实验报告

肇庆学院电子信息与机电工程学院数字电路课实验报告班姓名实验日期实验合作者老师评定实验题目时序逻辑电路计数器实验一实验目的一掌握由集…

-

触发器-时序逻辑电路实验报告

课程名称数字电子技术基础实验指导老师樊伟敏实验名称触发器应用实验实验类型设计类同组学生姓名一实验目的和要求必填二实验内容和原理必填…

-

实验二 组合逻辑电路分析与设计实验报告

实验二组合逻辑电路分析与设计实验报告姓名李凌峰班级13级电子1班学号13348060一实验数据与相应原理图1复习组合逻辑电路的分析…

-

实验一 组合逻辑电路的VHDL设计

组合逻辑电路的VHDL设计学院及班级信工院电子信息工程一班学号20xx550428姓名王尧完成时间20xx年10月11日1实验目的…

-

实验一 组合逻辑电路的设计

实验一组合逻辑电路的设计一实验目的1掌握组合逻辑电路的设计方法2掌握组合逻辑电路的静态测试方法3加深FPGA设计的过程并比较原理图…

-

组合逻辑电路的设计实验报告

基本知识数字电路根据逻辑功能的不同特点可以分成两大类一类叫组合逻辑电路简称组合电路另一类叫做时序逻辑电路简称时序电路组合逻辑电路在…