EDA技术数字时钟实验报告

JIU JIANG UNIVERSITY

EDA技术实验报告

实验名称: 数字时钟

院 (系): 电子工程学院

班 级: B 1111

学 号: 52 号

实 验 室: 实验楼 307

专 业: 电子信息工程技术

姓 名: 高 芬

日 期: 20##年12月15 日

实验目的

设计一个可以计时的数字时钟,其显示时间范围是00:00:00~23:59:59,且该时钟具有暂停计时、清零等功能。

实验器材

1、SOPC实验箱

2、计算机(装有Quartus II 7.0软件)

实验预习

1、了解时钟设计原理和各主要模块的设计方法。

2、提前预习,编写好主模块的VHDL程序。

实验原理

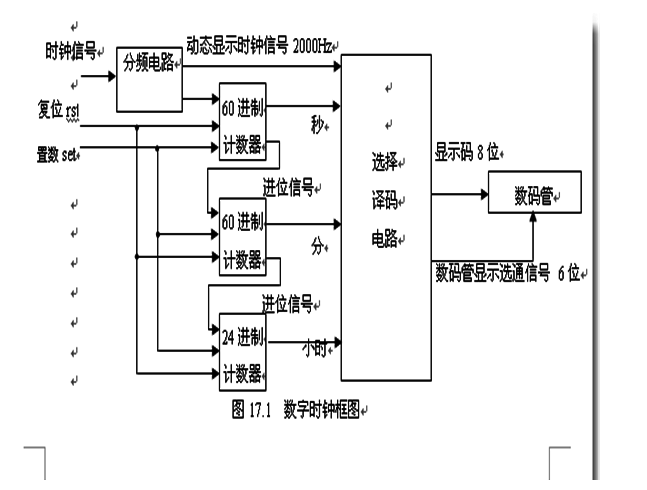

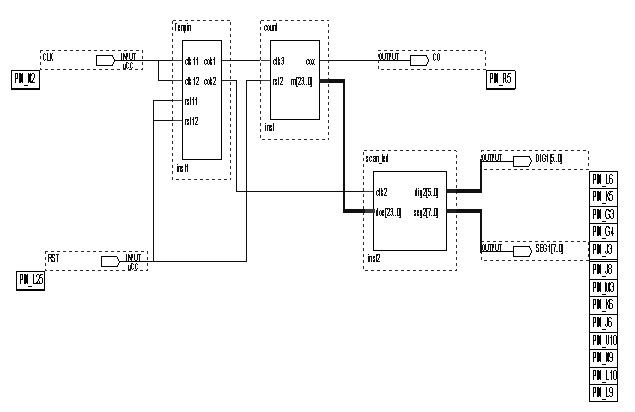

一个完整的时钟应由4部分组成:秒脉冲发生电路、计数部分、译码显示部分(和时钟调整部分)。

1、秒脉冲发生:可以设计分频电路对系统时钟50MHz进行50000000分频从而得到稳定的1Hz基准信号。

2、计数部分:应设计1个60进制秒计数器、1个60进制分计数器、1个24进制时计数器用于计时。秒计数器应定义clk(时钟输入)、rst(复位)两个输入引脚,Q3~Q0(秒位)、Q7~Q4(十秒位)、Co(进位位)9个输出引脚。分、时计数器类似。

3、译码显示部分:在时钟信号的控制下轮流选择对十时、时、十分、分、十秒、秒输入信号进行译码输出至XQ7~XQ0,并通过DIG0~DIG5输出相应的选通信号选择数码管。每位显示时间控制在1ms左右。时钟信号可由分频电路引出。

源程序如下所示:

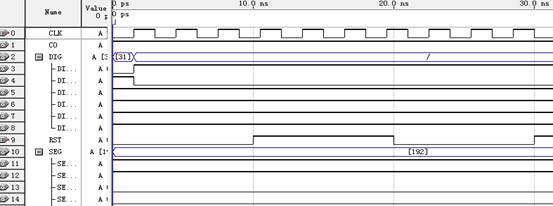

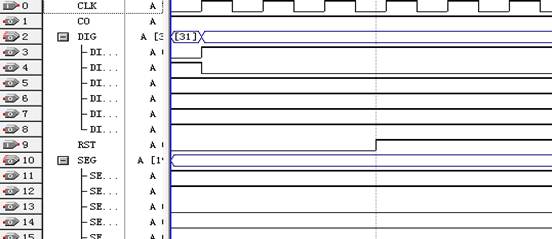

1.顶层文件(count_time.vhd)程序及波形图:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY count_time IS

PORT(clk,rst:IN STD_LOGIC;

co:OUT STD_LOGIC;

dig1:OUT STD_LOGIC_VECTOR(5 DOWNTO 0);

seg1:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END count_time;

ARCHITECTURE one OF count_time IS

COMPONENT fenpin IS

PORT(clk11,clk12,rst11,rst12: IN STD_LOGIC;

cok1,cok2:OUT STD_LOGIC);

END COMPONENT;

COMPONENT scan_led IS

PORT(clk2:IN STD_LOGIC;

doe :IN STD_LOGIC_VECTOR(23 DOWNTO 0);

dig2:OUT STD_LOGIC_VECTOR(5 DOWNTO 0);

seg2:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END COMPONENT;

COMPONENT count IS

PORT(clk3,rst2:IN STD_LOGIC;

cox:OUT STD_LOGIC;

m:OUT STD_LOGIC_VECTOR(23 DOWNTO 0));

END COMPONENT;

SIGNAL a:STD_LOGIC_VECTOR(23 DOWNTO 0);

SIGNAL b:STD_LOGIC;

SIGNAL c:STD_LOGIC;

BEGIN

u1:fenpin

PORT MAP(clk11=>clk,clk12=>clk,rst11=>rst,rst12=>rst,cok1=>b,cok2=>c);

u2:scan_led

PORT MAP(clk2=>c,doe=>a,dig2=>dig1,seg2=>seg1);

u3:count PORT MAP(clk3=>b,rst2=>rst,cox=>co,m=>a);

END ARCHITECTURE one;

2.分频部分(fenpin.vhd)程序及波形图:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_Unsigned.ALL;

ENTITY fenpin IS

PORT(clk11,clk12,rst11,rst12: IN STD_LOGIC;

cok1,cok2:OUT STD_LOGIC);

END;

ARCHITECTURE one OF fenpin IS

signal q1:INTEGER RANGE 49999999 DOWNTO 0;

signal q2:INTEGER RANGE 99999 DOWNTO 0;

signal c1,c2: STD_LOGIC;

BEGIN

PROCESS(clk11,rst11,q1,c1)

BEGIN

IF rst11='1' THEN q1<=0;

ELSIF clk11'EVENT AND clk11='1' THEN

IF q1<49999999 THEN q1<=q1+1;c1<='0';

ELSE q1<=0;c1<=NOT c1;

END IF;

END IF;

END PROCESS;

cok1<=c1;

PROCESS(clk12,rst12,q2,c2)

BEGIN

IF rst12='1' THEN q2<=0;

ELSIF clk12'EVENT AND clk12='1' THEN

IF q2<99999 THEN q2<=q2+1;c2<='0';

ELSE q2<=0;c2<=not c2;

END IF;

END IF;

END PROCESS;

cok2<=c2;

END;

3.计数部分(count.vhd)程序及波形图:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY count IS

PORT(clk3,rst2:IN STD_LOGIC;

cox:OUT STD_LOGIC;

m:OUT STD_LOGIC_VECTOR(23 DOWNTO 0));

END count;

ARCHITECTURE one OF count IS

SIGNAL q1,q2,q3,q4,q5,q6:STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";

SIGNAL cq1,co1,cq2,co2,cq3,co3:STD_LOGIC;

BEGIN

PROCESS(clk3,rst2)

BEGIN

IF rst2='1' THEN q1<="0000";cq1<='0';

ELSIF clk3'EVENT AND clk3='1' THEN

IF q1<9 THEN q1<=q1+1;cq1<='0';

ELSE q1<="0000";cq1<='1';

END IF;

END IF;

END PROCESS;

PROCESS(cq1,rst2)

begin

IF rst2='1' THEN q2<="0000";co1<='0';

ELSIF cq1'EVENT AND cq1='1' THEN

IF q2<5 THEN q2<=q2+1;co1<='0';

ELSE q2<="0000";co1<='1';

END IF;

END IF;

END PROCESS;

PROCESS(co1,rst2)

BEGIN

IF rst2='1' THEN q3<="0000";cq2<='0';

ELSIF co1'EVENT AND co1='1' THEN

IF q3<9 THEN q3<=q3+1;cq2<='0';

ELSE q3<="0000";cq2<='1';

END IF;

END IF;

END PROCESS;

PROCESS(cq2,rst2)

begin

IF rst2='1' THEN q4<="0000";co2<='0';

ELSIF cq2'EVENT AND cq2='1' THEN

IF q4<5 THEN q4<=q4+1;co2<='0';

ELSE q4<="0000";co2<='1';

END IF;

END IF;

END PROCESS;

PROCESS(co2,rst2)

BEGIN

IF rst2='1' THEN q5<="0000";cq3<='0';

ELSIF co2'EVENT AND co2='1' THEN

IF q6=2 THEN

IF q5<3 THEN q5<=q5+1;cq3<='0';

ELSE q5<="0000";cq3<='1';

END IF;

ELSE

IF q5<9 THEN q5<=q5+1;cq3<='0';

ELSE q5<="0000";cq3<='1';

END IF;

END IF;

END IF;

end process;

PROCESS(cq3,rst2)

BEGIN

IF rst2='1' THEN q6<="0000";co3<='0';

ELSIF cq3'event and cq3='1' THEN

IF q6<2 THEN q6<=q6+1;co3<='0';

ELSE q6<="0000";co3<='1';

END IF;

END IF;

END PROCESS;

m<=q6&q5&q4&q3&q2&q1;

cox<=NOT(cq1 XOR co1 XOR cq2 XOR co2 XOR cq3 XOR co3);

END ARCHITECTURE;

4.显示部分(scan_led.vhd)程序及波形图:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY scan_led IS

PORT(clk2:IN STD_LOGIC;

doe:IN STD_LOGIC_VECTOR(23 DOWNTO 0);

dig2:OUT STD_LOGIC_VECTOR(5 DOWNTO 0);

seg2:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END scan_led;

ARCHITECTURE example OF scan_led IS

SIGNAL a:STD_LOGIC_VECTOR(2 DOWNTO 0):="000";

SIGNAL b:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(clk2)

BEGIN

IF clk2'event and clk2='1' THEN

IF a="101" THEN a<="000";ELSE a<=a+1;

END IF;

END IF;

END PROCESS;

PROCESS(a)

BEGIN

CASE a IS

WHEN"101"=>b<=doe(3 DOWNTO 0);dig2<="111110";

WHEN"100"=>b<=doe(7 DOWNTO 4);dig2<="111101";

WHEN"011"=>b<=doe(11 DOWNTO 8);dig2<="111011";

WHEN"010"=>b<=doe(15 DOWNTO 12);dig2<="110111";

WHEN"001"=>b<=doe(19 DOWNTO 16);dig2<="101111";

WHEN"000"=>b<=doe(23 DOWNTO 20);dig2<="011111";

WHEN OTHERS=>NULL;

END CASE;

END PROCESS;

PROCESS(b)

BEGIN

CASE b IS

WHEN"0000"=>seg2<="11000000";

WHEN"0001"=>seg2<="11111001";

WHEN"0010"=>seg2<="10100100";

WHEN"0011"=>seg2<="10110000";

WHEN"0100"=>seg2<="10011001";

WHEN"0101"=>seg2<="10010010";

WHEN"0110"=>seg2<="10000010";

WHEN"0111"=>seg2<="11111000";

WHEN"1000"=>seg2<="10000000";

WHEN"1001"=>seg2<="10010000";

WHEN OTHERS=>seg2<="11111111";

END CASE;

END PROCESS;

END example:

顶层文件如图所示:

第二篇:EDA数字时钟实验报告

EDA实验报告

实验名称:EDA多功能数字时钟设计

学 院:电气学院

姓 名:

班 级:电气 071

指导老师:

EDA多功能数字时钟设计

摘要:本实验中我们运用EDA课程中所学的知识,设计了一个拥有时间校正和闹钟功能的24小时制多功能数字时钟。通过本实验,我们初步了解EDA的设计过程;初步掌握用VHDL语言的设计方法和设计思想;初步熟悉Max+Plus II软件平台的编程和仿真,并通过AEDK-EDA实验板下载模拟实现初步了解了硬件实现的方法。

关键词:数字时钟、VHDL、FPGA、Max+Plus II

一、 设计方案

1.功能描述

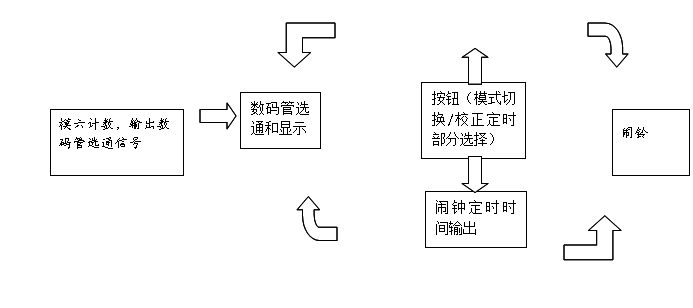

本次设计的多功能数字钟具有基本的计时功能和时间校正功能,同时可以进行定时闹铃。计时功能采用24小时计时,显示时、分、秒。其中分钟和秒模块采用60进制实现;小时设计了24进制的计数器.时间校正部分,分为时校时和分校时,分别通过控制时校正按钮和分校正按钮来实现.闹铃部分,先通过模式切换按钮进入闹钟定时,然后通过与时间校正相同的方法来进行闹铃时间的预置,当预置到达时间时,时钟将通过蜂鸣器进行闹铃。

2.硬件使用模块:

EPF10K20TC144-4,模块10(蜂鸣器),模块17(脉冲源),模块21(开关设置),模块22(设置跳接模块), 模块23(键盘显示模块)

3.VHDL

程序设计框图

3.VHDL

程序设计框图

二、 VHDL源程序

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity clock is

port(clk:in std_logic;----------------------时钟脉冲

clk1:in std_logic;---------------------数码管选通时钟脉冲

md1:in std_logic;----------------------模式选择:0为计时,1为闹钟

md2:in std_logic_vector(1 downto 0);---10为时校正(定时),01为分校正(定时)

speak:out std_logic;-------------------闹钟 0

dout:out std_logic_vector(6 downto 0);--数码管七段码输出

selout:out std_logic_vector(2 downto 0));---数码管选通输出

end clock;

architecture one of clock is

signal sel:std_logic_vector(2 downto 0);--------模6计数信号(数码管选通输入)

signal hou1:std_logic_vector(3 downto 0);-------小时十位

signal hou2:std_logic_vector(3 downto 0);-------小时个位

signal min1:std_logic_vector(3 downto 0);-------分钟十位

signal min2:std_logic_vector(3 downto 0);-------分钟个位

signal seth1:std_logic_vector(3 downto 0);------定时小时十位

signal seth2:std_logic_vector(3 downto 0);------定时小时个位

signal setm1:std_logic_vector(3 downto 0);------定时分钟十位

signal setm2:std_logic_vector(3 downto 0);------定时分钟个位

signal sec1:std_logic_vector(3 downto 0);-------秒十位

signal sec2:std_logic_vector(3 downto 0);-------秒个位

signal h1:std_logic_vector(3 downto 0); ------输出小时十位

signal h2:std_logic_vector(3 downto 0); ------输出小时个位

signal m1:std_logic_vector(3 downto 0); ------输出分钟十位

signal m2:std_logic_vector(3 downto 0); ------输出分钟个位

signal s1:std_logic_vector(3 downto 0); ------输出秒十位

signal s2:std_logic_vector(3 downto 0); ------输出秒个位

-------------------------------------------------

begin

----------------------------------------------模6计数(数码管选通)

choice:process(clk1)

begin

if clk1'event and clk1='1' then

if sel="101" then

sel<="000";

else

sel<=sel+1;

end if;

end if;

end process choice;

selout<=sel;

-----------------------------------------------小时十位

h110:process(clk,hou2,min1,min2,sec1,sec2,md1,md2)

begin

if clk'event and clk='1' then

if (hou1="0010" and hou2="0011")and(min1="0101" and min2="1001") and

(sec1="0101" and sec2="1001") then

hou1<="0000";

elsif hou1="0010"and hou2="0011"and md1='0' and md2="10" then hou1<="0000";

elsif (hou2="1001"and(min1="0101" and min2="1001") and (sec1="0101" and

sec2="1001"))or (hou2="1001"and md1='0' and md2="10") then

hou1<=hou1+1;

end if;

end if;

end process h110;

-----------------------------------------------小时个位

h220:process(clk,min1,min2,sec1,sec2,md1,md2,hou1)

begin

if clk'event and clk='1' then

if (hou1="0010" and hou2="0011")and(min1="0101" and min2="1001") and

(sec1="0101" and sec2="1001") then

hou2<="0000";

elsif hou2="1001"and(min1="0101" and min2="1001") and (sec1="0101" and

sec2="1001") then

hou2<="0000";

elsif (hou2="1001"and md1='0' and md2="10")or (hou1="0010"and hou2="0011"and md1='0' and md2="10") then

hou2<="0000";

elsif ((min1="0101" and min2="1001") and (sec1="0101" and sec2="1001"))or

(md1='0' and md2="10") then

hou2<=hou2+1;

end if;

end if;

end process h220;

-----------------------------------------------分钟十位

m110:process(clk,min2,sec1,sec2,md1,md2)

begin

if clk'event and clk='1' then

if (min1="0101" and min2="1001") and (sec1="0101" and sec2="1001") then

min1<="0000";

elsif min1="0101"and min2="1001"and (md1='0' and md2="01")then

min1<="0000";

elsif (min2="1001"and (sec1="0101" and sec2="1001")) or (min2="1001"and

md1='0' and md2="01")then

min1<=min1+1;

end if;

end if;

end process m110;

----------------------------------------------分钟个位

m220:process(clk,sec1,sec2,md1,md2)

begin

if clk'event and clk='1' then

if min2="1001"and (sec1="0101" and sec2="1001")then

min2<="0000";

elsif min2="1001"and (md1='0' and md2="01")then

min2<="0000";

elsif (sec1="0101" and sec2="1001") or(md1='0' and md2="01")then

min2<=min2+1;

end if;

end if;

end process m220;

---------------------------------------------秒十位

s110:process(clk,sec1,sec2)

begin

if clk'event and clk='1' then

if (sec1="0101" and sec2="1001")then

sec1<="0000";

elsif sec2="1001"then

sec1<=sec1+1;

end if;

end if;

end process s110;

--------------------------------------------秒个位

s220:process(clk,sec2)

begin

if clk'event and clk='1' then

if sec2="1001" then

sec2<="0000";

else sec2<=sec2+1;

end if;

end if;

end process s220;

-------------------------------------------时间设置小时部分

sethour1:process(clk,seth2)

begin

if clk'event and clk='1' then

if seth1="0010"and seth2="0011" then

seth1<="0000";

elsif seth2="1001" then

seth1<=seth1+1;

end if;

end if;

end process sethour1;

-------------------------------------------

sethour2:process(clk,md1,md2,seth1)

begin

if clk'event and clk='1' then

if (seth1="0010"and seth2="0011")or seth2="1001"then

seth2<="0000";

elsif md1='1' and md2="10" then

eth2<=seth2+1;

end if;

end if;

end process sethour2;

-------------------------------------------时间设置分钟部分

setmin1:process(clk,setm1,setm2)

begin

if clk'event and clk='1' then

if setm1="0101"and setm2="1001"then

setm1<="0000";

elsif setm2="1001"then

setm1<=setm1+1;

end if;

end if;

end process setmin1;

----------------------------------------------

setmin2:process(clk,md1,md2,setm2)

begin

if clk'event and clk='1'then

if setm2="1001"then

setm2<="0000";

elsif md1='1' and md2="01"then

setm2<=setm2+1;

end if;

end if;

end process setmin2;

--------------------------------------------闹铃

speaker:process(clk1,hou1,hou2,min1,min2)

begin

if clk1'event and clk1='1'then

if seth1=hou1 and seth2=hou2 and setm1=min1 and setm2=min2 then

if(sec2="0000"or sec2="0010" or sec2="0100" or sec2="0110" or sec2="1000" )then

speak<='1';

else speak<='0';

end if;

end if;

end if;

end process speaker;

-------------------------------------------数码管显示

disp:process(sel,md1,hou1,hou2,min1,min2,sec1,sec2,seth1,seth2,setm1,setm2)

begin

if sel="101" then

case h1 is

when "0000"=>dout<="0111111";

when "0001"=>dout<="0000110";

when "0010"=>dout<="1011011";

when others =>dout<="1000000";

end case;

elsif sel="100" then

case h2 is

when "0000"=>dout<="0111111";

when "0001"=>dout<="0000110";

when "0010"=>dout<="1011011";

when "0011"=>dout<="1001111";

when "0100"=>dout<="1100110";

when "0101"=>dout<="1101101";

when "0110"=>dout<="1111101";

when "0111"=>dout<="0000111";

when "1000"=>dout<="1111111";

when "1001"=>dout<="1101111";

when others=>dout<="1000000";

end case;

elsif sel="011" then

case m1 is

when "0000"=>dout<="0111111";

when "0001"=>dout<="0000110";

when "0010"=>dout<="1011011";

when "0011"=>dout<="1001111";

when "0100"=>dout<="1100110";

when "0101"=>dout<="1101101";

when others=>dout<="1000000";

end case;

elsif sel="010" then

case m2 is

when "0000"=>dout<="0111111";

when "0001"=>dout<="0000110";

when "0010"=>dout<="1011011";

when "0011"=>dout<="1001111";

when "0100"=>dout<="1100110";

when "0101"=>dout<="1101101";

when "0110"=>dout<="1111101";

when "0111"=>dout<="0000111";

when "1000"=>dout<="1111111";

when "1001"=>dout<="1101111";

when others=>dout<="1000000";

end case;

elsif sel="001" then

case s1 is

when "0000"=>dout<="0111111";

when "0001"=>dout<="0000110";

when "0010"=>dout<="1011011";

when "0011"=>dout<="1001111";

when "0100"=>dout<="1100110";

when "0101"=>dout<="1101101";

when others=>dout<="1000000";

end case;

elsif sel="000" then

case s2 is

when "0000"=>dout<="0111111";

when "0001"=>dout<="0000110";

when "0010"=>dout<="1011011";

when "0011"=>dout<="1001111";

when "0100"=>dout<="1100110";

when "0101"=>dout<="1101101";

when "0110"=>dout<="1111101";

when "0111"=>dout<="0000111";

when "1000"=>dout<="1111111";

when "1001"=>dout<="1101111";

when others=>dout<="1000000";

end case;

end if;

if md1='0' then---------------计时时间显示和设置模式

h1<=hou1;h2<=hou2;

m1<=min1;m2<=min2;

s1<=sec1;s2<=sec2;

else -------------闹铃时间显示和设置模式

h1<=seth1;h2<=seth2;

m1<=setm1;m2<=setm2;

s1<="1111";s2<="1111";

end if;

end process disp;

------------------------------------------

end;

三、 仿真结果

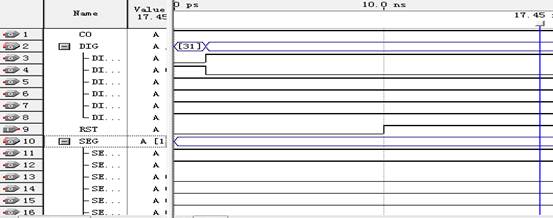

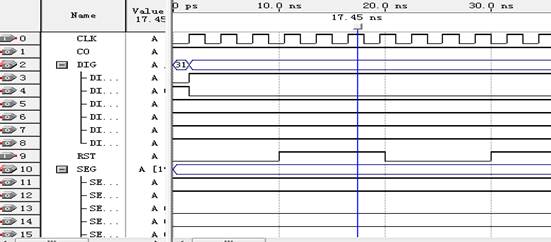

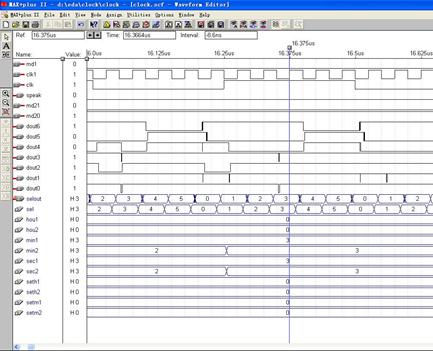

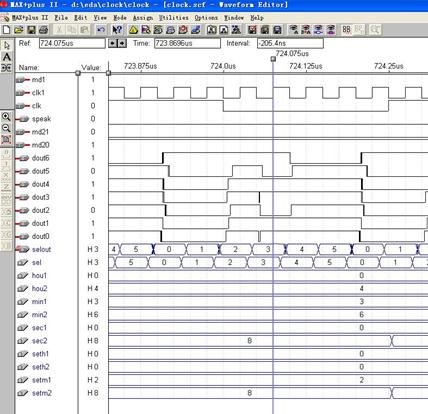

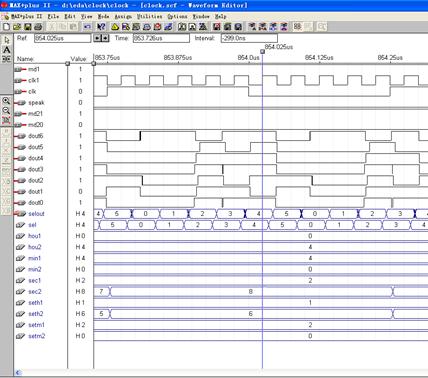

我们将上述VHDL程序通过Max+Plus II进行编译仿真,仿真结果符合我们设计所预想的功能。仿真结果见下图。

图1:正常计时(md1=0,时钟模式)

(所指处,sel值为0,选通数码管秒个位,dout七段码输出sec2,即2)

图2:分钟校正(md1=0,时钟模式)

(所指处,sel值为3,选通数码管分钟十位,dout七段码输出min1,即3)

图3:小时校正(md1=0,时钟模式)

(所指处,sel值为4,选通数码管小时个位,dout七段码输出hou2,即8)

图4:分钟定时(md1=1,闹钟模式)

(所指处,sel值为3,选通数码管分钟十位,dout七段码输出setm1,即2)

图5:小时定时(md1=1,闹钟模式)

(所指处,sel值为4,选通数码管小时个位,dout七段码输出seth2,即6)

四、 结论与收获

在整个设计过程中,通过查阅相关资料,我们一步步建立了对EDA设计的理解。通过解决在编程、调试以及仿真过程中的种种问题,也加深了我们对软件设计环境的熟悉程度。

通过仿真,我们也感性地认识到了曾经忽视的问题,比如器件间信号传递的时延以及产生毛刺会对电路功能实现的影响。而最让我们印象深刻的是一点是,在编程当中,虽然某些程序的结构获得的效果以及软件仿真的结果是一致的,但在实际硬件实现是却会有很大的不同。而这一切,都让我们获益良多。

-

数字钟实验报告

数字钟实验报告课题名称:数字钟的设计与制作组员:姓名:班级:电气信息I类112班实验时间:实验地点:指导老师:一、实验目的:1.学…

-

数字电子时钟实验报告

华大计科学院数字逻辑课程设计说明书题目:多功能数字钟专业:计算机科学与技术班级:网络工程1班***学号:****完成日期:20XX…

-

数字电路数字时钟课程实验报告

数字时钟设计实验报告一设计要求设计一个24小时制的数字时钟要求计时显示精度到秒有校时功能采用中小规模集成电路设计发挥增加闹钟功能二…

-

数字钟设计报告——数字电路实验报告

数字钟设计实验报告专业工程技术系班级电信0901班姓名XX学号XXXXXX数字钟的设计目录一前言3二设计目的3三设计任务3四设计方…

-

EDA数字钟实验报告

EDA实现多功能数字钟实验报告实验EDA实验数字钟一实验任务用FPGA器件和EDA技术实现多功能数字钟的设计已知条件1MAXPlu…

-

【精】数字时钟实验报告

一指标要求1显示时分秒采用24小时制2具有校时功能可以对小时和分单独校时对分校时的时候停止分向小时进位校时时钟源可以手动输入或借用…

-

VHDL数字时钟实验报告

VHDL数字时钟设计一实验目的进一步练习VHDL语言设计工程的建立与仿真的步骤和方法熟悉VHDL语言基本设计实体的编写方法同时在已…

-

EDA数字时钟实验报告

EDA实验报告实验名称EDA多功能数字时钟设计学院电气学院姓名班指导老师EDA多功能数字时钟设计摘要本实验中我们运用EDA课程中所…

-

eda数字钟实验报告

实验四数字钟设计一实验目的1进一步学习更复杂的EDA熟练项目设计更的掌握VHDL语言设计2学习动态数码管的VHDL编程3更加熟练计…

-

电子设计自动化(EDA)_数字时钟程序模块(LED数码管显示)_实验报告

电子设计自动化EDA数字时钟LED数码管显示二实验内容和实验目的16个数码管动态扫描显示驱动2按键模式选择时分秒与闹钟时分调整控制…

-

数字钟实验报告

南昌大学实验报告实验四多功能数字钟设计学生姓名学号专业班级实验类型验证综合设计创新实验日期实验成绩一实验目的1学习综合且较复杂数字…