数字频率计的设计

毕业论文(设计)材料

题 目: 数字频率计的设计

学生姓名: 骆 曼 学生学号: 0908030223 系 别: 电气信息工程学院 专 业: 电子信息工程 届 别: 2013 指导教师: 张 大 雷

一、毕业论文(设计)任务书

二、毕业论文(设计)开题报告

三、毕业论文(设计)评审表

第二篇:数字频率计设计

电子发烧友 电子技术论坛

第2节 数字频率计设计

[学习要求] 了解数字频率计测频率与测周期的基本原理;熟练掌握数字频率计的设计与调试方法及减小测量误差的方法。

[重点与难点]

重点:数字频率计的组成框图和波形图。

难点:时基电路和逻辑控制电路。

[理论内容]

一、数字频率计测频率的基本原理

所谓频率,就是周期性信号在单位时间(1s)内变化的次数。若在一定时间间隔T内测得这个周期性信号的重复变化次数为N,则其频率可表示为

f=N/T (1)

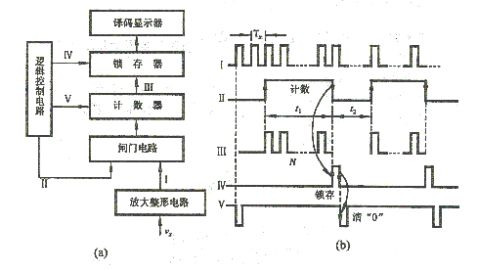

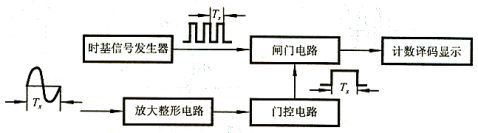

图1 数字频率计的组成框图和波形图

图1(a)是数字频率计的组成框图。被测信号vx经放大整形电路变成计数器所要求的脉冲信号I,其频率与被测信号的频率fx相同。时基电路提供标准时间基准信号II,其高电平持续时间t1=1秒,当l秒信号来到时,闸门开通,被测脉冲信号通过闸门,计数器开始计数,直到l秒信号结束时闸门关闭,停止计数。若在闸门时间1s内计数器计得的脉冲个数为N,则被测信号频率fx=NHz。逻辑控制电路的作用有两个:一是产生锁存脉冲IV,使显示器上的数字稳定;二是产生清“0”脉冲V,使计数器每次测量从零开始计数。各信号之间的时序关系如图1(b)所示。

电子发烧友 电子技术论坛

二、数字频率计的主要技术指标

1、频率准确度

?1?fx?fc=±?+一般用相对误差来表示,即 ?Tffxfc?x

式中,?? ??1?N±1为量化误差(即±1个字误差),是数字仪器所特有的误差,当==TfxNN

闸门时间T选定后,fx越低,量化误差越大;?fc?T为闸门时间相对误差,主要由时=fcT

基电路标准频率的准确度决定,

2、频率测量范围 ?fc1。 ??fcTfx

在输入电压符合规定要求值时,能够正常进行测量的频率区间称为频率测量范围。频率测量范围主要由放大整形电路的频率响应决定。

3、数字显示位数

频率计的数字显示位数决定了频率计的分辨率。位数越多,分辨率越高。

4、测量时间

频率计完成一次测量所需要的时间,包括准备、计数、锁存和复位时间。

三、数字频率计的电路设计与调试

1.基本电路设计

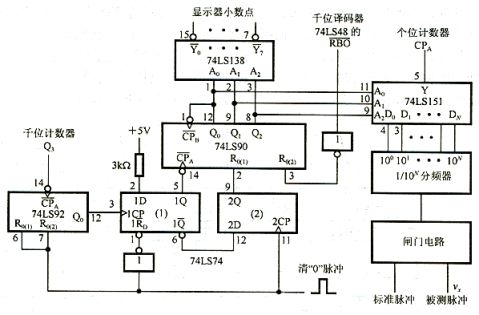

数字频率计的基本框图如图2所示,各部分作用如下。

① 放大整形电路

放大整形电路由晶体管3DG100与74LS00等组成。其中3DGl00组成放大器将输入频率为fx的周期信号如正弦波、三角波等进行放大。与非门74LS00构成施密特触发器,它对放大器的输出信号进行整形,使之成为矩形脉冲。

② 时基电路

时基电路的作用是产生一个标准时间信号(高电平持续时间为1s),由定时器555构成的多谐振荡器产生。若振荡器的频率f0=1/(t1+t2)=0.8Hz,则振荡器的输出波形如图1中

电子发烧友 电子技术论坛的波形II所示,其中t1=1s,t2=0.25s。由公式t1=0.7(R1+R2)C和t2=0.7R2C,可计算出电阻R1、R2及电容C的值。

③逻辑控制电路

根据图1(b)所示波形,在计数信号II结束时产生锁存信号IV,锁存信号IV结束时产生清“0”信号V。脉冲信号IV和V可由两个单稳态触发器74LS123产生,它们的脉冲宽度由电路的时间常数决定。

设锁存信号IV和清“0”信号V的脉冲宽度tw相同,如果要求tw=0.02s,则得tw=0.45RextCext=0.02s。若取Rext=10kΩ,则Cext=tw/0.45Rext=4.4μF。

由74LS123的功能可得,当1RD=1B=1、触发脉冲从1A端输入时,在触发脉冲的负跳变作用下,输出端1Q可获得一负脉冲,其波形关系正好满足图1所示的波形IV和V的要求。手动复位开关S按下时,计数器清“0”。

电子发烧友 电子技术论坛

图2 频率计整机电路图

④ 锁存器

锁存器的作用是将计数器在1s结束时所计得的数进行锁存,使显示器上能稳定地显示此时计数器的值。如图1(b)所示,1s计数时间结束时,逻辑控制电路发出锁存信号IV,将此时计数器的值送译码显示器。

电子发烧友 电子技术论坛 选用两个8位锁存器74L273可以完成上述功能。当时锁存信号CP的正跳变来到时,锁存器的输出等于输入,即。从而将计数器的输出值送到锁存器的输出端。高电平结束后,无论D为何值,输出端的状态仍保持原来的状态不变。所以在计数期间内,计数器的输出不会送到译码显示器。

2、扩展电路的设计

按照上述方法所设计的数字频率计电路,测量的最高频率只能为9.999kHz,完成一次测量的时间约1.25s。若被测信号频率增加到数百千赫兹或数兆赫兹时,则需要增加频率范围扩展电路。

图3 频率范围量程扩展电路

频率范围扩展电路如图3所示,该电路可实现频率量程的自动转换。其工作原理是:当被测信号频率升高,千位计数器已满,需要升量程时,计数器的最高位产生进位脉冲Q3,送到由74LS92与两个D触发器共同构成的进位脉冲采集电路。第一个D触发器的1D端接高电平,当Q3的下跳沿来到时,74LS92的Q0端输出高电平,则第一个D触发器的1Q端产生进位脉冲并保持到清“0”脉冲到来。该进位脉冲使多路数据选择器74LS151的地址计数器74LS90加1,多路数据选择器将选通下一路输入信号,即比上一次频率低10倍的分频信号,由于此时个位计数器的输入脉冲的频率比被测频率fx低10倍,故要将显示器的数乘以10才能得到被测频率值,这可以通过移动显示器上小数点的位置来实现。如图3所示,若被测

电子发烧友 电子技术论坛信号不经过分频(100输出),显示器上的最大值为9.999kHz,若经过101分频后,显示器上的最大值为99.99 kHz,即小数点每向右移动一位,频率的测量范围扩大10倍。

进位脉冲采集电路的作用是使电路工作稳定,避免当千位计数器到8或9时,产生小数点的跳动。第二个D触发器用来控制清“0”,即有进位脉冲时电路不清“0”,而无进位时则清“0”。

当被测频率降低需要转换到低量程时,可用千位(最高位)是否为零来判断。在此利用千位译码器74LS48的灭零输出端RBO,当RBO端为零时,输出为零,这时就需要降量程。因此,取其非作为地址计数器74LS90的清“0”脉冲。为了能把高位多余的零熄灭,只需把高位的灭零输入端RBI,同时把高位的RBO与低位的RBI相连即可。由此可见,只有当检测到最高位为“0”,并且在该1秒钟内没有进位脉冲时,地址计数器才清“0”复位,即转换到最低量程,然后再按升量程的原理自动换档,直到找到合适的量程。若将地址译码器74LS138的输出端取非,变成高电平以驱动显示器的小数点h,则可显示扩展的频率范围。

四、数字频率计测周期的基本原理

当被测信号的频率较低时,采用直接测频方法由量程误差引起的测频误差太大,为了提高测低频时的准确度,应先测周期Tx,然后计算fx=1/Tx。

数字频率计测周期的原理框图如图4所示。被测信号经过放大整形电路变成方波,加到门控电路产生闸门信号,如Tx=10ms,则闸门打开的时间也为10ms,在此期间内,周期为Ts的标准脉冲通过闸门进入计数器计数。若Tx=1us,则计数器计得的脉冲数N=Tx/Ts =10000个。若以毫秒(ms)为单位,则显示器上的读数为10.000。

以上分析可见,频率计测周期的基本原理正好与测频相反,即被测信号用来控制闸门电路的开通与关闭,标准时基信号作为计数脉冲。

图4 数字频率计测周期的基本原理

电子发烧友 电子技术论坛

-

数字频率计课程设计报告

赣南师院物理与电子信息学院数字电路课程设计报告书姓名班级学号时间数字频率计的设计一设计任务和要求1能够测量正弦波三角波锯齿波矩形波…

-

简易数字频率计课程设计报告

摘要在电子技术中频率是最基本的参数之一并且与许多电参量的测量方案测量结果都有十分密切的关系因此频率的测量显得更为重要测量频率的方法…

-

简易数字频率计设计实验报告 季克宇

电子线路课程设计报告第1页共14页电子线路课程设计报告姓名季克宇学号110404130专业通信工程日期20xx1010南京理工大学…

-

数字电路课程设计——数字频率计设计报告

I在电子技术中频率是一个重要参量应用计数法原理制成的数字式频率测量仪器具有精确度高测频范围宽便于实现测量过程自动化等一系列突出特点…

-

简易数字频率计课程设计报告 .

目录第一章概述11数字频率计功能及特点12数字频率计应用意义第二章设计方案21设计指标与要求22设计原理23方案论证第三章数字频率…

-

《EDA技术》数字频率计课程设计报告报

EDA技术课程设计报告题目数字频率计专业电子信息工程班级0702姓名指导教师高金定二0一0年6月24日020xx32820xx32…

- 基于单片机的频率计设计开题报告

-

基于51单片机的数字频率计设计报告

目录摘要.3关键词.3正文.41概述.42总体设计方案.52.1软件.52.2设计思路.53系统软件设计.53.1主板说明.53.…

-

基于51单片机的数字频率计设计报告

目录摘要.3关键词.3正文.41概述.42总体设计方案.52.1软件.52.2设计思路.53系统软件设计.53.1主板说明.53.…

-

简易数字频率计设计实验报告1赵勇

南理工紫金学院课题实验设计报告学生姓名赵勇学号专业电气工程及其自动化题目电子综合应用实践1课程设计任务书2课程设计任务书1封面课程…