数字电子技术课程设计报告(数字钟)

目录

一. 设计目的……………………………………… 1

二. 实现功能……………………………………… 1

三. 制作过程……………………………………… 1

四. 原理框图……………………………………… 3

4.1 数字钟构成……………………………………… 3

4 .2设计脉冲源……………………………………… 4

4.3 设计整形电路…………………………………… 5

4.4 设计分频器……………………………………… 5

4.5 实际计数器……………………………………… 6

4.6 译码/驱动器电路的设计…………………………… 7

4.7 校时电路………………………………………… 8

4.8 整点报时电路…………………………………… 9

4.9 绘制总体电路图………………………………… 10

五. 具体实现……………………………………… 10

5.1电路的选择……………………………………… 10

5.2集成电路的基本功能……………………………… 10

5.3 电路原理………………………………………… 11

六. 感想与收获……………………………………… 12

七. 附 录……………………………………… 14

数字电子技术课程设计报告

一、设计目的

数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。

数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能。诸如定时自动报警、按时自动打铃、时间程序自动控制、定时广播、定时启闭电路、定时开关烘箱、通断动力设备,甚至各种定时电气的自动启用等,所有这些,都是以钟表数字化为基础的。因此,研究数字钟及扩大其应用,有着非常现实的意义。

石英数字钟,具有电路简洁,代表性好,实用性强等优点,在数字钟的制作中,我们采用了传统的PCMS大规模集成电路为核心,配上LED发光显示屏,用石英晶体做稳频元件,准确又方便。

二、实现功能

① 时间以12小时为一个周期;

② 显示时、分、秒;

③ 具有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间;

④ 计时过程具有报时功能,当时间到达整点前10秒进行蜂鸣报时;

⑤ 为了保证计时的稳定及准确须由晶体振荡器提供表针时间基准信号。

三、制作过程

1.确立电子数字计时器的制作思路

要想构成数字钟,首先应有一个能自动产生稳定的标准时间脉冲信号的信号源。还需要有一个使高频脉冲信号变成适合于计时的低频脉冲信号的分频器电路,即频率为1HZ的“秒脉冲”信号。经过分频器输出的秒脉冲信号到计数器中进行计数。由于计时的规律是:60秒=1分,60分=1小时,24小时=1天,这就需要分别设计60进制,24进制,(或12进制的计时器,并发出驱动AM;PM的标志信号)。各计数器输出的信号经译码器/驱动器送到数字显示器对应的笔划段,使得 “时”、“分”、“秒”得以数字显示。

任何数字计时器都有误,因此应考虑校准时间电路,校时电路一般采用自动快调和手动调整,“自动快调”是利用分频器输出的不同频率脉冲使得显示时间自动迅速的得到调整。“手动调整” 是利用手动的节拍调整显示时间。

2.查阅资料绘出各部分的电路图(详见原理框图)

数字计时器的设计方法:

(1)设计脉冲源

(2)设计整形电路

(3)设计分频器

(4)设计计数器

(5)译码器/驱动器

(6)设计校时电路

3. 按所设计的电路去选择、测试好元器件、并装配成为产品

4. 准备设计论文答辩

四、原理框图

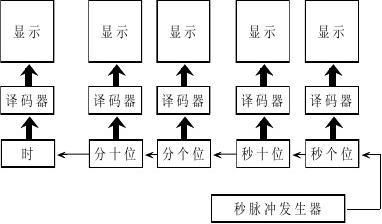

1.数字钟的构成

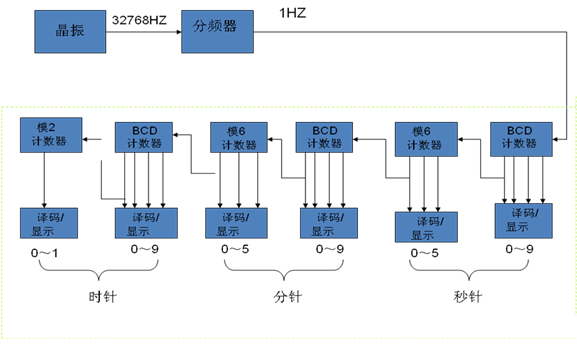

数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ时间信号必须做到准确稳定。通常使用石英晶体振荡器电路构成数字钟。

数字钟组成框图

2.设计脉冲源

自激式振荡电路有:自激多谐振荡器,激间歇振荡器这次我们选择晶体振荡器原因如下: 由于通常要求数字钟的脉冲源的频率要十分稳定、准确度高,因此要采用石英晶体振荡器,其他的多谐振荡器难以满足要求。石英晶体不但频率特性稳定,而且品质因数很高,有极好的选频特性。晶体振荡器电路给数字钟提供一个频率稳定准确的32768Hz的方波信号,可保证数字钟的走时准确及稳定。石英晶体振荡器的频率取决于石英晶体的固有频率,与外电路的电阻电容的参数无关一般情况下,晶振频率越高,准确度越高,但所用的分频级数越多,耗电量就越大,成本就越高,在选择晶体时应综合考虑。

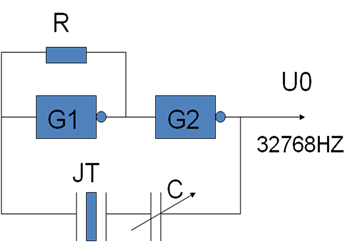

一般输出为方波的数字式晶体振荡器电路通常有两类,一类是用TTL门电路构成;另一类是通过CMOS非门构成的电路,本次设计采用了后一种。如图(b)所示,由CMOS非门U1与晶体、电容和电阻构成晶体振荡器电路,U2实现整形功能,将振荡器输出的近似于正弦波的波形转换为较理想的方波。输出反馈电阻R1为非门提供偏置,使电路工作于放大区域,即非门的功能近似于一个高增益的反相放大器。电容C1、C2与晶体构成一个谐振型网络,完成对振荡频率的控制功能,同时提供了一个180度相移,从而和非门构成一个正反馈网络,实现了振荡器的功能。由于晶体具有较高的频率稳定性及准确性,从而保证了输出频率的稳定和准确。

(a) CMOS 晶体振荡器(仿真电路)

3.设计整形电路

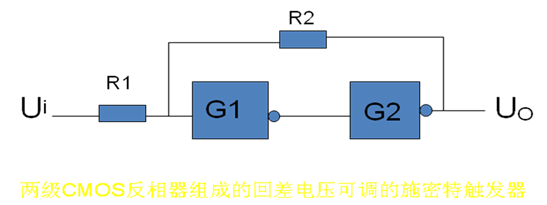

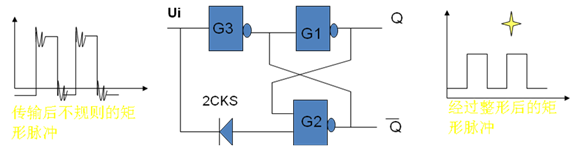

由于晶体振荡器输出的脉冲是正弦波或是不规则的矩形波,因此必须经整形电路整形。我们已学过的脉冲整形电路有以下几种:削波器、门电路、单稳态电路、双稳态电路、施密特触发器等。通过查阅资料主要使用施密特触发器:

门电路组成的整形电路

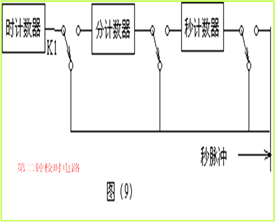

4. 设计分频器

分频器 —— 能将高频脉冲变换为低频脉冲,它可由触发器以及计数器来完成。由于一个触发器就是一个二分频器,N个触发器就是 2N个分频器。如果用计数器作分频器,就要按进制数进行分频。例如十进制计数器就是十分频器,M进制计数器就为M分频器。若我们从市场上购买到石英晶体振荡器其频率为32768HZ,要想用该振荡器得到一个频率为1HZ的秒脉冲信号,就需要用分频器进行分频,分频器的个数为2N =32768HZ,N =15 即有15个分频器。这样就将一个频率为23768HZ的振荡信号降低为1HZ的计时信号,这样就满足了计时规律的需求:60秒=1分钟,60分=1小时,24小时=1天。

5.设计计数器

计数器的设计,以触发器为单元电路,根据进制按有权码或无权码来编码,采用有条件反馈原理来构成。当 “小时” 的十位为2;个位为3时,只要个位数 “分” 有进位时,就应使十位的“小时 ”的位数归零,因此24小时进制计数器要采用有条件反馈的设计。(12进制计数器也同理);但应在归零的同时发出驱动AM(上午)、PM(下午)标志的信号。

按规律,一般设计计数器的方法

秒部分:个位选用模10计数器;十位选用模6计数器

分部分:个位选用模10计数器;十位选用模6计数器

小时部分:模12计数器;或模24计数器

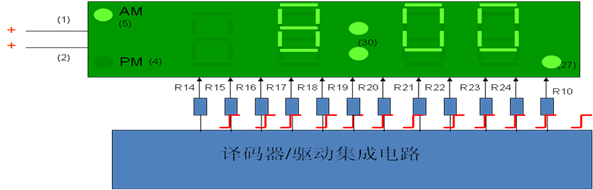

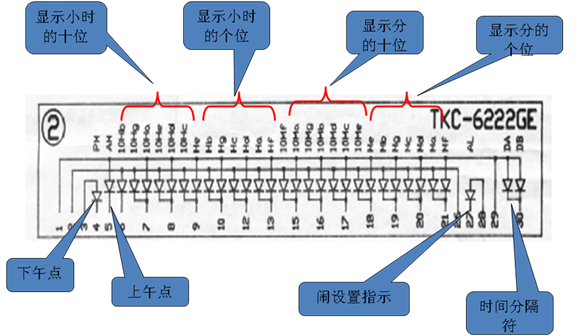

6. 译码/驱动器电路的设计

在数字系统中常常需要将测量或处理的结果直接显示成十进制数字。为此,首先将以BCD码表示的结果送到译码器电路进行译码,用它的输出去驱动显示器件,由于显示器件的工作方式不同,对译码器的要求也就不同,译码器的电路也不同。数字显示的器件的种类:荧光管、辉光管、发光二极管、液晶显示屏等.

译码器电路 :此次我们选择的是LED共阳极发光二极管显示器

:此次我们选择的是LED共阳极发光二极管显示器

显示电路如下:

显示电路如下:

原理图

原理图

7.校时电路

校时电路是计时器中不可少的一部分因为当即时间与计时器时间不一致时,就需要校时电路予以校正。校时电路有两种方案:第一、校时用的脉冲可选用频率较高的不等的几种脉冲,从计数器的总输入端(秒计数器的第一级输入端)送入。

第二、校时用的脉冲,分别将秒脉冲送到“计小时”的计数器的输入端, “计分”的计数器输入端,但校时、校分时,应将原计数回路关闭或断开。校秒时可采用关闭或断开秒计数器的脉冲信号输入端使其停止计时

8.整点报时电路

电路应在整点前10秒钟内开始整点报时,即当时间在59分50秒到59分59秒期间时,报时电路报时控制信号。

当时间在59分50秒到59分59秒期间时,分十位、分个位和秒十位均保持不变,分别为5、9和5,因此可将分计数器十位的QC和QA 、个位的QD和QA及秒计数器十位的QC和QA相与,从而产生报时控制信号。

实现方式:

9. 绘制总体电路图

五:具体实现

1、电路的选择:

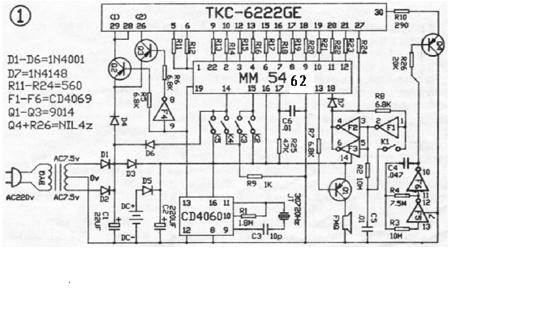

我们采用了传统的PCMS大规模集成电路为核心,配上LED发光显示屏,用石英晶体作为稳频元件,准确又方便。

数字钟专用集成块如下:

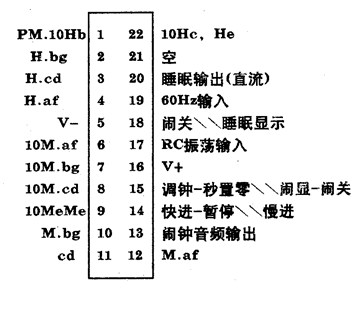

a. 译码/驱动电路:LM8361,M8560,LM8569,TMS3450NL,MM5457,MM5462集成电路,因为它在所有型号中静态功耗最低。其管脚图见图(12)

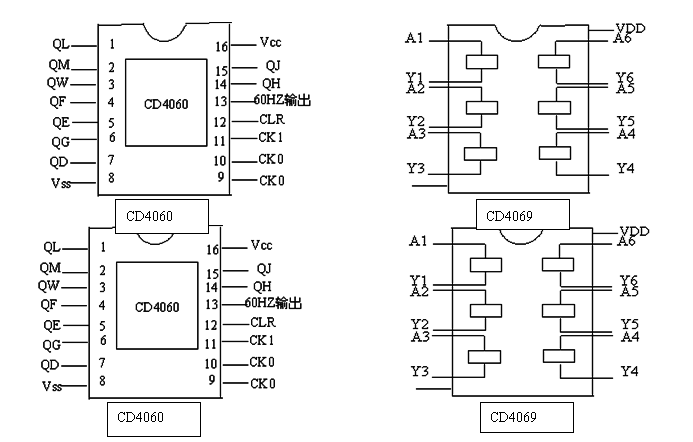

b. 分频器:我们采用了CD4060。

c.反相器: 我们选用了CD4069(内含有六个反相器)。

2、集成电路的基本功能

(1)CD4060:它是一个十四级二分频器,它所产生的信号频率为30720HZ,经九级两二分频后,得到一个60HZ的脉冲信号,见图。

(2)CD4069反相器: F1—F6六个反相器,通过外接电路去控制各电路的工作状态,管脚见图:

(3)MM5462: 它是集译码/驱动电路为一体,它是60HZ时基24小时专用集成电路。1-4,6-12,22十三个端子是显示笔划输出的,1脚是四个笔划,其余每脚输出二个笔划,16脚为正电源,5脚为负电源,20脚睡眠输出是直流信号,由17脚动和关闭,由13脚调整至需要值,最大值59分钟倒计时。17脚是内部振荡器RC输入端,该振荡信号一是作为外部时基的备用,二是13闹输出的信号源。在我们选用的这套套件没有用20脚的睡眠功能。19脚为时基信号输入脚。14、15、18脚是操作控制端,若接高低电平各有不同的功能。值得注意的是所有的输出端均为低电平有效。

(3)MM5462: 它是集译码/驱动电路为一体,它是60HZ时基24小时专用集成电路。1-4,6-12,22十三个端子是显示笔划输出的,1脚是四个笔划,其余每脚输出二个笔划,16脚为正电源,5脚为负电源,20脚睡眠输出是直流信号,由17脚动和关闭,由13脚调整至需要值,最大值59分钟倒计时。17脚是内部振荡器RC输入端,该振荡信号一是作为外部时基的备用,二是13闹输出的信号源。在我们选用的这套套件没有用20脚的睡眠功能。19脚为时基信号输入脚。14、15、18脚是操作控制端,若接高低电平各有不同的功能。值得注意的是所有的输出端均为低电平有效。

、

3、电路原理:(见图原理方框图)

变压器将交流220V电压,变为双7.5V交流低电压,经全波整流后路经D4供显示屏驱动电路,而另一路经滤波后供主电路。由于时钟需要脉冲源,我们选用了JT,R1,C3和CD4060内部的两个反相器组成的晶体振荡器,目的是为了提脉冲源的稳定度,而脉冲源产生的波形不是规则的矩形波,因此,需经整形器整形后,送到下一级,由于脉冲信号源的频率较高,经CD4060九级分频及计数后变换低频脉冲信号。由13脚得到60HZ的脉冲信号一路送入MM5461的19脚,另一路去控制由F4,Q2,Q3组成的显示屏驱动电路。由于F4的倒相作用,使Q2,Q3和时基信号交替导通,形成间歇点亮显示屏,使它工作在正常状态。

当60HZ的信号从MM5461的19脚进入后,由控制电路各部分电路的正常工作经译码与驱动电路去控制显示屏各个应亮的端。

F1,F2,F3,R2,R8,C5,K1组成了一个“电子自锁式开关”,每控一次K1,F2的输出状态会改变,一路去控制MM5461的18脚,另一路去驱动显示屏右下点的发光二极管以指示该功能的工作状态。“亮”表示“闹钟时间已设置”,“灭”表示“闹设置取消”。

R7,Q1,FMQ组成闹输出放大电路,控制信号由MM5461的13脚输出。当响闹时,按下K5可使闹暂停并延时九分钟再闹,还可多次使用报时延时,响闹总时长59分钟。

由于MM5461无秒信号输出,故用F5,F6,R3,R4,C4组成秒信号发生器,经Q4去驱动显示屏中间的“冒号”闪动。电路中各开关的功能:

K1:闹钟时间的设置开关。K1+K5快调闹时间的设置。 K1+K4慢调闹时间的设置

K2:时间的设置开关。 K2+K5 快调时间的设置 K2+K4慢调时间的设置。

K3:闹钟时间显示开关。单击K3可显示事先所设置的报时的时间

K4:慢调时间开关

K5:快调时间开关/暂停/显示

电路中,R10(1K)的作用,是防止开关操作工作时,正负电源短路。R13,R27,R9为限流电阻,它们决定显示亮度。

六:感想与收获

这次的比赛是我们三个人一起参加的,在比赛前的一段时间里,我们三个人的收获很大,具体有三点:

(1)有利于我们学习能力的提高。这里所说的学习能力包括获取资料的能力、理解前人思路的能力、系统设计能力、动手能力、分析排除故障能力、表达能力等很多方面,而这段时间的经历,我们提高都很大。

(2)有利于我们团队精神的培养。在课堂之外实际的工作中,我们三人一般都要合作共同完成某一项目,这就非常需要团队精神,而这一点在课堂常规教学中得到的锻炼是很有限的。三个人必须互相信任、互相配合、分工合作,在顺境时小组成员要相互提醒保持冷静,逆境时要相互鼓励共度难关,出现问题时不能相互埋,这些与课堂教学强调独立性是有明显区别的。

(3)有利于我们各种能力的锻炼。第一、不够细心比如由于粗心大意焊错了线,第二,是在学习态度上,这次培训是对我的学习态度的一次检验。我第一次体会到要作一名电子设计师,要求具备的首要素质是严谨。我们这次制作所遇到的多半问题多数都是由于我们不够严谨。第三,在做人上,我认识到,无论做什么事情,只要你足够坚强,有足够的毅力与决心,有足够的挑战困难的勇气,就没有什么办不到的。

电设赛场风云涌,各路英豪皆争雄。

今朝罢去怀壮志,来届电赛再显锋!

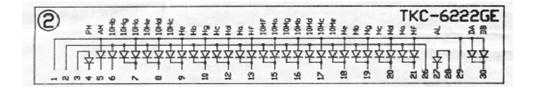

七:附录电路原理总图:

附录二、LED显示屏电路原理图

附录二、LED显示屏电路原理图

第二篇:数字电子技术课程设计数字钟的设计与制作

数字钟的设计与制作

班 级: 姓 名: 学 号: 组 别: 同组人:

一、设计目的

1、掌握计数、译码等芯片的逻辑功能及使用方法;

2、掌握脉冲产生电路的应用。

3、了解数字钟的组成及工作原理;

4、熟悉集成电路的引脚安排;

5、了解面包板及其接线方法;

二、设计要求

1、显示时(1-12)、分(0-59)、秒(0-59);

2、有元器件选择及参数计算;

3、画出总体接线图;

4、自行装配和调试,并能发现问题和解决问题;

5、编写设计报告,写出设计与制作的全过程,有心得体会。

三、设计原理

1、数字钟的工作原理与构成

数字钟是一个对标准1Hz频率进行计数的计数电路。可用555定时器构成秒脉冲发生器,对其计数,构成秒、分、时的不同进制,然后译码显示。总体框图如图所示。

2、秒脉冲发生电路:555定时器构成多谐振荡器。

3、时、分、秒计数器电路:74LS161

4、译码、显示电路:74LS48,共阴极数码管

四、总结

1、设计过程中遇到的问题及解决方法

2、设计体会

五、总体接线图

注意事项:

1、面包板使用说明

拉线时,尽量将线紧贴面包板,把线成直角,避免交叉,也不要跨越元件。 不能飞线、走高架桥;最后制作的美观程度也算一项计分标准。

3-4-3 4-3-4

2、自备电源,可用3节5号电池,新电池可调试2个小时,电池电压过低,也可能造成结果不正确。若用直流电源,注意安全。

3、设计地点:自定 调试地点:自定或电子实验室

4、分组:每班分9组,自由结合,每组至少3人,最多4人。

5、一个组可以只画一张接线图,设计报告每人一份。

6、在实验室调试时,不允许私自拿走实验室的物品(万用表)

7、调试时注意的问题

1)容易出现故障为接触不良。大家要细心、耐心。

a)集成块引脚方向预先弯好对准面包板的金属孔,再小心插入。

b)导线的剥线长度与面包板的厚度相适应(比板的厚度稍短)。

c)导线的裸线部分不要露在板的上面,以防短路。

d)导线要插入金属孔中央。

插线时,不能把绝缘皮插入过深,有可能顶开金属片,造成接触不良,也不能将金属导线露在外面,造成短路或接触不良。

可能有些面包板内部有些孔断开了,遇见这种情况,只能通过万用表查。

2)接线时首先确保可靠的电源和接地。

3)注意芯片的控制引脚必须正确接好。

4)检查故障时除测试输入、输出信号外,要注意电源、接地和控制引脚。

5)要注意芯片引脚上的信号与面包板上插座上信号是否一致(集成块引脚与面包板常接触不良)。

6)为了便于测试,可将1Hz信号直接输入到各级计数器。

10、回去后先设计原理图,也就是设计报告的前三项,可以先写出来,12号下午2点半每组派组长去电子实验室领设计用品,清单如下,领用时,核对清楚,设计过程中,工具和芯片若出现人为损坏或丢失,要找吴老师购买。

11、制作成功并写完报告即可答辩。

《数字电子技术》课程设计所需用品表

领用人签名: 学 院:专业班级: 联系电话:

-

数字电子技术课程设计报告

吉林建筑大学电气与电子信息工程学院数字电子技术课程设计报告设计题目:数字钟的电路设计专业班级:电气112班学生姓名:学号:指导教师…

-

数字电子技术课程设计报告(数字钟)

目录一设计目的1二实现功能1三制作过程1四原理框图341数字钟构成342设计脉冲源443设计整形电路544设计分频器545实际计数…

-

数 字 电 路 课 程 设 计 报 告

数字电路课程设计报告课题名称:篮球竞赛30秒计时器姓名:学号:专业班级:通信工程1指导教师:设计日期:20##年1月5日摘要:随着…

-

数字电路课程设计电子钟设计报告[1]

数字电路课程设计总结报告题目数字钟设计专业班级学生姓名学号指导教师20xx年12月15日目录一设计任务设计课题功能要求二设计框图及…

-

数字电子技术课程设计报告(样例)

大庆师范学院数字电子技术课程设计报告设计课题基于VHDL自动售货姓名杨浩北学院物电学院专业电子信息工程班级08级2班学号20xx0…

-

数字电路课程设计总结报告

数字电路课程设计总结报告题目:交通灯控制器1、设计背景2、设计任务书3、设计框图及总体描述4、各单元设计电路设计方案与原理说明5、…

-

数字电路课程设计比赛计时器总结报告 - 副本

数字逻辑电路设计课程设计总结报告题目指导教师姓名学号班级日期目录一设计任务书3一设计课题3二功能要求3二设计框图及整机概述3一原理…

-

数字电路课程设计报告

天津职业技术师范大学汽车与交通学院电子技术课程设计报告同组学生姓名学号杨帅11杨启瑞03陈敏18班级汽电1001班任务分工电路设计…

- 数字电子技术实验报告格式

-

数字电子技术 课程设计报告 电梯控制2

电子技术课程设计课题名称电梯控制学院电气学院专业电子信息工程姓名指导教师谢贝贝学号目录摘要2第一章设计目的及意义31目的32意义3…

-

数字电路课程设计总结报告

数字电路课程设计总结报告题目数字钟设计专业班级学生姓名学号指导教师日期20xx年12月11目录一设计任务1一设计课题1二功能要求1…