数字逻辑电路实验报告

数字逻辑电路实验报告

——计数器设计与应用

学院:电 信 学 院

班级:电子72班

姓名:冯天宇

学号:07051042

日期:20##年12月31日

一、实验目的:

1.全面、系统的认识与提高《数字逻辑》课程的学习。

2.熟悉和掌握EDA软件(Quartus II 6.0)设计调试电路的方法。

3.通过实验,提高运用数字逻辑电路解决实际问题的能力,并使学生更深入的理解所学知识 。

4. 用D触发器设计同步十六进制加法计数器。

5. 用74LS163(同步清零)设计一个六十进制计数器。

6.用74LS163或74LS190设计24小时制计时器。

二、设计电路及说明:

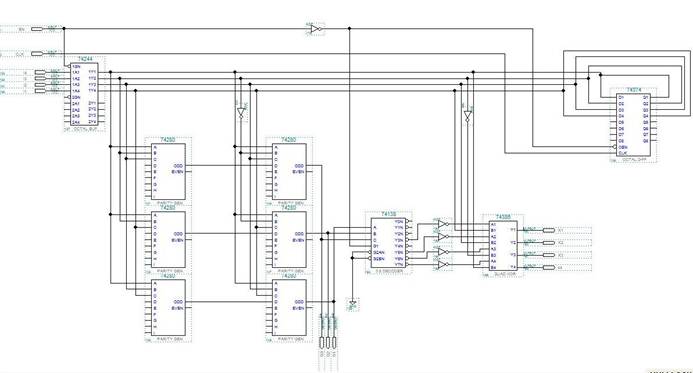

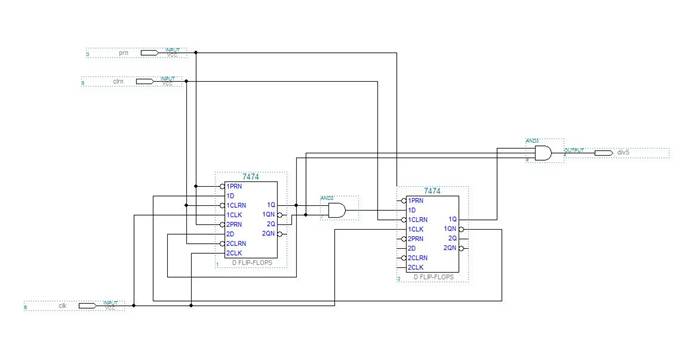

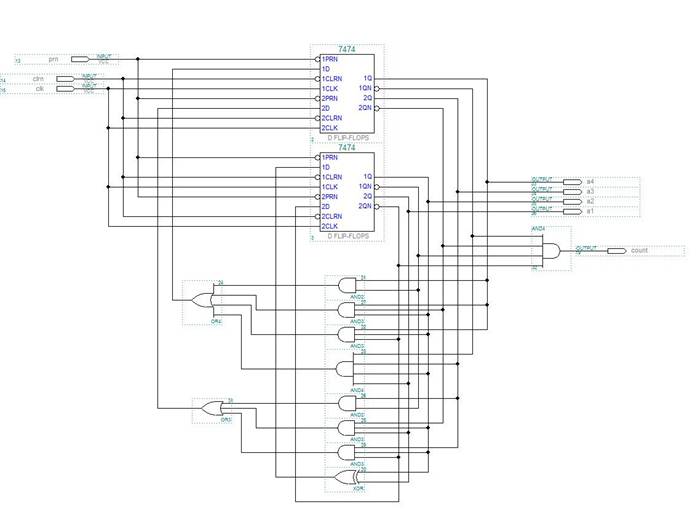

1. 用D触发器设计同步十六进制加法计数器。

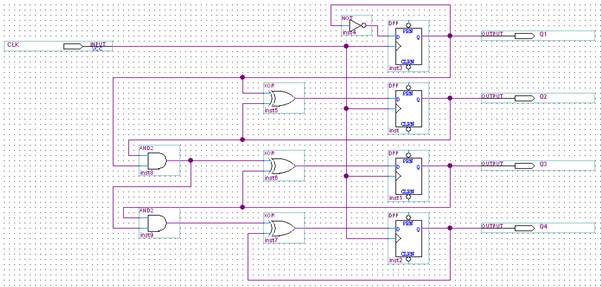

电路如下:

所用器件:2个或门,3个异或门,1个非门,4个D触发器。

同步计数器中,所有触发器的时钟输入端均接受统一计数脉冲并同时产生进位信号,进位信号需要用控制门加以控制。

图中:D1=/Q1 D2=Q1+Q2 D3=(Q2·Q1) +Q3 D4=(Q3·Q2·Q1) +Q4

从上述D的表达式可以看出,当Qi-1,Qi-2,……,Q1均为1时,再来一个计数脉冲,则产生至第i位触发器的进位信号,Qi将变反;否则Qi保持不变。

仿真结果如下:

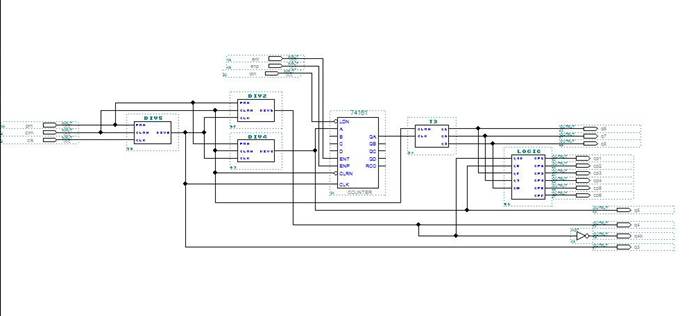

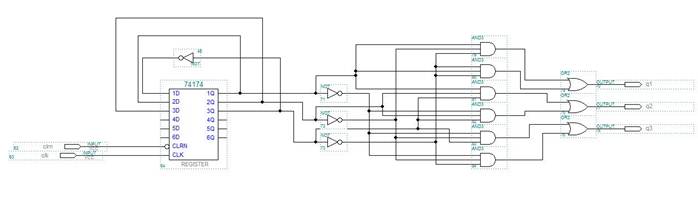

2. 用74LS163(同步清零)设计一个六十进制计数器:

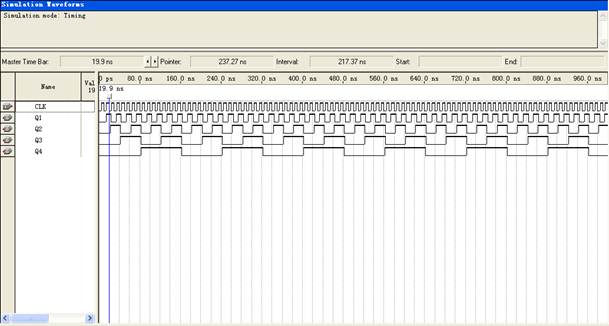

电路如下:

所用器件:2个与非门,2个74LS163同步计数器。

说明:

74LS163是四位同步二进制加法计数器,同步加载和清零,ENP和ENT为计数使能端。

当给CLK一个脉冲时,左侧的74LS163计数器加1。当它的QD和QA同时为1时,左侧的与非门输出低电压,这正好使低有效的CLRN有效,于是左侧的74LS163清零完成跳跃。每跳跃一次从0-9计数,容易知道左侧的74LS163是十进制计数器。

同理,当左侧的74LS163每完成一次跳跃,右侧的74LS163加1。当它的QC和QA同时为1时,右侧的与非门输出低电压,这正好使低有效的CLRN有效,于是右侧的74LS163清零完成跳跃。每跳跃一次从0-5计数,容易知道右侧的74LS163是六十进制计数器。

仿真结果如下:

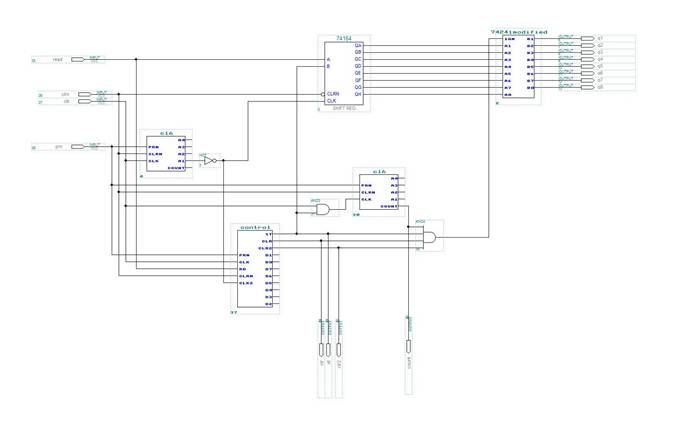

3. 用74LS163或74LS190设计24小时制计时器:

设计要求:

1 实现24小时计时。

2 能够进行校时操作。

分析:

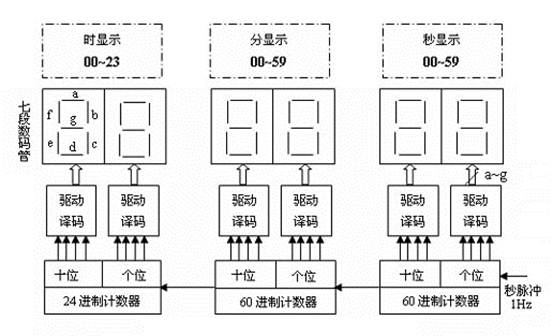

24小时计时器需用3个计时电路,分别为时计时电路、分计时电路和秒计时电路。根据计时要求,时计时电路应为24进制计数器,分计时电路和秒计时电路应为60进制计数器。

结构框图如下:

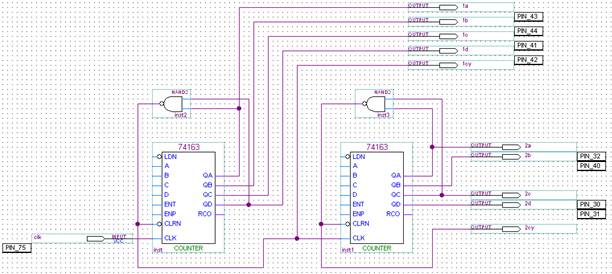

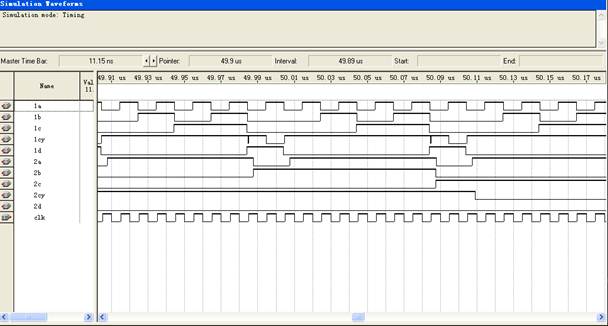

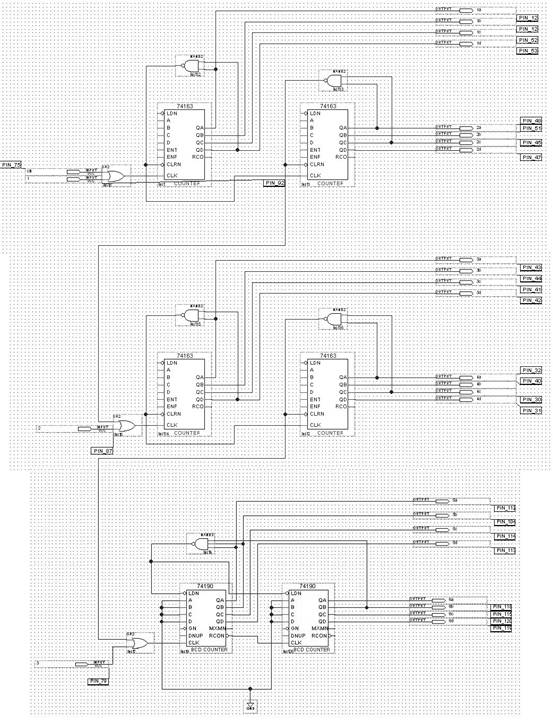

电路如下:

所用器件:3个或门,5个与非门,4个74LS163同步计数器,2个74LS190同步计数器。

说明:

74LS163是四位同步二进制加法计数器,同步加载和清零,ENP和ENT为计数使能端。74LS190是BCD十进制同步加/减计数器,异步加载,Down/Up是加减控制端,GN 是计数使能端。74LS163计数从0到15,74LS190计数从0到9。

电路图中由上到下分为三部分:第一部分是最上面的两个74LS163,它们组成一个六十进制加法计数器,用来计数秒;第二部分是中间的两个74LS163,它们也组成一个六十进制加法计数器,用来计数分钟;第三部分是下面的两个74LS190,它们组成一个二十四进制加法计数器,用来计数小时。

当给CLK输入1Hz的方波信号时,计数器由秒到分钟再到小时逐位进位,从而完成计时的功能。

时钟设置:

电路图的左边有三个或门,每一个或门的输入分别为前一个低位的进位和一个用来设置时钟的信号输入端。要设置时钟时,停止对CLK输入信号,将这三个或门上的设置时钟信号输入端分别接到三个按键上。这样,每按键一次,相应的秒、分、时位上就加一,从而可以达到设置时钟的目的。

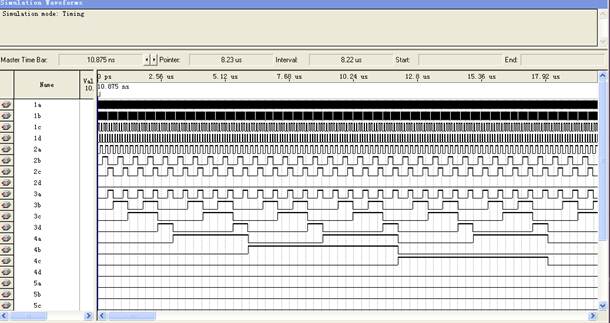

仿真结果如下:

三、思考题:

1、比较同步与异步计时的区别:

同步计时:各触发器状态的改变受同一个时钟脉冲控制,与时钟脉冲同步,即电路在同一时钟控制下,同步改变状态。在两个时钟脉冲之间,即使输入信号变化,电路状态也不会改变。

异步计时:没有统一的时钟脉冲使整个系统同步工作,输入直接引起状态改变。

在本实验中,用D触发器实现的是同步计数器,四个D触发器由同一个CLK控制;用JK触发器实现的是异步计数器,CLK仅加在低位触发器,高位时钟端由低位输出状态控制。

2、比较同步与异步加载、清零的区别

同步加载/清零:当时钟信号的上升沿或下降沿来临时,加载/清零信号才起作用,若没有时钟脉冲,即使加载/清零端有效,也不能完成加载/清零功能。

异步加载/清零:只要加载/清零端有效,且使能端有效,便开始执行操作,不必等待跳变沿的到来。

四、实验总结:

本实验设计很有意义,让我了解到了数字逻辑电路的实际应用,为以后的学习和工作做了铺垫。通过自己设计,也增强了动手能力。在不断的发现问题、解决问题中自我成长。这个问题从设计到仿真,再到硬件上实现花费了很多时间,期间出现了很多问题,有一些原理性的错误我很快能检查出来。但是,遇到的一些随机发生的问题却有些奇怪,比如仿真的时候很正常但是下载到芯片上实施时却出现了错误(加法计数器变成了减法器),但是在未修改任何东西的情况下,重新下载程序结果又好了……

之后,我想了想这些问题,觉得可能是由于系统地稳定性、初值设定或是外界环境如静电等的影响造成的。

通过本次实验,我基本掌握了QuartusII6.0进行EDA设计的基本步骤和调试的基本方法,为以后的学习和工作做了坚实的铺垫,也提高了我发现问题和解决问题的能力。除此之外,我对所学的数字逻辑的理论知识也有了更深入的理解和认识。

第二篇:数字逻辑电路实验报告

数字逻辑电路实验报告

实验二:16进制译码器

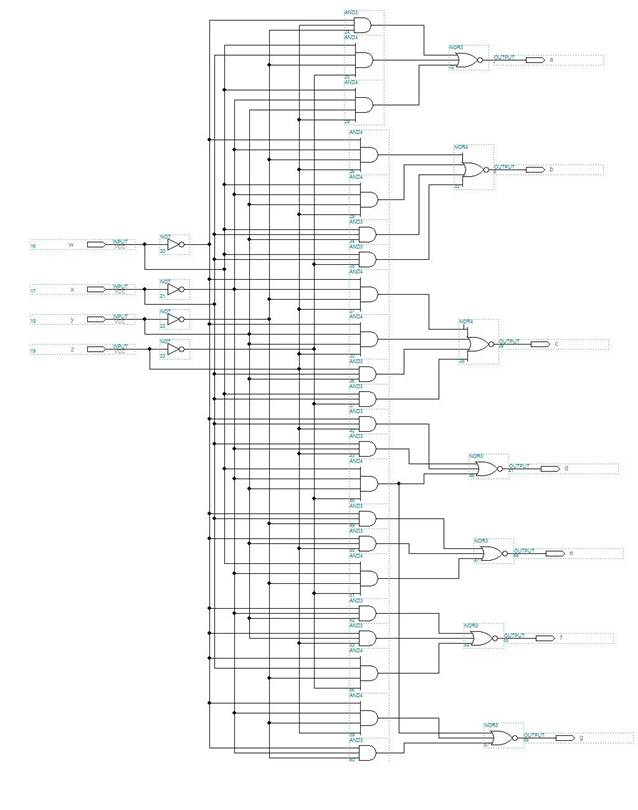

原理图:

GAL方程:

PLD16V8

BASIC GATES

2009.04.16

LQY USTC V0.1

W X Y Z NC NC NC NC NC GND

NC A B C D E F G NC VCC

/A=/W*/X*/Y*Z+/W*X*/Y*/Z+W*/X*Y*Z+W*X*/Y*Z/

/B=/W*/X*/Y*Z+/W*X*/Y*Z+/W*X*Y*/Z+W*/X*Y*Z+W*X*/Y*/Z+W*X*Y*/Z

/C=/W*/X*/Y*Z+/W*/X*Y*/Z+W*X*/Y*/Z+W*X*Y*/Z+W*X*Y*Z

/D=/W*/X*/Y*Z+/W*X*/Y*/Z+/W*X*Y*Z+W*/X*Y*/Z+W*X*Y*Z

/E=/W*/X*Y*Z+/W*X*/Y*/Z+/W*X*/Y*Z+/W*X*Y*Z+W*/X*/Y*Z

/F=/W*/X*Y*/Z+/W*/X*Y*Z+/W*X*Y*Z+W*X*/Y*Z

/G=/W*/X*/Y*Z+/W*X*Y*Z+W*X*/Y*/Z+/W*/X*/Y*/Z

DESCRIPTION

注释:实验中使用的是共阳极数码管,设计的时候还没有化简

VHDL代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY code16 IS

PORT(w,x,y,z: IN STD_LOGIC;

A,b,c,d,e,f,g:OUT STD_LOGIC

);

END code16;

ARCHITECTURE WORK OF code16 IS

BEGIN

A<=(NOT W AND NOT X AND NOT Y AND Z) OR (NOT W AND X AND NOT Y AND NOT Z) OR (W AND NOT X AND Y AND Z) OR (W AND X AND NOT Y AND NOT Z);

B<=(NOT W AND NOT X AND NOT Y AND Z) OR (NOT W AND X AND NOT Y AND Z) OR (NOT W AND X AND Y AND NOT Z) OR (W AND NOT X AND Y AND Z) OR (W AND X AND NOT Y AND NOT Z) OR (W AND X AND Y AND NOT Z);

C<=(NOT W AND NOT X AND NOT Y AND Z) OR (NOT W AND NOT X AND Y AND NOT Z) OR (W AND X AND NOT Y AND NOT Z) OR (W AND X AND Y AND NOT Z) OR (W AND X AND Y AND Z);

D<=(NOT W AND NOT X AND NOT Y AND Z) OR (NOT W AND X AND NOT Y AND NOT Z) OR (NOT W AND X AND Y AND Z) OR (W AND NOT X AND Y AND NOT Z) OR (W AND X AND Y AND Z);

E<=(NOT W AND NOT X AND Y AND Z) OR (NOT W AND X AND NOT Y AND NOT Z) OR (NOT W AND X AND NOT Y AND Z) OR (NOT W AND X AND Y AND Z) OR (W AND NOT X AND NOT Y AND Z);

F<=(NOT W AND NOT X AND Y AND NOT Z) OR (NOT W AND NOT X AND Y AND Z) OR (NOT W AND X AND Y AND Z) OR (W AND X AND NOT Y AND Z);

NOT G<=(NOT W AND NOT X AND NOT Y AND Z) OR (NOT W AND X AND Y AND Z) OR (W AND X AND NOT Y AND NOT Z) OR (NOT W AND NOT X AND NOT Y AND NOT Z);

END WORK;

实验三:海明校验电路

原理图:

做实验时,造错在总线上造错,导致读和写没有很好体现出来。

GAL方程:

PLD01V0

HAMMING

2009.04.16

LQY USTC V0.1

A B C D EA EB EC ED NC GND

NC S1 S2 S3 R1 R2 R3 R4 NC VCC

IA=A $ EA

IB=B $ EB

IC=C $ EC

ID=D $ ED

K1=A $ B $ D

K2=A $ C $ D

K3=B $ C $D

S1=A $ B $ D $ K1

S2=A $ C $ D $ K2

S3=B $ C $ D $ K3

E1=S1*S2*S3

E2= S1*S2*/S3

E3= S1*/S2*/S3

E4=/S1*S2*S3

R1=A $ E1

R2=B $ E2

R3=C $ E3

R4=D $ E4

DESCRIPTION

VHDL代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY hamm IS

PORT(i1,i2,i3,i4,e1,e2,e3,e4:IN STD_LOGIC;

r1,r2,r3,k1,k2,k3,k4:OUT STD_LOGIC);

END hamm;

ARCHITECTURE hamming OF hamm IS

SIGNAL s1,s2,s3,b1,b2,b3,b4,c1,c2,c3,c4,d1,d2,d3,d4:STD_LOGIC;

BEGIN

b1<=i1 XOR e1;

b2<=i2 XOR e2;

b3<=i3 XOR e3;

b4<=i4 XOR e4;

s1<=i4 XOR i2 XOR i1;

s2<=i4 XOR i3 XOR i1;

s3<=i4 XOR i3 XOR i2;

c1<=b4 XOR b2 XOR b1 XOR s1;

c2<=b4 XOR b3 XOR b1 XOR s2;

c3<=b4 XOR b3 XOR b2 XOR s3;

d1<=c1 AND c2 AND (NOT c3) AND (NOT c4);

d2<=c1 AND (NOT c2) AND (NOT c3) AND c4;

d3<=(NOT c1) AND c2 AND c3 AND c4;

d4<=c1 AND c2 AND c3 AND c4;

r1<=c1;

r2<=c2;

r3<=c3;

k1<=d1 XOR c1;

k2<=d2 XOR c2;

k3<=d3 XOR c3;

k4<=d4 XOR c4;

END hamming;

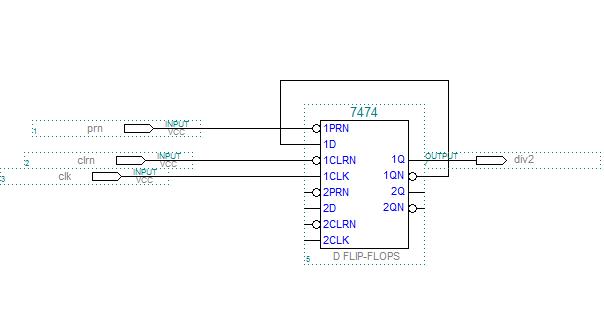

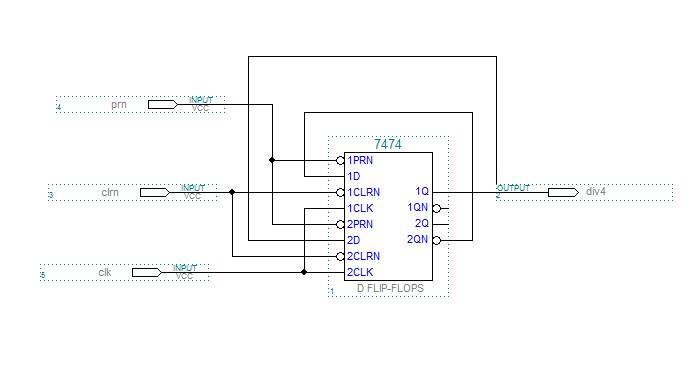

实验四:时序脉冲分频电路

原理图:

二分频电路

四分频电路

五分频电路

三周期电路

GAL方程:

VHDL代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY exp5tx IS

PORT(clk : IN STD_LOGIC;

CP1,CP2,CP3,CP4,CP5,CP6 : OUT STD_LOGIC;

Q3,Q4,Q4b,Q5,Q6,Q7,Q8 : BUFFER STD_LOGIC);

END exp5tx;

ARCHITECTURE DISTRIBUTER OF exp5tx IS

BEGIN

PROCESS(clk,Q3,Q5)

VARIABLE count_5 : STD_LOGIC_VECTOR(2 DOWNTO 0);

VARIABLE count_2 : STD_LOGIC;

VARIABLE count_4 : STD_LOGIC_VECTOR(1 DOWNTO 0);

VARIABLE count_3 : STD_LOGIC_VECTOR(1 DOWNTO 0);

BEGIN

IF(clk'EVENT AND clk='1')THEN

IF(count_5="000")THEN

count_5 = "001";Q3 <= '1';

ELSIF(count_5="001")THEN

count_5 := "010";Q3 <= '0';

ELSIF(count_5="010")THEN

count_5 := "011";Q3 <= '0';

ELSIF(count_5="011")THEN

count_5 := "100";Q3 <= '0';

ELSIF(count_5="100")THEN

count_5 := "000";Q3 <= '0';

END IF;

END IF;

IF(Q3'EVENT AND Q3='1')THEN

IF(count_2='0')THEN

count_2 := '1'; Q4 <= '1';Q4b <= '0';

ELSIF(count_2='1')THEN

count_2 := '0'; Q4 <= '0';Q4b <= '1';

END IF;

END IF;

IF(Q3'EVENT AND Q3='1')THEN

IF(count_4="00")THEN

count_4 := "01";Q5 <= '1';

ELSIF(count_4="01")THEN

count_4 := "10";Q5 <= '1';

ELSIF(count_4="10")THEN

count_4 := "11";Q5 <= '0';

ELSIF(count_4="11")THEN

count_4 := "00";Q5 <= '0';

END IF;

END IF;

IF(Q5'EVENT AND Q5='1')THEN

IF(count_3="00")THEN

count_3 := "01"; Q6 <= '1';Q7 <= '0';Q8 <= '0';

ELSIF(count_3="01")THEN

count_3 := "10"; Q6 <= '0';Q7 <= '1';Q8 <= '0';

ELSIF(count_3="10")THEN

count_3 := "00"; Q6 <= '0';Q7 <= '0';Q8 <= '1';

END IF;

END IF;

END PROCESS;

CP1 <= Q4b AND Q5 AND Q6;

CP2 <= Q4b AND NOT Q5 AND Q6;

CP3 <= Q4b AND Q5 AND Q7;

CP4 <= Q4b AND NOT Q5 AND Q7;

CP5 <= Q4b AND Q5 AND Q8;

CP6 <= Q4b AND NOT Q5 AND Q8;

END DISTRIBUTER;

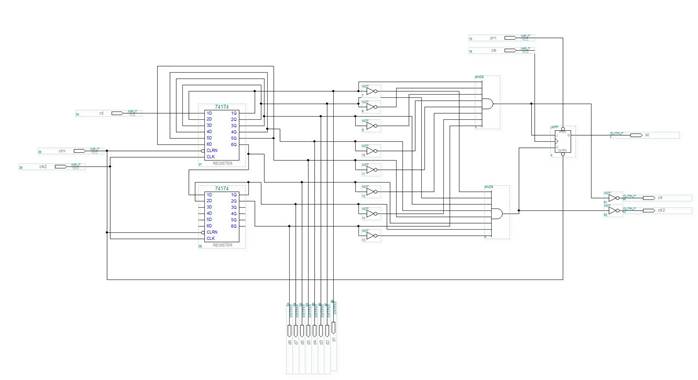

实验五:串并转换电路

原理图:

控制逻辑

十六进制计数器

GAL方程:

VHDL代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY sp IS

PORT(clk,rd: IN STD_LOGIC;

s7,s6,s5,s4,s3,s2,s1,s0:OUT STD_LOGIC

);

END sp;

ARCHITECTURE WORK OF sp IS

SIGNAL clr,cclk,c2,c16,d7,d6,d5,d4,d3,d2,d1,d0,st: STD_LOGIC;

BEGIN

PROCESS(clk)

VARIABLE count_4 : STD_LOGIC_VECTOR(1 DOWNTO 0);

BEGIN

IF(clk'EVENT AND clk='1')THEN

IF(count_4="00")THEN

count_4 := "01";c2 <= '1';

ELSIF(count_4="01")THEN

count_4 := "11";c2 <= '0';

ELSIF(count_4="11")THEN

count_4 := "10";c2 <= '0';

ELSIF(count_4="10")THEN

count_4 := "00";c2 <= '0';

END IF;

END IF;

END PROCESS;

PROCESS(c2,rd)

VARIABLE count_2 : STD_LOGIC;

BEGIN

IF(c2'EVENT AND c2='1')THEN

d0<=rd;

d1<=d0;

d2<=d1;

d3<=d2;

d4<=d3;

d5<=d4;

d6<=d5;

d7<=d6;

END IF;

END PROCESS;

PROCESS(clk,d7,d6,d5,d4,d3,d2,d1,d0)

BEGIN

IF(clk'EVENT AND clk='1')THEN

IF(d7='0' and d6='1' and d5='1' and d4='1' and d3='1' and d2='1' and d1='1' and d0='0')THEN

st <= '0';

ELSIF(d7='1' and d6='0' and d5='0' and d4='0' and d3='0' and d2='0' and d1='0' and d0='1')THEN

st <= '1';

END IF;

END IF;

cclk <= st AND clk;

IF(d7='0' and d6='1' and d5='1' and d4='1' and d3='1' and d2='1' and d1='1' and d0='0')THEN

clr<='1';

ELSIF(d7='1' and d6='0' and d5='0' and d4='0' and d3='0' and d2='0' and d1='0' and d0='1')THEN

clr<='1';

ELSE

clr<='0';

END IF;

END PROCESS;

PROCESS

VARIABLE count_4 : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

WAIT ON cclk UNTIL (cclk'EVENT AND cclk='1');

IF(count_4="0000")THEN

count_4 := "0001";c16 <= '0';

ELSIF(count_4="0001")THEN

count_4 := "0010";c16 <= '0';

ELSIF(count_4="0010")THEN

count_4 := "0011";c16 <= '0';

ELSIF(count_4="0011")THEN

count_4 := "0100";c16 <= '0';

ELSIF(count_4="0100")THEN

count_4 := "0101";c16 <= '0';

ELSIF(count_4="0101")THEN

count_4 := "0110";c16 <= '0';

ELSIF(count_4="0110")THEN

count_4 := "0111";c16 <= '0';

ELSIF(count_4="0111")THEN

count_4 := "1000";c16 <= '0';

ELSIF(count_4="1000")THEN

count_4 := "1001";c16 <= '0';

ELSIF(count_4="1001")THEN

count_4 := "1010";c16 <= '0';

ELSIF(count_4="1010")THEN

count_4 := "1011";c16 <= '0';

ELSIF(count_4="1011")THEN

count_4 := "1100";c16 <= '0';

ELSIF(count_4="1100")THEN

count_4 := "1101";c16 <= '0';

ELSIF(count_4="1101")THEN

count_4 := "1110";c16 <= '0';

ELSIF(count_4="1110")THEN

count_4 := "1111";c16 <= '0';

ELSIF(count_4="1111")THEN

count_4 := "0000";c16 <= '1';

END IF;

END PROCESS;

PROCESS(c16,st,clr)

BEGIN

IF(c16 ='0' OR st='0' OR clr='1')THEN

s0<='Z';

s1<='Z';

s2<='Z';

s3<='Z';

s4<='Z';

s5<='Z';

s6<='Z';

s7<='Z';

ELSE

s0<=d0;

s1<=d1;

s2<=d2;

s3<=d3;

s4<=d4;

s5<=d5;

s6<=d6;

s7<=d7;

END IF;

END PROCESS;

END WORK;

-

数字逻辑电路课程设计实验报告

数字逻辑电路课程设计报告数字逻辑电路课程设计多功能数字时钟班级信息安全1002姓名潘祥熙学号3100604048指导老师袁晓云时间…

-

数字逻辑电路实验报告

数字逻辑电路实验报告电子72班07051042冯天宇1数字逻辑电路实验报告计数器设计与应用学院电信学院班级电子72班姓名冯天宇学号…

-

数字逻辑电路实验报告模板

数字逻辑电路实验报告第次实验姓名学号级系班邮箱时间正文由下面八项内容评定每次实验报告成绩一实验目的本次实验预期要学习到的知识方法等…

-

数字逻辑电路实验报告

数字逻辑电路设计多功能数字钟学院计算机科学与通信工程专业姓名学号指导老师江苏大学计算机10数字逻辑电路设计报告多功能数字钟一设计任…

-

哈工大 数字逻辑电路与系统实验报告

HarbinInstituteofTechnology数字逻辑电路与系统课程名称院系班级姓名学号教师哈尔滨工业大学20xx年12月…

-

大连海事大学数字逻辑电路课程设计实验总结报告

数字逻辑电路课程设计实验总结报告题目一:用J-K触发器设计13进制加法计数器一、设计过程:参见设计实验报告(真值表,卡诺图)。二、…

-

东南大学 数字电路实验 第4章_时序逻辑电路

东南大学电工电子实验中心实验报告课程名称数字逻辑电路设计实践第4次实验实验名称基本时序逻辑电路院系信息科学与工程学院专业信息工程姓…

-

数字电路实验二--译码器实验报告深圳大学--郭治民

深圳大学实验报告实验课程名称数字电路与逻辑设计实验项目名称学院计算机与软件学院专业计算机科学与技术报告人同组人指导教师实验时间实验…

-

数字电路实验报告3

暨南大学本科实验报告专用纸课程名称数字逻辑电路实验成绩评定实验项目名称三态门特性研究和典型应用指导教师实验项目编号08060038…

-

数字电路与数字逻辑大型实验报告

数字电路与数字逻辑大型实验报告1一实验内容一QuartusII操作练习1用原理图输入法设计一个3线8线译码器二数字频率计设计三倒计…

-

数字电路实验心得体会

数字电路实验心得体会数字电路实验心得体会一数字电路实验心得在实验具体操作的过程中对理论知识半加器和全加器也有了更近一步的理解真正达…