电子设计自动化(EDA)_数字时钟程序模块(LED数码管显示)_实验报告

电子设计自动化(EDA)—数字时钟LED数码管显示

二、实验内容和实验目的

1.6个数码管动态扫描显示驱动

2.按键模式选择(时\分\秒)与闹钟(时\分)调整控制,

3.用硬件描述语言(或混合原理图)设计时、分、秒计数器模块、闹钟模块、按键控制状态机模块、动态扫描显示驱动模块、顶层模块。要求使用实验箱左下角的6个动态数码管(DS6 A~DS1A)显示时、分、秒;要求模式按键和调整按键信号都取自经过防抖处理后的按键跳线插孔。

实验目的: 1)学会看硬件原理图,2)掌握FPGA硬件开发的基本技能

3)培养EDA综合分析、综合设计的能力

三、实验步骤、实现方法(或设计思想)及实验结果

主要设备: 1)PC机,2)硬件实验箱,3)Quartus II软件开发平台。

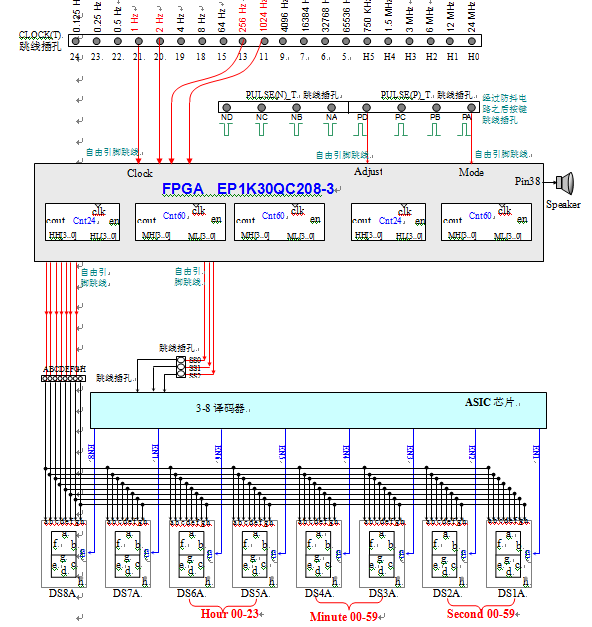

1.打开Quartus II ,连接实验箱上的相关硬件资源,如下图1所示。

2.建立新文件,选择文本类型或原理图类型。

3.编写程序。

4.编译

5.仿真,加载程序到芯片,观察硬件输出结果(数码管显示)

6.结果正确则完成。若结果不正确,则修改程序,再编译,直到正确。

模24计数器模块

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY count24 IS

PORT(clk,en:IN STD_LOGIC;

cout:OUT STD_LOGIC;

hh,hl:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END count24;

ARCHITECTURE arc OF count24 IS

SIGNAL a,b:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(clk,en)

BEGIN

hh<=a;

hl<=b;

IF(clk'EVENT AND clk='1') THEN

IF(en='1') THEN

IF(a="0010" AND b="0011") THEN

a<="0000";

b<="0000";

ELSE IF(b="1001") THEN

a<=a+'1';

b<="0000";

ELSE b<=b+'1';

END IF;

END IF;

IF(a="0010" AND b="0010") THEN

cout<='1';

ELSE cout<='0';

END IF;

END IF;

END IF;

END PROCESS;

END arc;

模60计数器模块

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY count60 IS

PORT(clk,en:IN STD_LOGIC;

cout:OUT STD_LOGIC;

hh,hl:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END count60;

ARCHITECTURE arc OF count60 IS

SIGNAL a,b:STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL sout:STD_LOGIC;

BEGIN

PROCESS(clk)

BEGIN

hh<=a;

hl<=b;

IF(clk'EVENT AND clk='1') THEN

IF(en='1') THEN

IF(a="0101" AND b="1001") THEN

a<="0000";

b<="0000";

ELSE IF(b="1001") THEN

a<=a+'1';

b<="0000";

ELSE b<=b+'1';

END IF;

END IF;

END IF;

END IF;

END PROCESS;

sout<='1' WHEN a="0101" AND b="1001"

ELSE '0';

cout<=sout AND en;

END arc;

4-7显示译码模块

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY segment4to7 IS

PORT(s:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

a,b,c,d,e,f,g:OUT STD_LOGIC);

END segment4to7;

ARCHITECTURE arc OF segment4to7 IS

SIGNAL y:STD_LOGIC_VECTOR(6 DOWNTO 0);

BEGIN

a<= y(6);

b<= y(5);

c<= y(4);

d<= y(3);

e<= y(2);

f<= y(1);

g<= y(0);

PROCESS(s)

BEGIN

CASE s IS

WHEN "0000"=>y<="1111110";

WHEN "0001"=>y<="0110000";

WHEN "0010"=>y<="1101101";

WHEN "0011"=>y<="1111001";

WHEN "0100"=>y<="0110011";

WHEN "0101"=>y<="1011011";

WHEN "0110"=>y<="1011111";

WHEN "0111"=>y<="1110000";

WHEN "1000"=>y<="1111111";

WHEN "1001"=>y<="1111011";

WHEN OTHERS=>y<="0000000";

END CASE;

END PROCESS;

END arc;

带闹钟控制模块

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY mode_adjust_with_alarm IS

PORT (adjust,mode,clk1hz: IN STD_LOGIC;

clkh,enh,clkm,enm,clks,enha: OUT STD_LOGIC;

clkh_a,clkm_a:OUT STD_LOGIC;

mode_ss: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END mode_adjust_with_alarm;

ARCHITECTURE arc OF mode_adjust_with_alarm IS

TYPE mystate IS (s0,s1,s2,s3,s4,s5);

SIGNAL c_state,next_state: mystate;

BEGIN

PROCESS (c_state)

BEGIN

CASE c_state IS

WHEN s0=> next_state <= s1; clkh<=clk1hz; clkm<=clk1hz; clks<=clk1hz;

enh<='0'; enm<='0'; enha<='0'; clkh_a<= '0'; clkm_a<= '0'; mode_ss <="000";

WHEN s1=> next_state <= s2; clkh<=adjust; clkm<= '0'; clks<='0';

enh<='1'; enm<='0';enha<='0'; clkh_a<= '0';clkm_a<= '0'; mode_ss <="001";

WHEN s2=> next_state <= s3; clkh<= '0'; clkm<=adjust; clks <= '0'; enh<='0';enm<='1';enha<='0'; clkh_a<= '0'; clkm_a<= '0'; mode_ss <="010";

WHEN s3=> next_state <= s4; clkh<= '0'; clkm<= '0'; clks<=adjust;

enh<='0'; enm<='0';enha<='0'; clkh_a<= '0'; clkm_a<= '0'; mode_ss <="011";

WHEN s4=> next_state <= s5; clkh<= clk1hz; clkm<= clk1hz; clks<=clk1hz; enh<='0';enm<='0';enha<='1'; clkh_a<=adjust; clkm_a<= '0'; mode_ss <="100";

WHEN s5=> next_state <= s0; clkh<= clk1hz; clkm<= clk1hz; clks<=clk1hz;

enh<='0'; enm<='0'; enha<='0'; clkh_a<= '0'; clkm_a<=adjust; mode_ss <="101";

END CASE;

END PROCESS;

PROCESS (mode)

BEGIN

IF (mode'EVENT AND mode='1') THEN

c_state<=next_state ;

END IF;

END PROCESS;

END arc;

扫描模块

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY scan IS

PORT(clk256hz:IN STD_LOGIC;

ss:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END scan;

ARCHITECTURE arc OF scan IS

TYPE mystate IS (s0, s1,s2,s3,s4,s5);

SIGNAL c_state,next_state: mystate;

BEGIN

PROCESS ( c_state )

BEGIN

CASE c_state IS

WHEN s0=> next_state <=s1; ss<="010";

WHEN s1=> next_state <=s2; ss<="011";

WHEN s2=> next_state <=s3; ss<="100";

WHEN s3=> next_state <=s4; ss<="101";

WHEN s4=> next_state <=s5; ss<="110";

WHEN s5=> next_state <=s0; ss<="111";

END CASE;

END PROCESS;

PROCESS (clk256hz)

BEGIN

IF (clk256hz'EVENT AND clk256hz='1') THEN

c_state<=next_state ;

END IF;

END PROCESS;

END arc;

复用模块

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY mux IS

PORT(hh,hl,mh,ml,sh,sl,hha,hla,mha,mla:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

ss,mode_ss:IN STD_LOGIC_VECTOR(2 DOWNTO 0);

y:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

alarm:OUT STD_LOGIC);

END mux;

ARCHITECTURE arc OF mux IS

SIGNAL a,hhtmp,hltmp,mhtmp,mltmp,shtmp,sltmp:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(mode_ss)

BEGIN

CASE mode_ss IS

WHEN "000"=>hhtmp<=hh; hltmp<=hl; mhtmp<=mh; mltmp<=ml; shtmp<=sh; sltmp<=sl;

WHEN "001"=>hhtmp<=hh; hltmp<=hl; mhtmp<=mh; mltmp<=ml; shtmp<=sh; sltmp<=sl;

WHEN "010"=>hhtmp<=hh; hltmp<=hl; mhtmp<=mh; mltmp<=ml; shtmp<=sh; sltmp<=sl;

WHEN "011"=>hhtmp<=hh; hltmp<=hl; mhtmp<=mh; mltmp<=ml; shtmp<=sh; sltmp<=sl;

WHEN "100"=> hhtmp<=hha; hltmp<=hla; mhtmp<=mha; mltmp<=mla; shtmp<=sh; sltmp<=sl;

WHEN "101"=> hhtmp<=hha; hltmp<=hla; mhtmp<=mha; mltmp<=mla; shtmp<=sh; sltmp<=sl;

WHEN OTHERS=>

hhtmp<="0000";hltmp<="0000";mhtmp<="0000";mltmp<="0000";shtmp<="0000";sltmp<="0000";

END CASE;

END PROCESS;

PROCESS(ss)

BEGIN

CASE ss IS

WHEN "010"=> a <=hhtmp;

WHEN "011"=> a <=hltmp;

WHEN "100"=> a <=mhtmp;

WHEN "101"=> a <=mltmp;

WHEN "110"=> a <=shtmp;

WHEN "111"=> a <=sltmp;

WHEN OTHERS => a <="0000";

END CASE;

y<=a;

END PROCESS;

alarm<='1' WHEN ((hh=hha)AND(hl=hla)AND(mh=mha)AND(ml=mla)) ELSE '0';

END arc;

闪烁模块

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY blink_control IS

PORT(ss,mode_ss:IN STD_LOGIC_VECTOR(2 DOWNTO 0);

blink_en:OUT STD_LOGIC);

END blink_control;

ARCHITECTURE arc OF blink_control IS

BEGIN

PROCESS (ss,mode_ss)

BEGIN

IF(ss="010" AND mode_ss="001") THEN blink_en<='1';

ELSIF(ss="011" AND mode_ss="001") THEN blink_en<='1';

ELSIF(ss="100" AND mode_ss="010") THEN blink_en<='1';

ELSIF(ss="101" AND mode_ss="010") THEN blink_en<='1';

ELSIF(ss="110" AND mode_ss="011") THEN blink_en<='1';

ELSIF(ss="111" AND mode_ss="011") THEN blink_en<='1';

ELSIF(ss="010" AND mode_ss="100") THEN blink_en<='1';

ELSIF(ss="011" AND mode_ss="100") THEN blink_en<='1';

ELSIF(ss="100" AND mode_ss="101") THEN blink_en<='1';

ELSIF(ss="101" AND mode_ss="101") THEN blink_en<='1';

ELSE blink_en<='0';

END IF;

END PROCESS;

END arc;

Top文件

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY design3 IS

PORT (mode,adjust,clk1hz,clk2hz,clk256hz,clk1khz:IN STD_LOGIC;

alarm,a,b,c,d,e,f,g:OUT STD_LOGIC;

ss:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END design3;

ARCHITECTURE arc OF design3 IS

COMPONENT mode_adjust_with_alarm PORT (

adjust,mode,clk1hz: IN STD_LOGIC;

clkh,enh,clkm,enm,clks,enha: OUT STD_LOGIC;

clkh_a,clkm_a:OUT STD_LOGIC;

mode_ss: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END COMPONENT;

COMPONENT scan PORT (

clk256hz:IN STD_LOGIC;

ss:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END COMPONENT;

COMPONENT segment4to7 PORT (

s: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

a,b,c,d,e,f,g: OUT STD_LOGIC);

END COMPONENT;

COMPONENT mux PORT(hh,hl,mh,ml,sh,sl,hha,hla,mha,mla:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

ss,mode_ss:IN STD_LOGIC_VECTOR(2 DOWNTO 0);

y:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

alarm:OUT STD_LOGIC);

END COMPONENT;

COMPONENT blink_control PORT(

ss,mode_ss:IN STD_LOGIC_VECTOR(2 DOWNTO 0);

blink_en:OUT STD_LOGIC);

END COMPONENT;

COMPONENT count24 PORT (

clk,en:IN STD_LOGIC;

cout:OUT STD_LOGIC;

hh,hl:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END COMPONENT;

COMPONENT count60 PORT (

clk ,en:IN STD_LOGIC;

cout:OUT STD_LOGIC;

hh,hl:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END COMPONENT;

SIGNAL clkh,enh,clkm,enm,clks,clkh_a,clkm_a,coutm,couts,coutm_en,couts_en,cout,vcc,coutma_en,coutma,alarm1,blink_en,blink_tmp,enha: STD_LOGIC;

SIGNAL mode_ss,ss1:STD_LOGIC_VECTOR(2 DOWNTO 0);

SIGNAL hh,hl,mh,ml,sh,sl,hha,hla,mha,mla,y,i:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

vcc<='1';

coutm_en <= enh OR coutm;

couts_en <= enm OR couts;

coutma_en<= enha OR coutma;

blink_tmp<=blink_en and clk2hz;

i(3)<=y(3) OR blink_tmp;

i(2)<=y(2) OR blink_tmp;

i(1)<=y(1) OR blink_tmp;

i(0)<=y(0) OR blink_tmp;

ss<=ss1;

alarm<=alarm1 AND clk1khz;

u1:mode_adjust_with_alarm

PORT MAP( adjust,mode,clk1hz,clkh,enh,clkm,enm,clks,enha,clkh_a,clkm_a,mode_ss);

u2:count24 PORT MAP(clkh,coutm_en,cout,hh,hl);

u3:count60 PORT MAP(clkm,couts_en,coutm,mh,ml);

u4:count60 PORT MAP(clks,vcc,couts,sh,sl);

u5:count24 PORT MAP(clkh_a,coutma_en,cout,hha,hla);

u6:count60 PORT MAP(clkm_a,vcc,coutma,mha,mla);

u7:mux PORT MAP(hh,hl,mh,ml,sh,sl,hha,hla,mha,mla,ss1,mode_ss,y,alarm1);

u8:scan PORT MAP(clk256hz,ss1);

u9:blink_control PORT MAP(ss1,mode_ss,blink_en);

u10:segment4to7 PORT MAP(i,a,b,c,d,e,f,g);

END arc;

实验结果:

数字钟包括正常的时分秒计时,实验箱左下角的6个动态数码管(DS6 A~DS1A)显示时、分、秒。adjust 递增调整时分秒,mode按键循环调整。闹钟定闹功能,在调整闹钟的“时”“分”的时候,数码管应显示闹钟的时间,此时正常时间继续计时,不会因为调整闹钟而使数字钟暂停。到了定闹时间,蜂鸣器发声。

硬件实验三对应的硬件资源连接

四、总结

实验中最容易出现的错误

1.并口线、下载线连接不紧,下载程序时出现错误提示,

2.选错芯片,出现错误提示。

3.注意控制计数器en 状态。

-

单片机c语言版数码管动态显示实验报告

数码管动态显示实验一实验要求1在Proteus软件中画好51单片机最小核心电路包括复位电路和晶振电路2在电路中增加四个7段数码管共…

-

数码管动态显示实验报告

实验四数码管动态显示实验一一实验要求1在Proteus软件中画好51单片机最小核心电路包括复位电路和晶振电路2在电路中增加四个7段…

-

数码管显示实验报告

HUNANUNIVERSITY课程实验报告实验名称学生姓名学生学号专业班级指导老师数码管显示实验20xx1217实验三数码管显示实…

-

实验报告 实验七 八段数码管显示实验

实验七八段数码管显示实验1实验目的1了解数码管动态显示的原理2了解用总线方式控制数码管显示2实验要求利用实验仪提供的显示电路动态显…

-

实验四 七段数码管显示实验报告

实验四七段数码管显示实验一实验目的掌握数码管显示数字的原理二实验内容1静态显示数码管为共阴极通过BCD码译码驱动器CD4511驱动…

-

【精】数字时钟实验报告

一指标要求1显示时分秒采用24小时制2具有校时功能可以对小时和分单独校时对分校时的时候停止分向小时进位校时时钟源可以手动输入或借用…

-

VHDL数字时钟实验报告

VHDL数字时钟设计一实验目的进一步练习VHDL语言设计工程的建立与仿真的步骤和方法熟悉VHDL语言基本设计实体的编写方法同时在已…

-

EDA数字时钟实验报告

EDA实验报告实验名称EDA多功能数字时钟设计学院电气学院姓名班指导老师EDA多功能数字时钟设计摘要本实验中我们运用EDA课程中所…

-

EDA技术数字时钟实验报告

JIUJIANGUNIVERSITYEDA技术实验报告实验目的实验名称院系班级学号实验室专业姓名日期数字时钟电子工程学院B1111…

-

eda数字钟实验报告

实验四数字钟设计一实验目的1进一步学习更复杂的EDA熟练项目设计更的掌握VHDL语言设计2学习动态数码管的VHDL编程3更加熟练计…

-

单片机c语言版数码管动态显示实验报告

数码管动态显示实验一实验要求1在Proteus软件中画好51单片机最小核心电路包括复位电路和晶振电路2在电路中增加四个7段数码管共…