开题报告数字频率计

杭州电子科技大学

毕业设计(论文)开题报告

一、综述本课题国内外研究动态,说明选题的依据和意义

(一)课题的意义

在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此,频率的测量就显得更为重要。近年来,在现代电子系统设计领域中,电子设计自动化已成为重要的设计手段。简单的搭建电路已经不适应大规模电路设计要求。EDA的可编写程序设计硬件电路设计,可重复下载的优势非常明显。这样做既可节省时间又能避免不必要的资源浪费。数字频率计的设计,其功能是实现信号的频率、周期、占空比以及脉宽等指标的测量,在电子测量、航海、探测、军事等众多领域的应用范围广泛。

数字频率计是数字电路中的一个典型应用,实际的硬件设计用到的器件较多,连线比较复杂,而且会产生比较大的延时,造成测量误差、可靠性差。而采用FPGA现场可编程门阵列为控制核心,通过硬件描述语言VHDL编程,在Quartus II仿真平台上编译、仿真、调试 ,并下载到FPGA芯片上,通过严格的测试后,能够较准确地测量方波、正弦波、三角波、矩齿波等各种常用的信号的频率,而且还能对其他多种物理量进行测量,并且将使整个系统大大简化,提高了系统的整体性能和可靠性。

本课题采用的是等精度数字频率计,在一片FPGA开发板里实现了数字频率计的绝大部分功能,它的集成度远远超过了以往的数字频率计。又由于数字频率计最初的实现形式是用硬件描述语言写成的程序,具有通用性和可重用性。 所以在外在的条件(如基准频率的提高,基准频率精度的提高)的允许下,只需对源程序作很小的改动,就可以使数字频率计的精度提高几个数量级。同时对于频率精度要求不高的场合,可以修改源程序,使之可以用较小的器件实现,从而降低系统的整体造价。

(二)国内外现状及发展趋势

我国在这个领域的发展是极其迅速,现在的技术实际已是多年来见证。我国现阶段电子产品的市场特点,电子数字化发展很快,数字频率计已经应用于高科技等产品上面,可以不夸张的说没有不包含有频率计的电子产品。我国的CD、VCD、DVD和数字音响广播等新技术已经大量进入市场,而在今天这些行业中都必须用到频率计。到今天频率计已开始并正向智能、精细的方向发展。

数字电路制造工业的进步,使得系统设计人员能在更小的空间实现更多的功能,从而提高系统可靠性和速度。现如今,数字频率计已经不仅仅是测量信号频率的装置了,用它还可以测量方波脉冲的脉宽。在人们的生活中频率计也发挥着越来越重要的作用,比如用数字频率计来监控生产过程,这样可以及时发现系统运行中的异常情况,以便给人们争取时间处理。

除此之外,它还可以应用于工业控制等其它领域。在传统的电子测量仪器中,示波器在进行频率测量是频率较低,误差较大。频率仪可以准确的测量频率并显示被测信号的频谱,但测量速度较慢,无法实时的跟踪捕捉到被测信号的频率变化。正是由于频率计能够快速准确的捕捉到被测信号频率的变化,因此频率计拥有非常广泛的引用范围。

二、研究的基本内容,拟解决的主要问题:

研究的基本内容:

数字频率计是数字电路中的一个典型应用,实际的硬件设计用到的器件较多,连线比较复杂,而且会产生较大的延时,造成测量误差、可靠性差。随着可编程逻辑器件(CPLD)的广泛应用,以EDA工具为开发平台,利用VHDL工业标准硬件描述语言,采用自顶向下 (Top to Down)和基于库(Library-based)的设计,设计者不但可以不必了解硬件结构设计,而且将使系统大大简化,提高整体的性能和可靠性。

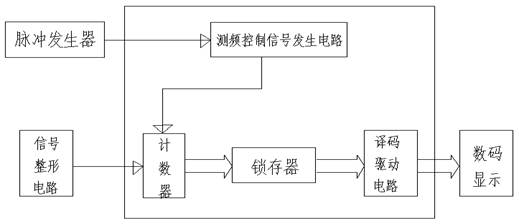

数字频率计的原理框图如图1所示。主要由5个模块组成,分别是:脉冲发生器电路、测频控制信号发生器电路、计数模块电路、锁存器、译码驱动电路。

图1 数字频率计的原理框图

数字式频率计的测量原理有两类:一是直接测频法,即在一定闸门时间内测量被测信号的脉冲个数;二是间接测频法即测周期法,如周期测频法。直接测频法适用于高频信号的频率测量,通常采用计数器、数据锁存器及控制电路实现,并通过改变计数器阀门的时间长短在达到不同的测量精度;间接测频法适用于低频信号的频率测量,本设计中使用的就是直接测频法,即用计数器在计算1s内输入信号周期的个数。

根据频率的定义和频率测量的基本原理,通过VHDL语言编程设计一款8位能以十六进制方式显示的频率计,再添加一块模板,把频率计改为8位十进制方式显示的频率计,此电路的计数器必须是8个4位的十进制计数器,并用EDA软件仿真。

可能遇到的问题:

(一)在接受信号脉冲时,有效脉冲不能使电路处于初始化;

(二)在低频率时候,脉冲会有衰减,使得测量不能正常记录;

(三)为了保证测试精度,一般对于低频信号采用测周期法;对于高频信号采用测频法,测试时很不方便;

(四)单片机程序和FPGA语言程序无法完美结合。

解决方法:

(一)检查电路,并且及时调整输入时钟;

(二)可以采用直接测量频率的方法;

(三)采用等精度频率测量方法具有测量精度,测量精度保持恒定,不随所测信号的变化而变化;并且结合现场可编程门阵列FPGA具有集成度高、高速和高可靠性的特点,使频率的测频范围可达到0.1Hz~100MHz,测频全域相对误差恒为1/1000000。

(四)通过继续学习FPGA语言,使之能够与其他的程序达到完美结合。

三、研究步骤、方法及措施:

(一)研究方法:

根据频率定义,测量1 s内被测信号经过的周期数即为该信号的频率。因此,本设计应主要解决三个问题:产生一个标准的时钟信号作为闸门信号;在闸门信号有效时间范围内对输入的信号进行计数;对所得的数据进行处理,并将其显示。

运用自顶向下的设计思想, 编程时分别对控制、计数、锁存、译码等电路模块进行VHDL文本描述 ,使每个电路模块以及器件都以文本的形式出现 ,然后通过编译、波形分析、仿真、调试来完善每个器件的功能。单个器件制作完成后 , 然后将它们生成库文件 ,并产生相应的符号 ,最后用语言将各个已生成库文件的器件的各个端口连接在一起 ,从而形成了系统主电路的软件结构。在上述工作的基础上 ,再进行波形分析、仿真调试便完成整个软件设计。

图2传统测频原理图

图3 系统的结构框图

上图3是通过EDA技术,利用VHDL语言,组成的一个系统结构框图,它包括四个模块:计数模块,显示模块,基准时间产生模块,控制模块。此四大模块按照相互间的信号连接关系组合起来,各模块间的流程由VHDL语言并发处理,需说明的是,由于FPGA只能实现数字电路,因此输入信号的整形电路需通过外加实现。这样设计出一款8位既能用十六进制数计数,也能用十进制数计数的频率计,再在Quartus II软件平台上进行仿真。

通过FPGA技术设计的频率计,能够将大量的逻辑功能集成于一个单个器件中,根据不同的需要所提供的门数可以从几百门到上百万门,从根本上解决了单片机的先天性限制问题。不但集成度远远超过了以往的数字频率计,而且在基准频率及精度等外部条件的允许下,根据不同场合的精度要求,对硬件描述语言进行一定的改动,使系统在精度提高的同时,用较少的器件来实现系统的功能,从而降低系统的整体造价。

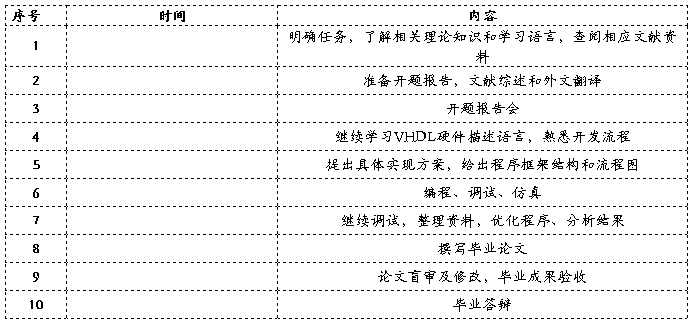

(二)步骤、措施:

当系统正常工作时,脉冲发生器提供的1Hz 的输入信号,经过测频控制信号发生器进行信号的变换,产生计数信号,被测信号通过信号整形电路产生同频率的矩形波,送入计数模块,计数模块对输入的矩形波进行计数,将计数结果送入锁存器中,保证系统可以稳定显示数据,显示译码驱动电路将二进制表示的计数结果转换成相应的能够在七段数码显示管上可以显示的十进制结果。在数码显示管上可以看到计数结果。

四、研究工作进度

五、主要参考文献

[1] 潘松,黄继业. EDA技术实用教程 [M]. 北京:科学出版社,2002.

[2] 潘松,王国栋. VHDL实用教程 [M]. 成都,成都电子科技大学出版社,2001 .

[3] 林晓焕,林刚. 基于VHDL语言的数字频率计设计[J], 西安工程科技学院学报, Vol.19, No.3, 2005, pp.321-324.

[4] 宋万杰,罗丰,吴顺君.CPLD技术极其应用.西安电子科技大学出版社.

[5] 魏忠,蔡勇,雷红卫.嵌入式开发详解.电子工业出版社

[6] 章坚武,李杰,姚英彪,骆懿.嵌入式系统设计与开发.西安电子科技大学出版社

[7] 潘松,陈龙,黄继业. 实用数字电子技术基础[M].北京,电子工业出版社,2011.

六、指导教师审核意见:

指导教师签字:

年 月 日

七、系(教研室)评议意见:

系(教研室)主任签字:

年 月 日

八、开题小组评审意见:

开题小组负责人签字:

年 月 日

九、学院领导审核意见:

1.通过; 2.完善后通过; 3. 未通过

学院领导签字:

年 月 日

第二篇:数字频率计的设计

毕业论文(设计)材料

题 目: 数字频率计的设计

学生姓名: 骆 曼 学生学号: 0908030223 系 别: 电气信息工程学院 专 业: 电子信息工程 届 别: 2013 指导教师: 张 大 雷

一、毕业论文(设计)任务书

二、毕业论文(设计)开题报告

三、毕业论文(设计)评审表

-

数字频率计开题报告

武汉大学珞珈学院本科生毕业论文设计开题报告毕业论文设计题目数字频率计系统设计系电子信息科学系学号20xx05060姓名一论文选题的…

-

开题报告数字频率计

杭州电子科技大学毕业设计论文开题报告题目学院专业姓名班级学号指导教师数字频率计的设计与实现通信工程学院通信工程孔冬滨120xx41…

- 数字频率计毕业设计开题报告

-

数字频率计开题报告

本科学生毕业设计论文开题报告系分院课题名称数字频率计的设计专业电子信息工程班级电信学生姓名指导教师李宇春日期20xx年12月23日…

-

数字频率计开题报告

本科生毕业设计论文开题报告院系信息工程学院专业电子信息班级D0842姓名赵培指导教师李悦研究方向单片机技术题目基于单片机的数字频率…

-

基于单片机的数字频率计的设计开题报告

题目:基于单片机的数字频率计的设计1.结合课题任务情况,查阅文献资料,撰写1500~20xx字左右的文献综述。单片机又称单片微控制…

- 基于单片机的频率计设计开题报告

-

无线遥控数字电子钟-开题报告

毕业论文设计开题报告题目无线遥控数字电子钟学生姓名韩二虎学号051641055所在院系机械工程学院专业班级测控052班指导教师杨帆…

-

数字频率计开题报告

武汉大学珞珈学院本科生毕业论文设计开题报告毕业论文设计题目数字频率计系统设计系电子信息科学系学号20xx05060姓名一论文选题的…

- 数字频率计毕业设计开题报告