基于FPGA数字频率计设计开题报告

毕业设计(论文)开题报告

基于FPGA数字频率计设计

系 部:

专 业:

学生姓名:

指导教师:

开题时间: 20## 年 3 月 日

第二篇:基于FPGA的全同步数字频率计的设计

湖南大学

硕士学位论文

基于FPGA的全同步数字频率计的设计

姓名:包本刚

申请学位级别:硕士

专业:电路与系统

指导教师:何怡刚

20071020

硕士学伊论文

摘要

频率是电子技术领域内的一个基本参数,同时也是一个非常重要的参数。稳定的时钟在高性能电子系统中有着举足轻重的作用,直接决定系统性能的优劣。随着电子技术的发展,测频系统使用时钟的提高潮9频技术有了相当大的发展,但不管是何种测频方法,±1个计数误差始终是限制测频精度进一步提高的一个重要因素。

本设计阐述了各种数字测频方法的优缺点。通过分析±1个计数误差的来源得出了一种新的测频方法:检测彼测信号,时基信号的相位,当相位同步时开始计数,相位再次同步时停止计数,通过相位同步来消除计数误差,然后再通过运算得到实际频率的大小。根据M/T法的测频原理,已经出现了等精度的测频方法,但是还存在±l的计数误差。因此,本文根据等精度测频原理中闸门时间只与被测信号同步,而不与标准信号同步的缺点,通过分析已有等精度测频方法所存在±1个计数误差的来源,采用了全同步的测频原理在FPGA器件上实现了全同步数字频率计。根据全同步数字频率计的测频原理方框图,采用VHDL语言,成功的编写出了设计程序,并在MAX+PLUSII软件环境中,对编写的VHDL程序进行了仿真,得到了很好的效果。最后,又讨论了全同步频率计的硬件设计并给出了电路原理图和PCB图。对构成全同步数字频率计的每一个模块,给出了较详细的设计方法和完整的程序设计以及仿真结果。

关键词:EDA、FPGA、全同步、数字频率计、VHDL语言、MAX+PLUSlI

基于FPGA的全同步数字频率计的设计

Abastract

Frequencyisabasicparameterofelectronicsfield,meanwhile,it’saveryimportantparameter.Stableclockisveryimportantinhighperformanceelectronicssystem,determiningthesyetemperformancedirectly.Withthedevelopmentoftechnologyofelectronics,thefrequencymeasurementsystemusinghigherclock,thefrequencymeasurementtechnologyhasverynicedevelopmentIndespiteofusingallotheradvancedfrequencymeasurementmethods,thepositiveandnegative1wasaerrorsveryimportantfactorthatstopfrequencymeasurementprecisionimprovingallthrough.

ThedesignexpoundtheadvantageanddisadvantageofmostdigitalfrequencymeasurementmethodsThroughanalyzingtheoriginofthepositiveandnegativeIelTors,gotanewfrequencymeasurementmethods:checkingthe

phase,ifthephaseissynchronous,thenthemeasuredcountersandstartstandardsignal’s

counting,whenthesignal’sphaseissynchronousagain,thecounterstoppingworking,byphasein-phasetoeliminatecountingerrors,thengettingtherealfrequencythroughcalculating.Bythisway’sguide,thedesign

successfullycompletedwithusingofcompletedigitalcymometerwasHighSpeedIntegratedCircuitHardVHDL(Very

DesignLanguage)hardwaredescriptionlanguageandsimulateditright.AccordingtoallofSynchronousDigitalBlockdiagramofthefrequencymeasurementusingVHDL,thesuccessfulpreparationofthedesignprocess,andinMAX+PLUSIIsoftwareenvironment,thepreparationofproceduresforVHDLsimulation,obtainedverygoodresults.Lastly,thefrequencysynchronizationofthewholediscussionofthehardwaredesignandgivesthecircuitschematicsandPCBplans.Allof

frequencyofeachmodule,is

designandsimulationresults.aasynchronousdigitalmoredetaileddesignandintegrityoftheprocess

Keyword:EDA、FPGA、CompleteIn-phase、DigitalCymometer、VHDL、MAXPLUSIIⅡ

湖南大学

学位论文原创性声明

本人郑重声明:所呈交的论文是本人在导师的指导下独立进行研究所取得的研究成果。除了文c扣特别加以标注引用的内容外,本论文不包含任何其他个人或集体己经发表或撰写的成果作品。对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式标明。本人完全意识到本声明的法律后果由本人承担。’

作者签名:宅砀剐日期:》_尹年‘1月上7日

学位论文版权使用授权书

本学位论文作者完全了解学校有关保留、使用学位论文的规定,同意学校保留并向国家有关部门或机构送交论文的复印件和电子版,允许论文被查阅和借阅。本人授权湖南大学可以将本学位论文的全部或部分内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存和汇编本学位论文。本学位论文属于

1、保密口,在

2、不保密团。

(请在以上相应方框内打“√”)年解密后适用本授权书。

作者签名:

导师签名:日期:弘刁年日期:肼f(月1,予日}}11月q日

硕I一学位论史

第一章

1.1课题背景绪论

随着数字电路应用越来越广泛,传统的通用数字集成电路芯片已经很难满足系统功能的要求,而且随着系统复杂程度的不断增加,所需通用集成电路的数量呈爆炸性增长,使得电路板的体积迅速膨胀,系统可靠性难以保证。此外,现代电子产品的生命周期都很短,一个电路可能要在很短的时间内作改进以满足新的功能要求,对于通用集成电路来说则意味着重新设计和重新布线。而可编程逻辑器件克服了上述缺点,它把通用集成电路通过编程集成到一块尺寸很小的硅片上,成倍缩小了电路的体积,同时由于走线短,减少了干扰,提高了系统的可靠性,又由于VHDL语言和Verilog语占易于掌握与使用,设计相当灵活,极大地缩短了产品的丌发周期。本设计在FPGA技术越来越成熟,应用越来越广泛的情况下,使用成熟的FPGA技术来实现目自管还不是很成熟的全同步数字频率计。此设计具有重要的研究价值。1.2频率计概述

频率是电子技术领域永恒的话题,电子技术领域离不丌频率,一旦离开频率电子技术的发展是不可想象的,就像现在的人离不开电一样。为了得到性能更好的电子系统,科研人员在不断地研究着频率,CPU就是用频率的高低来评价其性能好坏,速度的高低,可见频率在电子系统中是多么重要。如何/j。能知道频率的数值呢?当然是用频率计来测量。为了准确的测出频率的多少,人们研究出了很多测频率的方法。根据测频工作原理可将频率测量方法分成以下几类:

一、是利用电路的某种频率响应特性束测量频率,谐振测频法和电桥测频法是这类测量方法的典型代表:前者常用于低频段的测量,后者主要用于高频或微波频段的测量。谐振法的优点是体积小、重要轻、不要求电源等,目d口仍获得广泛应用。

二、是利用标准频率与被测频率进行比较来测量频率,采用比较法测量频率,其准确度取决于标准频率的准确度。拍频法、示波器法以及差频法等均属此类方法。拍频法和示波器法主要用于低频段的测量,差频法则用于高频段的频率测量,它的显著优点是测试灵敏度高…。

以上两种方法适合于模拟电路中实现,但是模拟电路没有数字电路稳定,因此数字电路出现后,马上就出现了数字频率计。目前广泛使用的计数测频法则适合于数字电路实现。该方法是根据频率的定义,记下单位时问内周期信号的重复次数,

基于FPGA的哞:旧步数’≯频率计的i51计

因此又称为电子计数器测频法。

常用数字频率测量方法有M法,T法和M/T法。M法是在给定的闸门时间内,测量被测信号的脉冲个数再进行换算得出被测信号的频率,其测量精度取决于闸门时问的准确度和被测信号频率。当被测信号频率较低时将产生较大误差,除非闸门时『日J取得很大。T法是通过测量被测信号的周期,然后换算得出被测信号韵频率。其测量精度取决于被测信号的周期和计时精度,测信号频率较高时,对计时精度的要求就很高。M/T法具有以上2种方法的优点,当他通过测量被测信号数个周期的计数次数,然后换算得出被测信号的频率,可兼顾低频与高频信号,提高了测量精度。但是,M法,T法和M/T法都存在±I计数误差问题。M法在规定闸门时问内存在±1个被测信号的脉冲计数误差,T法或M/T法也存在±1个字的计时误差。这个问题成为限制测量精度提高的一个重要原因。本设计在研究总结上述方法的基础上,得出了一种新的频率测量方法,该方法利用相位全同步方法消除限制测量精度提高的±1个数字误差问题,从而使频率测量的精度和性能大为改善“1。

然而一种新的方法的实际应用比提出来更难,要考虑各种可能的问题,首先就是由于采用的新的设计方法使得电路的复杂程度成倍增加,因此如果还采用传统数字电路来实现则将使PCB板面积变得异常庞大与复杂。信号走线长,导致系统误差增大,难以提高系统的工作频率,此外,PCB板的集成度不高还将导致高频信号容易受到外界的干扰,反而可能降低测频精度。由于可编程逻辑器件能很好地克服了以上缺点,大大提高系统时钟,因此本设计将介绍由现场可编程逻辑器件(FPGA)来实现全同步数字频率计,本设计除了相位检测电路不在可编程电路之中,其余的电路都集成在可编程逻辑器件中。

本设计消除了±l误差,但由于相位检测电路不可避免有误差,系统误差不可避免,因此,全同步数字频率计的主要问题是如何减小相位检测电路的误差以及提高标准时基晶振的稳定性。本设计使用著名的ALTERA公司的软件平台姒x+PLUSII并采用VHDL语言束设计实现。

1.3频率计发展现状

由于社会发展和科技发展的需要,信息传输和处理的要求的提高,对频率的测量精度也提出了更高的要求,需要更高准确度的时频基准和更精密的测量技术。而频率测量所能达到的精度,主要取决于作为标准频率源的精度以及所使用的测量设备和测量方法。目Ij{『,国内外使用的测频的方法有很多,有直接测频法、内插法、游标法、时间一电压变化法、多周期同步法、频率倍增法、频差倍增法以及相位比2

顾I学位论文

较法等等。直接测频的方法较简单,但精度不高。内插法和游标法都是采用模拟的方法,虽然精度提高了,但是电路设计却很复杂;时『自J一电压变化法是利用电容的充放电时『BJ进行测量,由于经过A/D转换,速度较慢,且抗干扰能力较弱。多周期同步法精度较高的一种。为了进一步的提高精度,通常采用模拟内插法或游标法与多周期同步法结合使用,虽然精度有了进一步的提高,但始终未解决±1个字的计数误差,而且这些方法设备复杂,不利于推广。频率误差倍增法可以减小计数器的±1个字的误差,提高测量精度。但用这种方法来提高测量精度是有限的,因为如要得到2×1013的测量精度,就要把被测频率fI倍频到mf。=1/2×10“Hz=5000MHz,这无论是对倍频技术,还是对目Ij{『的计数器都是很难实现的。频差倍增一多周期法是一种频差倍增法和差拍法相结合的测量方法。这种方法是将被测信号和参考信号经经频差倍增使被测信号的相位起伏扩大,在通过混频器获得差拍信号,用电子计数器在低频下进行多周期测量,能在较少的倍增次数和同样的取样时『日J情况下,得到比测频法更高的系统分辨率和测量精度。但是仍然存在着时标不稳而引入的误差和一定的触发误差。以上只是对现存的几种主要的测频方法的概述,很显然从以上的分析中知道:不同的测频方法在不同的应用条件下是具有一定的优势的,而在本论文中,我主要在多周期同步法的基础上,采用了全同步的测频方法。主要是消除了±1个字的对时标信号的计数误差,而且在FPGA/cPLD芯片上实现,具有很大的优势。

总之,频率(时间)测量技术发展非常快。在频标方面,一方面是追求新的更高稳定度和准确度的新型频标,据报道,实验室中做出频率准确度优于lO-“的频标。一方面是提供便于工业、科研应用的商品化频标,如小铯钟、铷频标、新型高稳定度晶体振荡器等这些工作多在计量研究与工业部门进行。大量的工作在改进、创造新的测频原理、方法和仪器,以便以更高的精度、速度,自动进行测量和数掘处理,并向多功能、小型化、高性价比方向发展。在提高测频精度方面,值得特别提出的有全同步取样技术和可校准通用电子计数器技术,它们使测频精度提高到一个新的水平嘲。

1.4FPGA概述

FPGA是英文FieldProgrammableGateArray的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA采用了逻辑单元阵列LcA(LogicCellArray)这样一个新概念,内部包括可配置逻辑模块CLB(ConfigurableLogicBlock)、输出输入模块IOB(Input3

幕于FPGA的伞M步数字频牢计的设计

OUtputBlock)和内部连线(Interconnect)三个部分。FPGA的基本特点主要有:

1)采用FPGA设计ASIC电路,用户不需要投片生产,就能得到合用的芯片。2)FPGA可做其它全定制或半定¥0ASIC电路的中试样片。

3)FPGA内部有丰富的触发器和I/O引脚。

4)FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。5)FPGA采用高速CHMOS工艺,功耗低,可以与CMOS、TTL电平兼容。

可以说,FPGA芯片是小批量系统提高系统集成度、可靠性的最佳选择之一。

目前FPGA的品种很多,有XILINX的XC系列、TI公司的TPC系列、ALTERA公司的FLEX系列等。

FPGA是由存放在片内RAM中的程序来设置其工作状态的,因此,工作时需要对片内的RAM进行编程。用户可以根据不同的配置模式,采用不同的编程方式。

加电时,FPGA芯片将EPROM中数据读入片内编程RAM中,配置完成后,FPGA进入工作状念。掉电后,FPGA恢复成白片,内部逻辑关系消失,因此,FPGA能够反复使用。FPGA的编程无须专用的FPGA编程器,只须用通用的EPROM、PROM编程器即可。当需要修改FPGA功能时,只需换一片EPROMU口可。这样,同一片FPGA,不同的编程数据,可以产生不同的电路功能。因此,FPGA的使用非常灵活。

FPGA有多种配置模式:并行主模式为一片FPGA加一片EPROM的方式;主从模式可以支持一片PROM编程多片FPGA;串行模式可以采用串行PROM编程FPGA;外设模式可以将FPGA作为微处理器的外设,由微处理器对其编程。

FPGA芯片是特殊的ASIC芯片,除了具有ASIC的特点之外,还具有以下几个优点嘲:

1)随着超大规模集成电路(VeryLargeScaleIC,VLSI)工艺的不断提高,单一芯片内部可以容纳上百力.个晶体管,FPGA芯片的规模也越来越大,其单片逻辑门数已达到上百万门,所实现的功能越来越强,同时还可以实现系统集成。

2)FPGA芯片在出厂之I;i『100%都做过测试,不需要设计人员承担投资风险和费用,设计人员只需在自己的实验室罩就可以通过相关的软硬件环境来完成芯片的最终功能设计。所以,FPGA的资会投入少,节省了许多潜在的花费。

3)用户可以反复的编程、擦除、使用,或者在外围电路不动的情况下,用不同的实现软件就可以实现不同的功能。因此,用FPGA试制样本,能以最快的速度占领市场。FPGA软件包中有各种输入工具、仿真工具、版图设计工具及编程器等全线产品,使电路设计人员在很短的时间内就可以完成电路的输入、编译、优化、仿真,直至最后芯片的制作。当电路有少量的改动时,更能显示出FPGA的优势。电路设计人员使用FPGA进行电路设计是时,不需要具备专门的Ic深层次的知识,FPGA软件易学易用,可以使设计人员集中精力进行电路设计,快速将产品推4

向市场“卜_”1。

1.5

FPGA原理及结构

1.5.1查找表(Look-Up-TabIe)的原理与结构

采用查找表结构的PLD芯片我们也可以称之为FPGA:如altera的ACEX,APEX系列,xilinx的Spartan,Virtex系列等。查找表(Look—Up-Table)简称为LUT,LUT本质上就是一个RAM。

目前FPGA中多使用4输入的LUT,所以每一个LUT

可以看成一个有4位地址线的16xl的RAM。当用户通过原理图或HDL语言描述了一个逻辑电路以后,PLD/FP6A丌发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM,这样,每输入一个信号进行逻辑运算就等于输入一

个地址进行查表,找出地址对应的内容,然后输出即可。表1.1是一个4输裁尚

门的例子,说明了LUT的工作原理.

表1.1

FPGA中4输入的LUT的1.作原理

实际逻辑电路

LUT的实现方式

!地址戏

!墓当~

a,b,C,d输入

0000

:

4

l

I

1h1圳

l

输出。

l血盯)

地址

0000000l

逻辑输出

00O1

RAM叶1存储的内存

O00

0001

I

『

….

1111

ljll1

1.5.2基于查找表(LOT)的FPGA的结构

altera的FLEX/ACEX等芯片的结构如图1.1所示:

燕十FPGA的全同步数字频率计的设计

图1.1alteraFLEX/ACEX芯片的内部结构图

www.fpE‘tomcn

|生I1.2逻辑单元(LE)内部结构图

FLEX/ACEX的结构主要包括LAB,I/0块,RAM块(未表示出)和可编程行/q连线。在FLEX/AcEX中,一个LAB包括8个逻辑单元(LE),每个LE包括~个,uT,一个触发器和相关的相关逻辑。LE是FLEX/ACEX芯片实现逻辑的最基本结句。6

硕l’学位论史

1.5.3查找表结构的FPGA逻辑实现原理

以图1.3这个电路的为例:

^

日

C

D

CLK

图1.3简单逻辑电路幽

A,B,C,D由FPGA芯片的管脚输入后进入可编程连线,然后作为地址线连到到LUT,LUT中已经事先写入了所有可能的逻辑结果,通过地址查找到相应的数据然后输出,这样组合逻辑就实现了。该电路中D触发器是直接利用LUT后面D触发器束实现。时钟信号CLK由I/O脚输入后进入芯片内部的时钟专用通道,直接连接到触发器的时钟端。触发器的输出与I/O脚相连,把结果输出到芯片管脚。这样PLD就完成了图3所示电路的功能。这个电路是一个很简单的例子,只需要一个LUT加上一个触发器就可以完成。对于一个LUT无法完成的的电路,就需要通过进位逻辑将多个单元相连,这样FPGA就可以实现复杂的逻辑。由于LUT主要适合SRAM工艺生产,所以目前大部分FPGA都是基于SRAM工艺的,而SRAM工艺的芯片在掉电后信息就会丢失,一定需要外加一片专用配置芯片,在上电的时候,由这个专用配置芯片把数据加载到FPGA中,然后FPGA就可以J下常工作,由于配置时『HJ很短,不会影响系统正常工作。也有少数FPGA采用反熔丝或Flash工艺,对这种FPGA,就不需要夕lqJn专用的配置芯片。…,1.5.4其他类型的FPGA和PLD

随着技术的发展,在2004年以后,一些厂家推出了一些新的PLD和FPGA,这些产品模糊了PLD和FPGA的区别。例如Altera最新的MAXII系列PLD,这是一种基于FPGA(LUT)结构,集成配置芯片的PLD,在本质上它就是一种在内部集成了配置芯片的FPGA,但由于配置时I.日J极短,上电就可以工作,所以对用户来说,感觉不到配置过程,可以传统的PLD一样使用,加上容量和传统PLD类似,所以altera把它归作PLD。还有像Lattice的xP系列FPGA,也是使用了同样的原理,将外部配置芯片集成到内部,在使用方法上和PLD类似,但是因为容量大,性能和传统FPGA相同,也是LUT架构,所以Lattice仍把它归为FPGA。1.6VHDL简介

VHDL的英文全名是Very—High—SpeedIntegratedCircuitHardware

DescriptionLanguage,诞生于1982年。1987年底,VHDL被IEEE和美国国防部确

基于FPGA的会同步数’一频牢计的设计

认为标准硬件描述语言。自IEEE公布了VHDL的标准版本,IEEE-1076(简称87版)之后,各EDA公司相继推出了自己的VHDL设计环境,或宣布自己的设计工具可以和VHDL接口。此后VHDL在电子设计领域得到了广泛的接受,并逐步取代了原有的非标准的硬件描述语言。1993年,IEEE对VHDL进行了修订,从更高的抽象层次和系统描述能力上扩展VHDL的内容,公布了新版本的VHDL,即IEEE标准的

1076—1993版本,(简称93版)。现在,VHDL和Verilog作为IEEE的工业标准硬件描述语言,又得到众多EDA公司的支持,在电子工程领域,已成为事实上的通用硬件描述语言。有专家认为,在新的世纪中,VHDL与Verilog语占将承担起大部分的数字系统设计任务。

VHDL主要用于描述数字系统的结构,行为,功能和接口。除了含有许多具有硬件特征的语句外,VHDL的语言形式和描述风格与句法是十分类似于一般的计算机高级语言。VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可视部分及端口)和内部(或称不可视部分)。在对一个设计实体定义了外部界面后,一旦其内部丌发完成后,其他的设计就可以直接调用这个实体。这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。应用VHDL进行工程设计的优点是多方面的。

(1)与其他的硬件描述语占相比,VttDL具有更强的行为描述能力,从而决定了他成为系统设计领域最佳的硬件拙述语占。强大的行为描述能力是避丌具体的器件结构,从逻辑行为上描述和设计大规模电子系统的重要保证。

(2)VHDL丰富的仿真语句和库函数,使得在任何大系统的设计早期就能查验设计系统的功能可行性,随时可对设计进行仿真模拟。

(3)VHDL语句的行为描述能力和程序结构决定了他具有支持大规模设计的分解和已有设计的蒋利用功能。符合市场需求的大规模系统高效,高速的完成必须有多人甚至多个代发组共同并行工作才能实现。

(4)对于用VHDL完成的一个确定的设计,可以利用EDAI具进行逻辑综合和优化,并自动的把VHDL描述设计转变成门级网表。

(5)VHDL对设计的描述具有相对独立性,设计者可以不懂硬件的结构,也不必管理最终设计实现的目标器件是什么,而进行独立的设计。

硕I‘学位论文

第二章全同步频率测量方法的研究

2.1常用的数字频率测量方法

用于频率测量的方法有很多,频率测量的准确度主要取决于所测量的频率范围以及被测对象的特点。而测量所能达到的精度,不仅仅取决于作为标准使用的频率源的精度,也取决于所使用的测量设备和测量方法。因此,下面介绍集中常用的频率测量方法,分析他们的优缺点,从而提出全同步频率测量方法。2.1.1直接测频法

直接测频法是最简单的,也是最基本的频率测量方法,在测量过程中,依据信号频率高低的不同,测量方法也可以分为两种:

一、被测信号频率较高时(M法)

通常选用一个频率较低的标准频率信号作为闸门信号,而将被测信号作为充脉冲,在固定闸门时间内对其计数。设闸门宽度为T,计数值为N,则这种测量方法的频率测量值为:一l

六=等

总误差可以采用分项误差绝对值线性相加来表示,即:(2.1)测量误差主要决定于闸门时间T和计数和计数器计得的数的准确度,因此,

等=±b剀六(2.2)

I矾蚓J

其中,±去是最大量化误差的相对值,等=等=±麦,等的产生是由于测频时,闸门的刀:启时刻与计数脉冲之『日J的时问关系不相关造成的,即在相同的主门丌启时间内,计数器所得的数并不一定相同。当主门丌启时问T接近甚至等于被测信号周期T,的整数倍时,量化误差最大,最大量化误差为△Ⅳ=±1个数。:掣为标准频率的准确度,在数值上石英晶体振荡器所提供的标准频率的准确l_,ol

度等于闸门时问的相对误差△%的准确度,即:

一AT盟,(2.3)厶

式中负号表示由觚引起的闸门时间的误差为一△7’。9

基于FPGA的拿问步数宁频率计的设计

通常,对标准频率的准确度锊的要求是根据所要求的测频准确度而提出来的。因此,为了使标准频率误差不对测量结果产生影响,标准频率的准确度应高于被测信号准确度至少1个数量级。因此,测量较高的信号频率时,若fo一定,闸门时间T越长,测量准确度越高,当T选定后,fo越高,±1个数字误差对测量结果影响减小,测量准确度越高。

二、被测信号频率较低时(T法)

通常被测信号被选作闸门信号,而将频率较高的标频信号作为填充脉冲,进行计数,设计数值为N,标准频率信号的频率为fo,周期为To,则有:

伽志@‘4’

使用这种方法测频的误差主要是对标频信号计数产生的±1个数字误差,在忽略标准频率信号自身误差的情况下,测量精度为:

甑=±等(2.5)

由上可知:直接测频方法的优点是:测量方便,读数直接,在比较宽的频率范围内能够获得较高的测量精度。它的缺点是:由于被测信号±1个数字误差的存在,难以兼顾低频和高频实现等精度测量,所以测量精度较低。

2.1.2多周期同步测频方法

一、测量原理

多周期同步测频是在直接测频基础上发展起来的,在目前的测频系统中得到了越来越广泛的应用。它在测频时,闸门时间不是固定的,而是被测信号的整数倍,即与被测信号保持同步,因此消除了对被测信号计数所产生的±1个数字误差,使测量精度大为提高,测量原理框图如图2.1,测量原理的波形如图2.2。

标准信号f

预置闸门运

算

显

不

被捌信号f

图2.1多周期同步测频原理框图10

顾I。学位论文

预置闸门

被测信号fx

实际闸门

标准信号fcJ●TLZ仃亿刀刀刀●I111111111111111111111111111f

豳2.2多周期同步测频原理波形图

测量时,首先预置闸门开启信号,此时计数器并不计数,等被测信号上升沿到来时,触发器输出计数允许信号(实际闸门信号),计数器l对标准信号计数,计数器2对被测信号计数,预置闸门关闭时,计数器并不立即结束计数,而是等到被测信号上升沿到来时才停止计数,完成测量过程。

若计数器l对标准信号的计数值为N。,计数器2对被测信号的计数值N。,则被测信号频率为:

^,

正=詈正

』Vc(2.6)

运算器对式(2.6)进行运算,由显示器显示运算结果,即为被测信号的频率值。

二、误差分析

由误差合成公式有:

盟:坐一坐+笪

{xNI(2.7)Nclc

在(2.7)中第一项为被测信号引起的量化误差,由于实际闸门与被测信号同步,所以AⅣ.=0,即消除了被测信号计数所产生的±1个字的量化误差,由此得到最大相对误差为:

等=±陆+吲]正(2.8)l矾I丘U

式(2.8)说明频率测量的相对误差与被测信号的频率无关,其大小主要取决于闸门时间和标准信号频率,因而实现了频带内等精度、高精度的测量。当合理选择闸门时间和标准信号频率,既可保证测量精度;又可提高测量速度,因此多周期同步测频法得到了广泛的应用。而且由(2.8)式可知:闸门时『自JT越长,时基频率越高,分辩率越高,误差愈小。但是,多周期同步测频法还是没能够是时基

摹于FPGA的伞旧步数字频率计的设计

信号与被测信号以及闸门信号三者同步,从而产生的时基信号的±1个字的量化误差还没有消除。

2.2提高频率测量精度的方案研究

在多周期同步测频方法中,已经消除了被测信号的±1个字的量化误差,但是对标频信号的±1个字的量化误差还没有得到很好的解决。因此,下面在多周期同步测频方法的基础上,进一步分析提高测量精度的基本方法。

2.2.1采用对标频信号计数的修正来提高测量精度

1、双计数测频

该方法在多周期同步测频的基础上,提

高测频的精度。我们可以分别把标准频率

L的上升沿和下降沿分别作为计数器的计

数脉冲,最后的N等于2个计数器计数值的

算术平均值。其实这种方法相当于在不改

变系统的工作频率的情况下让其达到2倍

频的效果,以2f0的时钟频率进行计数,

从而将测量精度提高到原来的两倍。例如

直接用IOOMHz的f0作为标频计树脉冲时,

最大计数误差为10ns,而双沿计数的等效

时钟则为200MHz,计数误差为5ns,同时,

系统的最大工作频率并没有改变。

2、数字移相测频图2.3移相测频原理幽计数翱

这种思想与双计数测频具有累似的地方。所谓移相是以一路信号为参考,另一路信号的相位相对于参考信号超J;i『或滞后的移动。原理如图2.3所示。标准频率ffJ经过移相得到clkO、clkl、clk2、clk3,而clkl、clk2、clk3相对与clk0依次移相90度、180度、270度。四路信号分别作为计数器l、计数器2、计数器3、计数器4的计数脉冲,同时使T1为Tx的整数倍,并把Tl作为所有计数器的开始信号,N=(NO+NI+N2+N3)/4。但是由于clkl、clk2、clk3是fo的二分频,所以这种方法对于提高测频精度和双计数测频法是等效的,但是电路要复杂一些。如果采用FPGA内部资源来实现不分频情况下的精确移相,则其精确度可以提高4倍。

总之,以上两种方法可以在一定程度上提高频率测量的精确度,。但是还是很难抑制标准频率信号所产生的±1个字的量化误差。西安电子科技大学周渭发明了相检式多周期同步测频方法,能够采用相对简单的技术在同一闸门时问内准确

硕卜警位论史

的对标准频率信号和待测频率信号的整周期数进行计数,从而可获得很高的测频精度。

2.2.2相检式多周期同步测频法

1、相检式多周期同步测频法的原理”1

当被测频率量与标准频率量之间有频率差时,两信号的相对相位会随时间周期性变化。采用特定的相位检测电路,可以检测出被测频率信号相位重合的信息,并产生相应的相位重合脉冲,用此脉冲作为实际计数闸门的开门相关门信号。图

待测频辜专三i几厂]几几…一一一r]几厂]标准频率fQ;几几几几几几几几几n几几n几重合脉}中i卜

实际r回P'JTFee.Tf单eq"篱罄尊莲-J一一一一。———_—]门信号TEl

J玺I2.4相检式多周期同步测频法原理幽I!FF—————1:!I||_…一…一一iJL一

2.4是实际应用该方法的信号时序图。

f,和fo分别为被测频率信号和标准频率信号,Tg为预定闸门时间(可以是0.1s,Is,lOs),由单片机系统定时给定。当Tg上升为高电平给出预开门信号后,相位检测电路丌始工作,而对f。和f0的计数并没有真正开始,直到随后f。和f0同时达到上升沿或下降沿时,相位检测电路将产生相应的相位重合脉冲,用它打开真正的计数闸门,两路计数器同时对f,和f0分别进行计数:经过预定闸门时I'日JTg后,单片机给出预关门信号,但计数并没有停止,直到随后的第一个相位重合脉冲到来时才同时关闭两路计数器,这样,两计数器计得得分别是被测频率信号f。与标准频率信号f0的整周期数Nx和N。。对于以知得f0有:

六=瓮厶(2.9)

用此方法测量频率,理论上测量结果得误差只取决于相位检测电路得相位重合检测精度J(如使用74SXX系列得高速器件可使这个检测精度在时间轴上满足万≤3ns)。但是,实际上在这种测量方法中,待测信号和标准信号得频率值,频率差得大小都会对实际闸门时间得长短有影响。例如,当待测信号和标准信号的频率值相等或成整数倍或分数倍的关系时,一旦两信号有相位差,就不会有相位重合的时刻,两信号频差越小,实际的闸门时间就越长。另外,待测信号和标准信号的频率值,频率差也对测量结果的误差有影响。分析表明,当频率差不大时,

基于FPGA的伞问步敬‘一频率计的设计

两信号的相位从分离到重合是完全有规律的按一定的步长变化的。单片机给出预开门信号到相检电路检测到随后第一个相位重合信息并打丌闸门的过程,与单片机给出预关门信号到相检电路检测到随后第一个相位重合信息并关闭闸门的过程是完全一致的,因此,尽管相检电路检测相位重合的精度为J,但由于闸门开启和关闭是两信号相位变化过程的一致性,这个艿被最大限度的抵消了,测量精度就越高。但频差太小,两信号相位重合的频率也很小,由图2.4可知,实际闸门时间为Tgreal=Tg—TI+T2,当T2变大时会使得实际得闸门时间太长从而过多得偏离预设闸门时间。

在参考文献[6]中,通过一定的试验得出了以下的结论:在采用相检式多周期同步法测频,应考虑到被测信号频率与标准信号频率的频差关系对测量精度的影响。标准频率一定,被测频率与标准频率的频差越小,测量时相应的实际闸门时问会越长;而频差太大,考虑相检电路的分辨率后,被测信号和标准信号之间的相位重合脉冲的产生就无规律可循。无法利用两次相位重合脉冲产生时相同的重合到分离的规律抵消相检电路的检测误差,不能达到这种方法的最高测量精度。

2.3全同步数字频率计的工作原理

2.3.1全同步频率测量的误差分析

M法、T法的测量精度不仅取决于基准时J’日J和计数器的计数误差,还取决于频率的高低,频率不同则精度不一样,M法在高频段的准确度相对较高,T法在低频段的准确度较高。M厂r法则在整个测试频段的精度一样,闸门信号是被测信号周期的整数倍,即与被测信号同步,因此大大减少了误差,但山于只与被测信号同步,而不与标准时钟同步,因此还是存在着标准时钟±l计数误差。其测频原理图见图2.5。

标准时钟

门几几几几几几几几l

被测信号

厂]厂]厂]

参考闸门

等精度测频原理

图2.5等精度测频原理图14

硕I‘学位论文

设实际闸门时问为T。,在T。时间内,被测信号周期数为N。,标准时钟周期数为M0。标准时钟频率为fo,被测信号的频率测量值为。1:

∥=篆五

此可知被测信号的频率真值为:眨9,实际闸门时『日J忍为被测信号周期的整数倍,因此ⅣJ是精确的:而对标准时钟的计量值则存在误差△Moa△MoI≤1),即标准时钟计数的真值应为Mo+AMo由乒=去五晓㈣

M§Mq若不计标准时钟的误差。则测量的相对误差是:仃:垃型。loo%:幽≤上:上(2.11)llT%氏

由上式可知误差与闸门时间和时钟频率有关,闸门时『白J越长,标准时钟频率越高,误差越小。由于用等精度测频法时所取的标准时钟频率比较高(101v【dtz以上),因此±1计数误差相对很小。标准时钟频率不可能无限制提高,并且随着频率提高,产品成本成倍增加,对于生产应用没有意义。因此本设计用改进的等精度频率测量方法一全同步测量来实现数字频率计的设计。在全同步的情况下,闸门信号不仅与被测信号同步,还与标准时钟同步,实现真J下的同步。其原理图如图2.6所示。’

设丌启闸门时脉冲同步时|’甘J差为她,关闭闸门时脉冲同步时『白J差为△r:,脉冲同步检测最大误差为△f,则有:△f.≤At,At,≤△,。不计标准时钟误差,实际闸门与标准时钟同步,实际闸门时间为7’。被测信号计数值为N。标准时钟计数值为M【,,则被测信号的频率测量值为”’

z=丝To=旦Mo五JJJ0(2.12)……

被测信号频率的真实值可表示为:z=赤矗(2m)。

(2“)频率测量的相对误差为:盯:匿型。100%:!些±些』≤型正瓦To由上式可知,误差只与脉冲检测电路准确度有关。

摹十FPGA的伞问步数字频率计的设计

2.3.2全同步数字频率计原理框图

对于全同步数字频率计也可用传统的中规模集成电路来实现,但由于设计比较复杂,这样势必会使PCB板的面积过于庞大,因此不宜采用此种设计方法。其实本设计也可以用单片机来实现,灵活性则大大提高,但单片机的处理速度不够快,并且能够处理的频率也不够高,因此本设计也不采用此种方法。FPGA具有集成度高,一片FPGA等效于几十到几百万枚门电路,并且高频特性特别好,又由于其可编程,设计起柬事半功倍,因此本设计采用FPGA来实现全同步数字频率计。其系统原理框图如图2.7所示。由图知,设计的绝大部分由FPGA完成,只有脉冲同步检测电路由74LS系列与非门以及显示部分由数码管构成。

L

删信号广一标准时钟.F脉冲

同步

检测

电路G

A

图2.7系统原理图P—————-—-—-.h—————Jj显不电路——V|

其模块电路设计原理如图2.8所示。设计原理图主要由以下几部分组成.:脉冲同步检测电路、2个计数器、2个锁存器、控制器、乘法器、除法器、译码电路等组成。工作原理如下:被测频率与标准时钟分别送给脉冲同步检测电路与两个计数器,当脉冲同步检测电路检测到被测频率与标准时钟相位同步时,脉冲同步检测电路发出同步信号,2个计数器丌始计数,当脉冲同步检测电路再次检测到同步信号时,又发出同步信号,计数器停止计数。同时计数器的计数值锁存到锁存器,时序乘法器从锁存器中取得被测频率的计数值与标准时钟频率进行乘法运算,然后再将乘法器运算所得的值与标准时钟的计数值送给除法器,乘法器的结果为被除数,标准时钟的计数值为除数,运算所得结果就是被测信号的频率,然后再经过二十进制转换变成BCD码,送给数码管显示。本设计采用lOldHz的标准时钟,由于乘法器输入是27位二进制,相当于9位lO进制数,而IOMHz的标准时钟为107Hz,因此用被测频率的计数值乘以108可得到一位小数点。以下介绍各种模块电路的功能及实现过程。6

图2.8内部模块设计原理图17

基于FPGA的伞删步数’#频率计的设计

第三章基于FPGA器件的功能模块电路设计

3.1脉冲同步检测电路

脉冲同步检测电路是本设计中提高测量精度的关键电路,如果把它集成在FPGA器件中,很难达到测频精度的要求,因此本模块电路的设计采用74SXX的高速器件束进行设计,可以使相检误差控制在几个rls。

脉冲同步检测电路设计原理图如图3.1所示。U.’U。为74SXX系列与非门,同步检测电路利用门电路的延时来构成。当被测信号及标准时钟都处在低电平时,U.、U。输出为高电平,U。、U。的输出为高电平,U5、U。输出为低电平,则u瀚出为低电平。当被测信号(Fx)及标准时钟的上升沿同时到来时,由于门电路具有延时特性,因此U。、U:并不马上变为低电平,而是要经过一个延时/j。变为低电平。于是u,、U。的输入端都是高电平,则u,、U。输出为低电平,uj、u。的输出为高电平,则u。输出为高电平。但是当且仅当Fx与Clk的上升沿在在延时时|’日J内同时到达时u。才会输出高电平。这个高电平作为丌启信号启动实际的闸门信号,使被测信号,标准信号和闸门信号达到相对的同步,同理,当再一次检测到Fx与Clk的上升沿在在延时时间内同时到达时则关闭闸门信号。这样以来,使测最精度得到大大的改善。

74SXX系列与非门的延时最小为4ns,最大为15ns,因此最大误差为lins。根据公式(3.1)得:

盯;型:!!!!!!!::辈

roro109ro(3.1)

当T0为lS时,其精度可达N10罐,再减小相位重合误差,则可提高频率计的精确度。

图3.1脉冲同步检测电路8

3.2计数器

此计数器为27位二进制,实现对标准频率信号和被测频率信号进行计数。它具有计数使能端(ena)、异步清零端(clr)、州钟输入端(clk)、进位输出端(ov)等。当异步清零端(clr)为高电平时,不管计数使能端是否有效,时钟上升沿是否到来,计数器都立即清零,lipq=O。只有异步清零端(clr)为低电平,并且计数使能端为高电平,有上升沿到来时,计数器才开始计数,当计数器计满时,进位输出为高电平。计数器VHDL程序仿真图如图3.2所示。从仿真图上可知:此计数器具有良好的控制和计数功能。

计数器的VHDL源程序如下所示:

1ibraryieee:

useieee.std_logic一1164.all:

ieee.std-logic—UDSigned.a11:use

entitycounter30is

std—logic;port(clk,clr,ena:in

ov:out

q:outstd—logic:std-logic—vector(26downto0)):

end:

architecture

signal

signal

beginbhvofcounter30isdowntoq_temp:std—logic—vector(26o:std—logic:0):

process(clk,clr,ena)

begin

ifclr=’1’thenq_temp<=”000000000000000000000000000”:

else

ifclk’eventandclk=’1’then

ifena=’1’then

ifq__temp<”101111101011110000011111111”then

q_temp<=q_temp+l:。

elseo<=’l,:q_temp<=”000000000000000000000000000’:

endif:

endif:19

摹于FPGA的争蚓步数7频率计的设计

endif:

endif:

endprocess:

q<=qtemp:

ov<=o:

end:

Name:

监鹫f—enaValue1200.0ns4000ns5000ns日∞On

鞋蛰净clr0

1

0

D00X1X2X3X4X5X0匿沪clk-%0簿0V每泣qX1

图3.2计数器仿真图

3.3锁存器

锁存器的作用就是当时钟上升沿到来时将计数值锁存到触发器中。非常简单,因此本设计没有编写专门的锁存器程序,具体程序请查看顶层文件中的相关锁存器内容。

3.4乘法器

由于本设计所用的乘法器位数较宽,而组合逻辑乘法器位数越多耗用的硬件资源成倍增长,并且本设计不需要有很高的运算速度,考虑到硬件资源与运算速度,因此采用时序电路来实现乘法器。它是~种牺牲运算时『白J换取硬件资源的方案。

时序逻辑乘法器的原理是,乘法可以通过逐项移位相乘相加来实现(如图3.3所示)。20

II

1I0I1(B)(A)(×)

0O

1Ol0(+)lI

10010lI(P)

图3.3时序逻辑乘法运算原理图

设乘法器的输入为A、B,其宽度为N位,则乘积P宽度为2N位。计算步骤如下:

图3.4乘法器软件流程图2

摧十FPGA的伞同步数。#频率计的设计

(1)A向右移动一位。

(2)A的低位为高电平,则P(2N一1

即无操作。

(3)

(4)downtoN)=P(2N一1downtoN)+B:否贝lJp=p,P向右移动一位,加法的进位移入P的高位。重复(1)’(3)步骤,直到A中的最高位移出寄存器(共需N次操作)…。乘法器软件流程图如图3.4所示。

乘法器是通过加法器来实现,因此先介绍加法器,考虑到加法器耗用的资源不是很多,因此为节省时间,直接用VHDL的算术运算包来实现加法运算,其程序相对比较简单,请参见附录1.1。其仿真结果如图3.5N示.

Navoe

Cm

cOut

a10口Ons002DD.Ons3000nlD100

Db

S1咖D1100画[)[至叵X亘可面—1—订玎—_!越f而1婴)(!堕X!!!

图3.5加法器仿真图

乘法器的输入必然有乘数A和B,输出有积P。此外,为了使用方便,还给出四个接口信号start、finished、f和df。start信号为输入信号,它若为高电平,那么乘法器将异步复位并丌始计算。finished信号为输出信号。如果finished为低电平,则表明乘法器正在进行一项乘法,这时如果start信号有效,那么乘法器将忽略start信号,继续进行原来的乘法计算。如果finished为高电平则表明乘法器空闲,这时只要start信号有效,乘法器就会立即丌始计算。一一一一一一一一一一一一…一一一一].冈

佑0.start!竺!!!

A移位

寄存

器A

输入电路结果

B寄存

器B加法器移位

寄存

器PP

L.……一一二………一JI乘法器I

图3.6乘法器原理图

硕f学位论文

图3.7乘法器仿真图

乘法器的结构框图如图3.6所示。它包括移位寄存器A、输入寄存器B、结果移位寄存器P、加法器和控制电路。移位寄存器A实现A的右移一位操作。输出寄存器B实现数据B的存储。结果移位寄存器P则实现数据P的右移一位操作。加法器是一个宽度为N的加法器。控制电路负责把其他所有的模块连接起来,并给出控制时序。它的主要组成部分是两个计数器:主节拍和副节拍计数器。主节拍计数器的值为0时,乘法器仞始化,结果移位寄存器清零。主节拍计数器的值为1’N时,对应N次移位相加操作。主节拍计数器的值为N+I时,乘法器停止工作。副节拍计数器的模为3,它的计数输出每个时钟周期都会变化一次,即副节拍计数器计数值变化3次后,主节拍计数器的计数值才会变化一次。副节拍计数器的计数值代表每个移位相加操作的具体步骤,其计数值为oN表示正在进行加法运算,l则表示币在实现把加法的结果存储到结果移位寄存器P中,其计数值为2则表示结果移位寄存器P右移一位,并把加法的进位移入结果寄存器的最高位。控制电路还负责接收start信号,产生finished信号Ⅲ,同时为了方便除法器取数,控制器还产生两个输出端f和df,这两个输出端对于乘法不是必要的,但从乘法器得到这两个用于除法器的信号比较方便,df用于把标准时钟的计数值锁存到除法寄存器中,防止乘法运算时间过长面导致数据丢失;另一个用来通知除法器乘法运算已经结束并且结果已经锁存到除法器寄存器中,可以丌始除法运算了。其仿真图如图3.7所示。

乘法器的VHDL的源程序如下:

libraryieee:

useieee.std—logic_l164.all:

ieee.std_logic_unsigned.a11:

entitymultnisuse

generic(dw:integer:=27):

摹于FPGA的伞间步数’7-频率计的改计

port(

clk:

a:

std—ogic:std—std—std

一时钟

downtodownto

ogic—vector(dw一1ogic_vector(dw一1

0):~乘法器输入0):一乘法器输入

0):一乘法器输出~乘法运算丌始信号一乘法运算结束信号一被除数锁存信号

一除数锁存信号

b:

P:out

logic—vector(2*dw一1

downto

start:instdlogic:finished:buffer

f:out

Std_logic:

stdlogic:

logic

df:outstd

):

end

architecturebhvofmultnis

signalsignalsignalsignalsignal

a-slg:s

td—logic—vector(dw一1

to

downto

0)

count:1ntegerrange0dw+l2:

count2:integerrange0to

qx:Integerrange0

to

2:

qf:integerrange0to2:

componentadder28

generic(dw:integer:=27):

port(

cin:ina:in

std-logic:

std—logic_vector(dw一1

c

downtodowntodownto

b:instd—logi

s:outcout:out

vector(dw一1

std—logic—vector(dw一1std_logic

叭叭∞

):

endcomponent:

S

gnalgnalgnalgnal

adder_a:sttlogic—vector(dw-I

adder_b:std_logic—vector(dw—l

downtodownto

O):0):

SS

adder—sum:std-logic_vector(dw-Iadder—cin:std_logic:

downtoO)

S

S

gnaladder_cout:std—logic:gnal

S

zero:st吐logic—vector(dw-I

downto0)

signalp_sig:std-logic—vector(dw*2—1downto0)signalff:std_logic:

begin

ul:adder28portmap(

cin=>adder_cin,

a=>adder_a,

b=>adder_b。

s=>adder—SUm,

cout=>adder_cout

):

~主控进程

process(clk)

begin

if(clk’eventandclk=’0’)then

if(count=Oandcount2=O)then

p_sig(dw*2—1downtodw)<=zero:p_sig(dw一1downto0)<=zero;

elsif(a_sig(0)=’1’andcount2=O)thenelsif(a_sig(0)=’1’andcount2=1)then

p_sig(dw*2—1downtodw)<=adder—sum;elsif(count2=2andcount/=count’high)then

p_sig(dw*2—2downto0)<=psig(dw*2—1downto1)p_sig(dvr*2—1)<=addercout:

endif:

endif:

endprocess:

一控制加法器

process(clk)

begin

if(clk’eventandclk=’0’)thenif(a_sig(0)=’1’)then

肇于FPGA的伞M步数’一频率计的设计adder_a(=p_sig(dw*2—1

adder_b<=b:

addercin<=’0’:

else

adder_a<=zero:

adder_b<=zero:

adder—cin<=’0’:

end

end

endprocessifif:downtodw)

process(clk)

begin

if(start=’1,)andfinished=’l’then

count<=O:

count2<=O:

finished<=’0’:

elsif(clk’eventandclk=’1’)then

andif(count=count’high

count<=cOunt:

count2<=count2

finished<=’l’:count2=count2’high)then

elsiI(count2=count2’high)then

count2<=O:

count<=count+l

finished<=’0’:

else

count2<=count2+1

finished<=’0’:

endif:

endif:

endprocess

process(clk)

begin

if(clk’eventandelk=’0’)then

if(count=O)then

a_sig<=a:

elsif(count2=2)then

a_sig(dw一2

a_sig(dw一1)

else

a_sig<=a_sig

endif:

else’downto<=’0’:0)<=a_sig(drldowntoI)

a一819<3a_slg

endif

endprocess

process(clk,finished)begin

iffinished=’0’then

elsifclk=’I’andqx<=O:thenclk’event

ifqx<qx’highthen

qx<=qx+l:

elseqx<=qx

endif:

endif:

endprocess:

Process(clk,finished)begin

iffinished=’I’then

elsifclk=’1’andqf<=O:thenclk’event

ifqf<qf’highthen

qf<=qf+l:

elseqf<=qf:

幕于FPGA的伞M步数’一频牢计的设计

endif:

endif:

endprocess

process(qx)

begin

ifqx=lthen

f<=’1’:

elsef<=’0’:

endif:

endprocess:

process(qf)

begin

ifqf=1then

df<=’1’:

elsedf<=’0

endif:

endprocess:

process(finished)

begin

iffinished=’l,then

p<=p_sig;

endif,

endprocess:

gl:foriin0todw一1generate

zero(i)<=’0’:

endgenerate:end:

母!I。学位论史

3.5除法器

ll

0

ll1l

1

O

0Ill1(A)(B)(÷)ll(一)】0l(I)(一)1

0(1)00

图3.8时序逻辑除法运算原理图

图3.9时序逻辑除法器软件流程图

除法器则可通过移位相减相除来实现,其实现过程见图3.8。其软件流程图如图3.9所示。减法器不作介绍,程序见附录1.2,仿真图见图3.12。除法器与乘法器的工作原理是一样的,但比乘法器稍微复杂一点,因为乘法器不需要比较是

幕于FPGA的伞旧步数’#频牢计的设计

否要进行加法,只要看移位寄存器的结果就知道是否要进行加法操作,而除法器则不一样,要求比较中间数据与除数的大小,如果除数大于中间数据则不进行减法,对应的结果寄存器置0,否则就置1。其余的工作过程类似,可参见乘法器的实现,原理框图如图3.10所示。仿真结果见图3.11。由仿真结果知除法器和乘法器一样,其结果的输出与数据的输入有一段时间|’日J隔,这是因为乘除法器是由时序逻辑电路构成的,计算结果需要很多个时钟周期爿+能得出结果。由于时序电路的这种特性,因此必须等到运算结果才能允许下一次输入,否则不允许输入,这就是要设置start信号和finished信号原因。

B

A

Name:Value:,

D

1

0

D12D020。40.us4a0.us&炉startt炉clk—国眵finishedn厂1999

3

0∥a∥b蚴PXX333D3D333

Name:Value:,1013.Ons200:Ons300.Om

。

《∞pcln0Il-§:≯coutD

断aD1015

莲盘泸bD55

斛s—而—丫1F](—西T!!婴X!!婴X!塑!ID9即婴夏塑孤!!!墨

图3.12减法器仿真图

除法器的VHDL源程序如下:

1ibraryieee:

useieee.sttlogic-1164.all:useieee.std—logic_unsigned。all:

entitydivideris

generic(dw:integer:=27):

port(

clk:instd_logic;

a:instd-logic_vector(dw*2一ldownto0):一被除数b:inst九logic—vector(dwdownto0):一除数p:outstd—logic—vector(dw*2—1downto0):一一商start:instd-logic:一开始信号finished:bufferstd_logic一结束信号

):

end:

architecturebhvofdividerissignalasig:std—logic—vector(Otodw*2—1)一被除数暂存器signalcount:integerrange0todw*2+1:一主计数器signalcount2:integerrange0to2:~副节拍计数器

componentsubber

generic(dw:integer:=28):

port(

cin:instd—logic:

a:instd_logic—vector(dW-ldownto0):b:instd_logic—vector(dw一1downto0):s:outstd_logic—vector(dw一1downto0)3I

举于FPGA的伞Ifd步数’一频率计的设计

cout:out

std_logic):

endcomponent:

mgnal

signal

subber_a:std_logic_vector(dwsubber_b:std—logic—vector(dw

downtodownto

0):0):

~减法器输入A一减法器输入B

mgnalsubber_sum:std_logic_vector(dw

signal

subber_cin:std—logic:subber—coot:std—logic:

downto

0):一结果输出一借位输入一借位输出

mgnal

signalsignalsignalsignalbegin

zero:std—logic—vector(dw一1p_sig:std—logic—vector(dw

downtodownto

0):0):0):

一零

一余数寄存器一商寄存器

p_r:std_logic—vector(dw*2一l

comr:std—logic:

downto

一判断信号

ul:subber

port

map(

cin=>subber—cin,

a=>subber

a,

b=>subber—b,s=>subber—sum,cout=>subber—cout

):

~主进程负责系统协调

process(clk)

begin

if(clk’event

andclk=’1’)then

and

if(count=Ocount2=O)then

p_sig(dw)<=’0’:p—sig(dw一1

downto

0)<=zero;p—r(dw*2—1

downto

dw)<=zero

D

r(dw一1

downto

O)<=zero:

elsif(comr=’1’andcount2=O)then一等待

elsif(comr=’1,andcount2=1)then

p

sig<=subber_sum;

and

一结果送寄存器

elsif(count2=2count/=count’high)then

32

pr(dw*2—1downto1)<=p_r(dw*2—2downto0)

p_r(0)<=comr:

p_sig(dwdownto1)<=psig(dw一1downto0)

p_sig(0)<=asig(count):

end

endif;if:

endprocess:

一比较器

process(count2)

begin?if(count2=O)then

if(p_sig(dwdownto0)>=band

comr<=’1’:b/=”0000000000000000000000000000’)then

elsecomr<=’0’:

endif;

endif:

endprocess:

~控制加法器输入

process(clk)

begin

if(clk’eventandclk=’1’)then

if(comr=’1’)then

subber—a<=p—sig;

subber_b<=b:

subber_cin<=’0’:

else

subbera(dw-1downtoO)<=zerosubber_a(dw)<=’0’:subber_b(dw一1

subberdowntoO)<=zerob(dw)<=’0’:subber_cin<=’0’:

endif;

endif;

基于FPGA的伞耐步数‘≯频率计的-垃计

endprocess

一控制状态机

process(clk)

begin

ifstart=’1’andfinished=’1’then

count<=O:

count2<=0:

finished<=’0’:

elsif(clk’eventandclk=’1’)then

if(count=count’highandcount2=count2’high)then

count<=count:

count2<=count2:

finished<=’1’:

e1sif(count2=count2’high)then

count2<=O:

count<=count+l:

finished<=’0’:

else

count2<=count2+1

finished<=’0’:

endif:

endif:

endprocess:

一控制乘数A寄存器

process(clk)

begin

if(clk’eventandclk=’0’)then

if(count=O)then

a_sig<=a:

else

a_sig<=a_sig:

endif:

硕I。学位论文

else

a_sig<=a_sig

endif:

endprocess:

一结果输出

process(finished)

begin

iffinished=’1’then

p<2pr:

endif;

endprocess:

gl:foriin0todw一1generate

zero(i)<=’0’:

endgenerate:

end:

3.6控制器

控制器工作时序如下:当同步信号(clk)上升沿到来时,计数使能信号(cp)立即变成高电平,锁存信号(creg)及清零信号(clr)变成低电平,同步信号(clk)的上升沿再次到来时,除清零信号(clr)外,其余信号均取反,当同步信号(clk)的下降沿到来时,清零信号(clr)变成高电平。当同步信号又到来时,重复上述过程,软件流程图如图3.13所示,其仿真结果如图3.14所示。

控制器的VHDL源程序如下:

1ibrary

useieee:ieee.std_logic_1164.al1:

isentitycontrol

port(clk:instd_logic:

creg:buffer

clr,cp:out

endentity:一同步信号std-logic:~锁存信号std—logic);~清零与计数使能信号

摹于FPGA的伞f嗣步数‘}颍率计的设计

architecturetrof

signal

beginc:stdlogic:controlis

process(clk)

begin

ifclk=’1’andclk’eventthen

c<=notc:

endif:

endprocess:

process(c,clk)

begin

ifc=’0’andclk=’0’thenclr<=’1’:

elseclr(=’0’:

endif;

endprocess:

creg<=notc:

cp<=c:

end:

图3.13控制器软件流程图

痧|I+学位论文

图3.14控制器仿真图

3.7译码电路

译码电路的主要功能是把二十进制转换得到的BCD码送给数码管显示,为节省管脚数,数码管采用动态扫描的方式显示,则译码输出由数据总线和数码管的位选总线构成,由于采用的数码管为共阴极数码管,则低电平表示该数码管被选中,同时相应位的数据被送到该数码管上显示。程序见附录1.8的相关程序,其仿真图如图3.17。如果没有外接译码器,例如74LSl38,则使用cnt信号控制数码管的阴极,如果外接了译码器,则使用cnt9控制译码器的输入端,译码器的输出端控制数码管的阴极。

3.8二十进制转换模块

二十进制转换模块的功能是把二进制数转换成十迸制数BCD码。由于转换电路对速度没有要求,为节省硬件资源,转换电路由时序逻辑电路构成,由时钟控制转换过程的进行。本转换模块可将30位二进制数转换成10位BCD码,其工作过程如下:设置10个BCD码计数器,分别为a00~a09。如果除法运算未完成,则处于等待状态,完成了则丌始转换,首先把二迸制数送入暂存器a,a00’a09清零,当时钟上升沿到来时,如果a大于999999999时,D|a自减1000000000,同时a00自加l,如果a大于99999999时,则a自减100000000,同时aOl自加l,如此下去,直到a<9,则停止计算,同时把a的值赋给a09。然后再把a00。a09相并后送给bcd则得到10位BCD码输出“1。软件流程图如图3.15所示。仿真结果如图3.16所示。本电路只有转换丌始信号,任何时候有数据信号过来,只要clk为低电平都会被接收,只要高电平一来就会丌始转换,但由于乘法器、除法器的运算时间大于本电路的运算时间,因此,在运算过程中不会有干扰信号过来,不存在一次运算还没有完成,下一次运算就到来的情况。

摹fFPGA的令删步数‘一频率计的设计

图3.15二十进制转换模块软件流程图

Name:Value:1020

、O.usO.us30;

t盏—一clkO1

誊o—-clk1UU一

123456789

也bcd妒hdX999999

0000000000X0123456789

图3.16二十进制转换模块仿真图

二十进制转换模块VHDL源程序如下:libraryieee:

ieee.std—logic_1164.all:

ieee.std-logic_arith.all:

ieee.std—logicunsigned.all:

btodis

std—logic:~转换丌始信号

clkO:instd—logic:~标准时钟hd:instd_logic—vector(29downto0):一二进制数输入端bcd:outstd—logic—vector(39downto0)一BCD码输出端tecturevhfofbtodisuseuseuseentityport(clk:in):end;archj

signal

begina00,a01,a02,a03。a04,a05,a06,a07,a08,a09:integerrange0to9

process(clkO,clk,hd)

variablea:integerrange0to1000000000:一二进制数暂存器begin

ifclkO=’1’andclkO’eventthen

ifclk=’0’then

a:=convinteger(hd);a00<=O:aOl<=O;a02<=O:a03<=O;a04<=0:a05<=O:a06<=0

a07<=O:a08<=O:a09<=O:

else

ifa>999999999thena:=a-1000000000:aOO<=a00+l:。elsifa>99999999

elsifa>9999999

elsifa>999999

elsifa>99999

elsifa>9999

elsifa>999

elsifa>99

elsifa>9

elsethena:=a一100000000:a01<=aOl+l:thena:=a-10000000:a02<=a02+l:thena:=a-1000000:a03<=a03+l:thena:=a-100000:a04<=a04+l:thena:=a-10000:a05<=a05+l:thena:=a—1000:a06<=a06+l:thena:=a-100:a07<=a07+l:thena:=a-lO:a08<=a08+l:a09<=a;

ifa<10then

bcd(39

bcd(35

bcd(31

bed(27

bcd(23

bcd(19

bcd(15

bcd(11

bcd(7

bcd(3downtodowntodowntodowntodowntodowntodowntodowntodowntodownto36)<=cony—std—logic_vector(a00,4):32)<=COnV—std—logic—vector(a01,4):28)<=conv—std-logic—vector(a02,4):24)<=COBV—stdlogic_vector(a03,4):20)<=conv—std—logic—vector(a04,4):16)<=conv—std-logic—vector(a05,4):12)<=conv_std-logic—vector(a06,4):8)<=conv—std_logic_vector(a07,4):4)<=conv_std—logic—vector(a08,4):0)<=cony_std_logic—vector(a09,4):endif:

筚干FPGA的拿旧步数’7-频率计的设计

endif:

endif:

endif;

endprocess

3.9顶层VHDL程序设计及整体仿真结果

把以上各模块按照图2.8进行组合后得到顶层文件,源程序见附录B1.3,编译通过后进行仿真,如图3.18所示。由仿真图可看出:124×10‘÷93=i3333333,由于使用的是10MHz的晶振,因此还有一位小数点最终显示的结果应该是

1333333.3Hz。由仿真图3.17知,小数位在数码管的第二位上有效,其余位均无效。仿真结果与期望结果一致。

在图3.17中是经过局部放大而得到的仿真图,可以比较清楚的看到数码管的显示情况:1001111显示数码3,0000110显示数码l,Ollllll显示数码0,并且还有小数点的指示在倒数第二位上,说明最后在数码管上的显示为:01333333.3。这与理论的计算结果完全相同。在图3.18中是经过缩小的仿真图,可以清楚的看到两组数据,其中一组是:124×10:.93=13333333;另一组数据是:13×101÷69=1884057。这充分说明了本设计的谁确性。由于本设计采用的lOMHz的标准基准频率,因此被测信号的频率不能太高。如果超过IOOMHz的频率通过本系统进行测量则会使测量误差增大,同时FPGA器件的内部计数器也不能满足要求。但是本系统可以通过加上一定的扩展电路,从而实现对更高频率的测量。这个问题将在展望中加以讨论。

妒dkO

妒dkl

l扣幽-1口UUUUUUUUUn几几几几几几nnr]几几几n门厂]几几几几几几

O

?口Dl嵇硼话喇

屹多如Xl1Il2I3llX5i6’X7I8X工11111110111{1111D1111111101Illllll口11”静"0111111110111111”011”{{1和11111i11I_

10011H1‘幽qZ0000110Ⅱ0111111l

学P

‘驴甲一ckO01∞?Ⅱ1∞拗337

翻蝠y掣』酗口2加

图3.17整体仿真图l图3.18整体仿真图2

41

基于FPGA的伞卜d步数’7-频率计的设计

第四章FPGA配置方案的设计

4.1EPFIOK30ATI144-3FPGA芯片简介

本系统所使用的FPGA芯片为EPFIOK30ATll44-3的FLEX系列芯片,其管脚数为144,封装为TQFP,工作电压可选择5V或3.3V,典型可用门数为30,000,最大可用系统门数为69,000,逻辑单元(LEs)为1,728,逻辑阵列块(LABs)为216,嵌入式阵列块(EABs)为6,总的RAM为12,288位,最大用户使用I/0口为246个。4.2EPC2配置芯片简介

本系统使用的专用配置芯片为EPC2,该芯片数掘传输方式为串行传输,与FLEX系列的芯片相接的管脚只有4个,连接相当简单。支持MAX+PLUSTl软件平台,能够用MAX+PLUSII自带的编程器进行下载。封装形式有多种:8脚的PDIP封装、20脚的PLCC封装以及32脚的TQFP封装。其存储空『日J为l,695,680位。能够对

FLEXlOK、FLEX6000、FLEX8000系列芯片进行配置。支持5V和和3.3V电压,能够在MAX+PLUSII平台下通过BitBlaster、ByteBlaster和ByteBlasterMV电缆进行下载,支持Ps及JTAG下载模式”…“。

4.3配置模式

FPGA有多种配置模式。对于A1tera公司的SRAMLUTFPGA器件,FPGA有六种配置模式,这些模式通过FPGA上的两个模式选择引脚MSELl和MSEL0上设定的电平来决定”1:

(1)专用器件配置模式,如用EPC系列器件进行配置。

(2)PS(PassiveSerial被动串行)模式:MSELI=O、MSELO=O。

(3)PPS(Passiveparallel

MSEL0=0。Synchronous被动并行同步)模式:MSELI=I、

(4)PPA(PassiveparallelAsynchronous被动并行异步)模式:MSELl=1、MSELO=I。

(5)PSA(PassiveSerialAsynchronous被动串行异步)模式:MSELI=I、MSELO=0。(6)JTAG模式:MSELI=0、MSELO=O。

硕十学位论文

4.4下载方式

FPGA的配置方式有多种,但总的来说下载方式只有两种:PS下载和JTAG下载方式。这两种方式的硬件电路连接图如图4.1所示。图中只是这两种下载接口电路的介绍,它既可以用JTAG接口下载,也可以用ByteBlaster接口进行下载。不过用JTAG方式是先把数据下载到EPC2器件,EPC2器件再对FPGA进行配置,其实用JTAG方式也可以直接把数据下载到FPGA中,但图中没有画出来,有兴趣可以参考后面的相关参考文献。图中的ByteBlaster接口既可以直接下载到FPGA器件,也可以在配置FPGA的同时把数据下载至UEPC2器件中(图中开关要合上)。而在实际应用过程中,并不一不定要这样接,我们可以只选择其中一种下载接口。而在把研究设计转换成产品的时候则一定要用配置芯片,配置芯片在掉电的时候可以保存数据,下次加电的时候数据可以直接从配置芯片中下载到FPGA中。

FIEXloK器什

MSELI

MS日D

VCC

VCC嘛j

VCCIO-J

黧li秽mnC∞----NC

图4.I卜载接口原理图

本设计对配置器件EPC2采用JTAG下载方式,数据同时下载到EPC2和FPGA中,EPC2对FPGA的配置采用PS(被动串行).模式。其电路原理图见图4.3左边部分。4.5硬件电路原理图设计

本设计工作电压为5V,对FPGA芯片配置采用PS模式,用ByteBlasterMV电缆进行下载,数码管用动态扫描方式进行显示(可以用静念扫描,此种FPGA有足够

43

幕十FPGA的伞M步数字频率计的设计

的引脚,但程序要变),其硬件电路图如图4.2’4.4所示。54脚接IOMHz标准时钟,55脚接被测信号时钟,63、64、65、67、68、69、70、7l脚分别接数码管的A、B、C、D、E、F、G、DP端,用于控带q数码管的段选。73、78、79、80、81、82、83、86脚分别接数码管1’8的公共端(阴极),用于控制数码管的位选。同步时钟从125脚输入,其他的为系统引脚。由电路图可以看出用FPGA设计电路的外围电路相当简单,设计起来事半功倍。

萋一

三ipVCC

j翌亘dm

量F—m—焉彳蒯vcc…世雌荆。蝌=蚍掣蝴

图4.2硬件电路图1

44

clksclkx

图4.3硬rl:电路幽2a

b生世

一一一一一一一一一。盆却∞Lc;g卸一一一一一一一一

.

a

一一一一一一一一;

g却癣却∞L。一癣Gm

cntldocnt2幽4.4硬件电路图3

摧于FPGA的辛删步数’一频率计的设计

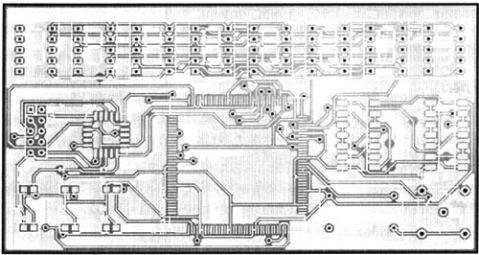

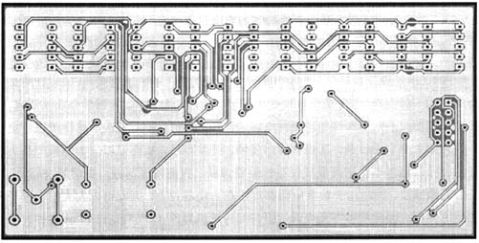

第五章PCB系统板的设计

印制电路板(PCB)的设计是电路能否调试成功的关键。PCB板布线的好坏直接影响电路的性能,如果布线没有按照约定的规则,那怕电路原理图完全没有错误,PCB板的调试也可能不成功或者不稳定。一般来说PCB板的布线主要有以下规则:

1)电源线要尽量宽,因为电源线中要流过较大的电流,如果电源线不够宽,则有可能承受不了系统要求的电流,烧毁电路板。地线也一样,如果地线不够宽,当有较大的电流流过的的时候,地电位将急剧上升,影响电路的参考点,导致电路不稳定。一般来说地线的宽度应大于电源线的宽度。

2)电源线中的关键地方需要使用一些抗干扰元器件,例如磁珠、磁环和电源滤波器等,以提高电路的抗干扰能力。

3)电源入口应该接去耦电容,一个高频和一个低频去耦电容。高频去耦电容的容量为几十到几百pF,低频去耦电容的容量为几十到几百uF。

4)印制电路板的模拟地和数字地要尽量分丌,最后通过电感汇接到一起。低频电路采用单点接地,而高频电路则应采用多点接地。

5)印制电路板的模拟部分与数字部分也应该分丌布局。接口电路放在电路板的边缘,以便于电路的调试。

6)印制电路板中的时钟发生器、晶振和CPU(或主芯片)的时钟输入端等尽量靠近,远离低频器件、数据线和噪声敏感元件,以降低高频脉冲干扰。

7)设计人员尽量采用45。或135。折线而不采用90。折线,这样布线可以减小高频信号对外的发射与耦合。

8)石英晶体的外壳一般要接地,另外石英晶振下面和对噪声特别敏感的元器件下面不要走线,最好覆铜并且接地。

9)时钟线应尽量与数据线垂直,这样可以有效降低脉冲干扰。

t0)由于走线的路径不一样,同类型同功能的信号可能不在同一时『日J内到达,导致电路不稳定或误动作。因此,也可以用蛇形线进行延迟。

11)印制电路板中的任何信号都不要形成环路,如果实在是不可避免出现的话,应该尽量减少相应的环路面积。

12)每10片左右的集成电路要加一片充放电电容,或者称为蓄放电电容,电容大小一般为lOuF。

13)5/5规则:在时钟频率超过5MHz时,或上升沿小于5ns时,就需要使用多层电路板。但这个规则不是绝对的,对于高速边沿速率的器件和时钟而占,只要设计和布局合理,不一定满足5/5规则就要用多层板,同样可以使用双层板来完

硕f‘学位论文

成设计。

14)3W原则:走线问的距离间隔(走线中心『日J的距离)应该至少是走线宽度的3倍,也就是说走线问的间距应该大于走线宽度的两倍。一般而占,采用3w规则可以减小队70%的辐射能量,而lOW规则则能够达到减小98%的辐射能量,一般情况下3w规则就可以满足我们的要求,除非有特殊要求,否则一般不采用lOW规则。

根据印制电路板的设计规则及一些经验,用PROTEL99SE电路板设计软件设计得如图5.1、5.2的PCB板。电路板的面积为5×11CM,由此可知,用FPGA来实现的数字频率计的PCB板体积小,比传统的频率计的体积小得多。图5.1为印制电路板的顶层3D视图,图5.2为PCB板的底层3D视图。

|鳘|5.1印制电路板顶层

图5.1印制电路板底层

47

幕于FPGA的伞同步数宁频|率计的设计

结论及展望

结论

全同步数字频率计是目自{『精度最高的频率计。在高速时钟随处可见的现代电子系统,有着非常广泛的研究价值。从某种程度上说它是以牺牲时间来换取精确度的,但一般情况下频率计对时间的要求并不高,并且由于电子系统对系统时钟准确度的要求越来越高,因此全同步数字频率计还是有着广泛的应用空间。通过对全同步数字频率计的设计,可以得到以下几个结论:

(1)采用全同步原理测频可以消除±1个计数误差,提高测频精度。

(2)把全同步数字频率计设计在FPGA芯片上,构成了一个典型的SOC系统,对缩小电路板的体积以及缩短设计丌发的周期具有非常重要的意义。

(3)通过对全同步数字频率计的仿真,得到了良好的结果,这对硬件的设计和测试提供了很好的依掘。

(4)本设计在最后没有做好硬件电路进行最后的硬件测试,这是一个很大的遗憾。在后续的研究中应该做好硬件测试,能够与现在市面上的频率计的测试结果进行比较,得到更加科学的验证。

(5)本设计要转化成产品还要更进一步的进行研究,需要设计电源电路和被测信号的波形整形、放大电路以及设计标准稳定的时基信号电路。

(6)出于测量频率的仪器功能一般都比较多,因此,我们完全可以在本设计的基础之上,可以添加测周,测相位差以及与Pc机通讯的功能,使之向多功能方向发展。

展望

EDA(电子设计自动化)是现代电子设计的趋势,VHDL语言则是EDA设计中最为流利的一种高级语言,要掌握现代电子设计的核心技术,就应该学会VHDL语言。其设计简单,不需要详细知道硬件电路的结构,就可以进行丌发。这样可以有更多的人加入到电子行业。其语言通俗易懂,开发容易,从而可以大大缩短产品上市的时间,可以事先用开发软件进行前期仿真,提lj{『发现问题,提Iji『解决问题,投资风险减少,同时由于数字电路都集成在一块芯片上,因此可以大大缩小电子产品的体积。因此从各方面来看,用可编程逻辑器件(FPGA或CPLD)作硬件,用VHDL硬件描述语言作为开发语言,是一种方便快捷、高效、高速、低成本的开发方式。

硕I‘学位论文

现在ALTERA公司又推出了全新的HRADCOPY技术:通过强化EDA工具的设计能力,在保持FPGA开发优势的前提下,引入ASIC的开发流程,从而对ASIC市场形成直接竞争。也就是利用原有的FPGA开发工具,将成功实现于FPGA器件上的系统通过特定的技术直接向ASIC转化,从而克服传统ASIC设计中普遍存在的问题,并且用HARDCOPY技术设计的AsIc一次性投片的成功率近乎100%,即所谓的FPGA向ASIC的无缝转化。而且用ASIC实现后的系统性能将比以自口在HardCopyFPGA上验证的模型提高近50%,而功耗则降低40%。一次性成功率的大幅度提高即意味着设计成本的大幅降低和产品上市速度的大幅提高。因此就其发展趋势看,势必涉及越来越广阔的电子技术及电子设计技术领域。其中包括电子工程、电子信息、通信、航天航空、工业自动化、家电、生物工程等等。而且随着大规模集成电路技术的发展和EDA工具软件功能的不断加强,所涉及的领域还将不断扩大。随着FPGA器件性价比的不断提高,EDA技术将不断地渗透到电子设计的各个领域,逐步进入到家电,高精度仪器仪表,汽车等只常消费行业。下面我对基于FPGA的频率计的设计作一些具体的展望:

(1)采用全同步的频率测量技术与已往的测频技术相比,在测量精度上有了大的提高,这样在一些高精度频率测量的场合可以考虑采用本设计方法具有很大的优势。”(2)本设计采用了高集成度的FPGA芯片,还具有很大的功能扩展空间,这样有利于全同步频率计的升级,这种升级是完全不需要改板的升级,只须修改FPGA

“内部的逻辑功能,大大的降低了频率计的二次丌发费用。

(3)在本设计中,我们为了减少FPGA器件的硬件丌销,在设计乘法器时采用了逐项移位相乘相加的方法来进行设计,但是如果我们对运算速度有很高要求的话,我们完全可以采用组合逻辑乘法器的原理来设计,这样可以提高速度,但是会增加FPGA的硬件丌销。这在高集成度的FPGA器件中是完全可以做到的。

(4)采用FPGA器件来实现高速,高精度,连续测频具有很大的优势,它可以解决采用单片机测频中时基频率(标准频率)过低而影响测频精度的缺点。并且可以实现高速,连续测频技术,采用FPGA器件来实现运算可以节省运算时问,缩短每次测频时I’日J,从而可以比较方便的实现连续测频技术。

(5)对于目前提出的高精度定闸门的测频方法,如果采用单片机来实现,存在着一定的缺点,需要采用Pc机来实现高速运算。但如果采用FPGA芯片来实现,则会很好的解决这个问题,当然基于FPGA的高精度定闸门的测频方法目前还没有进行设计,这也是我在以后的工作中要做的。t

(6)现在对高频率信号频率的测量也已经显得越来越重要,怎样提高被测信号的频宽,对高频信号能够进行准确,快速的测量也是衡量一个频率计的一个很

幕十FPGA的伞I几1步教。,频率计的设计

重要的参数。在传统的单片机测量技术中,其标准频率只能在几十兆Hz左右,因此很难提高测频频宽。而现在的FPGA器件具有更高的标准频率,而且可以设计宽位、高速的乘法器,这样一来,对于高频信号的频率测量技术提供了一个很好的发展平台。

(7)对超高频信号(几百M赫兹一一几吉赫兹)频率的测量也是目|j{『频率测量的一个难以解决的难题。在本设计的基础上,我们可以提出一个解决的方案。在本设计中,测量的最高频率几百M赫兹,但是我们可以在本设计的基础之上,我们可以采用对被测信号先进行硬件分频,然后再进行测量,然后对测量的数掘进行必要的数据处理,这样一来,我们就可以进行几吉赫兹频率的测量。其中存在有两个难题:一是怎样判定被测信号是一个超高频信号以便于启动硬件分频系统:二是怎样实现对被测超高频信号的频率进行还原,然后进行正确的显示。这两个问题在理论上都是可以在FPGA器件上加以实现。但是,怎样进行具体实现这是我们下一阶段要解决的问题。当然,在进行硬件分频时会产生一定得分频误差,这样会影响频率测量精度,这是不可避免的。50

参考文献

[1]求是科技.cPLD/FPGA应用丌发技术与工程实践[M].北京:人民邮电出版

社,2005:33—97

[2]张学庄,

2004:98—145廖翊希.电子仪器与测量[M].长沙:湖南科学技术出版社,

[3]魏西峰.全同步数字频率测量方法的研究[J].现代电子技术,

2005,30(8):76—79

[4]黄智伟.FPGA系统设计与实践[M].北京:电子工业出版社,2005:3-55[5]潘松,黄继业.EDA技术实用教程[M].北京:科学技术出版社,2005:22—175[6]严颂庄,王祝盈,陈小林等.影响相检式多周期同步测频法测量精度因数的

研究[J],湖南大学学报(自然科学版),2003,30(3):5-8

[7]章军,张平,于刚.多周期同步测频测量精度的提高[J].电测与仪表,Jun。

2003。40(450):16—18

[8]张庚辰,秦京华,朱维真等.等精度可变多周期不问断测频方法的研究[J].

仪器仪表学报,2000,21(6):651—653

[9]冯涛,秦永左。数字测频方法的研究[J].长春光学精密机械学院学报,2001

24(1):P38-41

[10]徐成,刘彦,李仁发等.一种全同步数字频率测量方法的研究[J].电子技

术应用,2004,38(12):43—46

[11]杨恒,李爱国,王辉等.FPGA/CPLD最新实用技术指南[M].北京:清华大学出版社,2005

[12]边春远,王志强.MCS-51单片机应用程序丌发实用子程序[M],北京:人民

邮电出版社,2005.9.

[13]阎石.数字电子技术基础[M].北京:高等教育出版社,1998

[14]吴超英.基于CPLD/FPGA技术的数字系统的设计[J].安徽工业大学学报,

2003。20(1):69-一73

[15]武卫华,陈德宏.基于EDA技术的数字频率计芯片化的实现[J].电测与仪

表,2004,41(460):23—26

[16]邵蓉.基于EDA技术的数字系统的数字综合方法的探讨[J].扰顺石油学院

学报,2003,23(1):69—7l

[17]李如春,秦苗.基于FPGA/CPLD的小型片上系统的设计[J].浙江工业大学

学报,2001,29(3):312—315[18]伞景辉,常青.基于FPGA的乘法器实现结果分析与仿真[J].微处理机,

基于FPGA的伞|几1步数。7频率计的设计

2004。(3):3—7

[19]莫琳.基于FPGA的等精度频率计的设计与实现[J].现代电子技术,2004,

30(10):35—37

[20]张兆莉,蔡永泉,王钰.基于FPGA的数字频率计的设计及实现[J].自动

化仪表,2006,27(11):9--Il

[21]朱灿焰.频率精确测量方法研究[J].现代雷达,2004,26(7):54—56

[22]张梦犁,韩国松.基于FPGA的等精度数字频率计的研究与实现[J].商丘职

业技术学院学报,2006,5(2):34—36

[23]谢小东,李良超.基于FPGA的等精度数字频率计设计[J],实验科学与技术,

2005.10.

[24]杨守良.基于FPGA的数字频率计的设计和实现[J].现代电子技术,2005,

(11):123-125

[25]林晓焕,林刚.基于VHDL语言的数字频率计设计[J].西安工程学院学报,

2005,19(3)

[26]郭改枝,基于复杂可编程逻辑器件的数字频率计的设计与实现[J].内蒙古

师范大学学报,2005,34(4):35—37

[27]张霞.数字频率计的VHDL程序设计[J].现代电子技术,2001,30(9):56—57[28]谢海鸿.基于FPGA芯片的数字频率计设计[J].现代电子技术,

2005,30(18):45—47

[29]苟殿栋,徐志军.数字电路设计实用手册[M].北京:电子工业出版社,2003[30]王伟.VerilogHDL程序设计与应用[M].北京:人民邮电出版社,2005[31]汪金爱.刘达EDA技术与FPGA设计应用[J].今冗电子,2004,

(12):73—76.

[32]任良超,会海明.AlteraFLEXIO的配置及实现[J],仪器仪表学报,2005,

(8):262-264

[33]Weizhou,Zongqiang,JianGuoYu.Somenewdevelopmentofprecision

ofthe1995IEEEfrequencymeasurement

internitionaltechniquc[C],preceedingsfrequencycontrol

newsymposium.PP.354—359.1995.measurement[C].[34]Weizhou,Somemethodsorpresiontimeinterval

1997IEEEinternationalfrequencycontrolsymposium.

[35]Wayne

2005Wolf(USA)。FPGA-BasedSystemDesign[M],北京:机械工业出版社,

[36]徐欣,于红旗,易凡,卢启中.基于FPGA的嵌入式系统设计[M],北京:机械工业出版社,2004

[37]PanSongApplicationforegroundofCPLD/FPGAinelectrondesign[J]

Electrontechnologyapply1997,(7):16—2l

some[38]MAAshour+HIsalehAnFPGAinplementationguidefor

ofserial—parallelmultiplierdifferenttypesstructures[J].MicroelectronicsFournal,2000,31(3):161—168

ASSP[J]Electron[39]LUShaoqiangFPGAwillgradualyreplaceASICand

productionworld.200。(9):26—-28

theComplexSoC:Fast,FlexibleDesign[40]ChrisRowen(USA).Engineering

withConfigurableProcessors[M].北京:机械工业出版社,2005

F,GailGray,DesignexpressionandSynthesiSof

Universitypress,2001

MethodforprecisionTimeInterval

Frequency[41]JamesR,AnmstrongVHDL[M]Cambridge:Harvard[42]ZhouWei。eta1.SomeNewMeasurementproceedingsofthe

Control1977IEEEinternationalsymposium。1997,418—42l

堆fFPGA的伞I卅步数宁频率汁的设汁

致谢

本文是在导师何怡刚教授的悉心指导下完成的。导师渊博的知识、丰富的实践经验、严谨的治学态度、雷厉风行的办事风格令我终生难忘,受益非浅。

在攻读硕士学位期问,我还得到了其它众多老师和同学们无私的关怀和帮助,有了他们,我才能顺利完成硕士研究生阶段的学业,并即时完成我的硕士学位论文。

首先,我必须再一次地感澍我的导师何怡刚教授,感谢他在这两年多的工作学习中对我无私的关怀和教诲。感谢他为我提供了大量的实践、学习机会,使我在学习和生活等各方面都得到长足的进步。我从他身上学到的,不仅仅是科学知识,还有更多的做人的道理。

其次,我要感谢我的家人,感谢他们对我一贯的理解和大力支持。生活上,他们无微不至的关怀着我,学习上总是不断激励着我不断上进、勇往直莳。没有他们,就没有我的今天。

最后,我还要衷心的感谢谭永宏,蒋辉平,潘海军等同学,是他们提供了热心的帮助和鼓励并使我的生活变得丰富多彩,学习充满了激情。能成为他们的同学与朋友是我~生的荣幸。

再一次衷心地谢谢大家!

谨以此文献给我的父母、亲人以及所有关心帮助我的人们1

2007年8月于湖南大学

颂f¨擎化论文

附录A:

[1]包本刚攻读学位期间发表的论文及成果基于FPGA器件的FIR滤波器的设计[J].湖南科技学院学

报,2005,V01.26,No.11,67—70.

[2]包本刚基于ICL7107器件的量程自切换的数字电压表的设计[J],.中国仪

器仪表.2007,2..

[3]包本刚,朱湘萍基于FPGA器件的数字电压表的设计[J],电子工程

师,2007,V01.33,P17-18.

[43包本刚基于MSI器件的数字密码锁的设计[J].山西电子技术,2007,10.[53包本刚何怡刚,谭永宏,李晴基于FPGA的全同步数字频率计的设计与

实现[J].测试技术学报(已定稿2008年年初)

[6]包本刚何怡刚,朱湘萍全同步数字频率计的VHDL设计与仿真[J].现代电子技术,2007,30(10):176-178.

摹十FPGA的伞删步数’,频率汁的设计

附录B:VHDL部分源程序

全同步数字频率计部分源程序

本程序创建于2006年9月完成于2007年6月程序员:包本刚

1.1加法器VHDL程序

1ibraryieee:

useieee.stdogic—1164.all:

useieee.stdogic_arith.a11:

useieee.stdogic_unsigned.a11

entityadder28is

generic(dw:integer:=27):

port(

cin:instd—logic:

a:instd—logic—vector(dw一1downto0):b:instd-logic—vector(dw一1downto0):s:outstd—logic—vector(dw一1downto0)cout:outstd—logic

end

rtlofadder28is

signaltemp:std-logic—vector(dwdownto0)signalt1:integerrange0to100000000:signalt2:integerrange0to100000000:signalt3:integerrange0to200000001:tl<=cony—integer(a):t2<=conv—integer(b);t3<_tl+t2+conv—integer(ein):

temp<=cony—std—logicvector(t3,28):

s<=temp(dw一1downto0):一进位输入一进位输出一加法器输入a一加法器输入b一加法器输出sarchitecturebegin

cout<=temp(dw)

end:

1.2减法器VHDL程序

libraryieee:

useieee.std—logic一1164.all:useieee.std_logic—arith.a11:useieee.st以logic—unsigned.all

entltysubber1S

generic(dw:integer:=28):

port(

cin:instd—logic:

a:instd_logicvector(dw一1downto0):b:instd_logic—vector(dW一1downto0)S:outstd-logic—vector(dw一1downto0)cout:outstd—logic

):

endentity:

rtlofsubberiS

signaltemp:std—logic—vector(dwdownto0)signalt1:integerrange0to268435455:signalt2:integerrange0to268435455:signalt3:integerrange0to268435455:begin

tl<=conv—integer(a):

t2<=convinteger(b):

t3<=tl—t2一conv—integer(cin):

temp<=conv_std_logic—vector(t3,29):

s<=temp(dw一1downto0):

cout<=temp(dw):

end:一借位输入~减法器输入b~借位输出~减法器输入a一减法器输出S、architecture

摹十FPGA的牟州步数’,频率计的设计

1.3顶层VHDL源程序

1ibraryieee:

useieee.std—logic一1164.al1:useieee.std.109ic_unsigned.alluseieee.std—logic_arith.a11:entitytopleveliS

generic(dw:integer:=27):

port(

clkO:instd—logic:

clkx:instd—logic:

clks:instd_logic:

cnt9:outstd—logic—vector(3downto0)sg:outstd—logic—vector(6downto0)cnt:outstd—logic—vector(8downto0)dp:outstd—logic:

P:outstd—logic—vector(35downto0)):

end:

architecturetopoftopleveliscomponentcounter30

port(clk,clr,ena:instd_logic:

ov:outstd_logic:

q:outstd-logicvector(26downto0))endcomponent:

componentcontrol

port(clk:instd—logic:

creg:bufferstd—logic:

clr。cp:outstd-logic)

endcomponent:

componentmultn

generic(dw:integer:=27):port(

clk:inst(Llogic:

a:instd_logicvector(dw—ldownto0);b:instd.109icvector(d旷ldownto0):p:outstnlogicvector(2*dw一1downtostart:instd—logic:finished:buffersttlogic:

f:outsttlogic

df:outstd—logic

):

endcomponent:

componentdivider

generic(dw:integer:=27):port(

clk:inst(Llogic:

a.instd—logic_vector(dw*2—1downtoO):一被除数b.instd—logic—vector(dwdownto0):一除数p:outstd_logic—vector(dw*2一ldownto0)~商start:instd—logic:一开始信号finished:bufferstd—logic一结束信号):

endcomponent:

componentbtod

port(clk:instdlogic;

clkO:instd—logic:

hd:instdlogic_vector(29downtoO):bcd:outstd_logic_vector(39downto0)

):

endcomponent:

一

苎±!Q皇堕全型兰墼:兰塑!生塑壁生

signalsignalsignalsignal

qO:std—logic—vector(dw~1qx:std-logic—vector(dw~1

downtodownto

0):0):

downtodowntodownto

mult—qO_a:sttlogic_vector(dw一1

mult_qO—b:std—logic—vector(dw一1

out:std—logic—vector(dw*2—1

0):0):0)

signalmult

signalsignal

divider_a:std-logicvector(dw*2—1divider_b:std—logic—vector(dw

vector(dw

downto

0)

downtodownto

0):0):

signaldivider—bt:std—logic

signalsignal

cinl:std—logiccin2:std—logic

signalsignalsignal

cp:std—logic:一计数使能终止信号clr,clx:std—logic:~计数器清零lock:std—logic:一数值锁存

signalsignal

qO—clkO:std—logic—vector(dw一1

downtodownto

0)0)

qx—clkx:sttlogic—vector(dw-1

slgnalsignalsignal

start

m:std-logic:

finished_m:std-logic:start—d:std-logic:

s1’gnalfinished—d:std—logic:signalsignalsignal

PP:std—logic:ff:std—logic;df:std—logic:

dq:integerrange0to2

signal

signalsignal

qP:std_logic—vector(dw*2—1qq:std-logic_vector(29

downto

0)

downto

0):

60

gnal

gnalppp:std—logic—vector(35downto0)cntt:std-logic—vector(3downto0)

gnala.std_logic—vector(3downto0):

begin

ul:counter30port

U2:counter30port

u3:control

u4:multnportportmap(clk=>clkO,clr=>clr,ena=>cp,ov=>cinl,q2>qO):map(clk=>clkx,clr=>clr,ena=>cp,ov=>cin2,q。>qx):map(clk=>clks,creg=>lock,clr=>clr,cp=>cp):

map(clk=>clkO,a=>mult_qO_a,b=>mult_qO_b,p=>mult_out,start=>clx,finished=>finished_m,f=>ff,df=>df):

u5:dividerport

map(clk=>clkO,a=>divider_a,b=>divider_b,p=>qp,start=>ff,finished2>finishedd):

portu6:btodmap(clk=>finishedd,clkO=>clkO,hd=>qq,bcd2>PPP):

qq<=qp(29

p<=ppp(35downto0):downto0):

process(clr,clkO)

begin

ifclr=’0’thendq<=O;

elsirclkO’eventandclkO=’1'then

ifdq<dq’highthen

dq<=dq+l:

elsedq<=dq;

endif:

endif;

endprocess:

process(dq)

begin

ifdq=lthen

clx<=’1’:

elseclx<=’0’6l

基于FPGA的伞M步数。,频率计的设计

endif:

endprocess

process(10ck)

begin

iflock=’1’andlock’eventthen

qO_clkO<=qO:

qx_clkx<=qx:

endif:

endprocess:

process(clr,mult—qOa,mult—qO—b)

begin

ifclr=’1’andclr’event

multqO—a<=qx—clkx:then

mult—qO』<=”10111i101011110000100000000”endif:

endprocess:

process(df,divider~bt)

begin

ifdr=’1’anddf’eventthen

divider_bt(dw一1downto0)<=q0一clkO(dw一1downto0).divider—bt(dw)<=’0’:

endif:

endprocess:

process(divider—a,divider_b,finished—d,ff)begin

ifff=’1’andff’eventthen

iffinished—d=’1’then

downtodivider—a(dw*2—1

divider_a(dw一1dw)<=mult—out(dw*2—1downtodW)downtoo)<=mult—out(dw一1downto0):

divider_b(dw一1downto0)<=dividerbt(dW一1downto0)divider_b(dw)<=’0’;

endif:

endif:

endprocess:

8进制计数器

process(clkO)

begin

ifclkO=’1’andclkO’eventthen

ifcntt<8then

一cntt<=cntt+1:

elsecntt(=”0000。:

endif;

ifcntt=”0000’thendp<=’1

elsedp<=’0’:

endif;

endif:

cntg<=cntt:

endprocess:

循环描述

~一…一一…一…一一一……一一数码管段选程序process(cntt)

begin

casecnttis

downto

downto

downto

downto

downto

downtowhen”0000”=>a<=ppp(3when”0001’=>a<=ppp(7when’0010”=)a<=ppp(1lwhen’0010):4):8):12)16)20)1’=)a<=ppp(15when’0100”=>a<=ppp(19when’O101’=>a<=ppp(23

摹于FPGA的伞¨步教‘一频率计的I垃计

when’01

when”0110”=>a<=ppp(2711’=>a<=ppp(31downtodownto

downto24)28)32)when’1000’=>a<=ppp(35

whenothers=>null:

endcase:

endprocess:

~……一一~…一一一…一一●…直接描述一-._……一一扫描方式

译码序程process(a,cinl,cin2)

begin

ifcinl=’0’andcin2=’0’then

caseaiS

when”0000”=>sg<=”0111111”;when”0001”=>sg<=”0000110”when”0010”=>sg<=”1011011”;when”0011”=>sg<=”1001111”when”0100”=>sg<=”1100110’:when”0t01”=>sg<=“1101101”when”0110”=>sg<=”1111101”:when”0111”=>sg<=”000011l”when”1000”:>sg<=4lllllll”;when”1001”=>sg<=”1101111”whenothers=>null:

endcase:

elsesg<=’1110001”:

endif:

endprocess;

直接描述

process(cntt)

begin

casecnttiS

when’0000’=>cnt<=’111111110’

when”0001”=>cnt<=”1111111014

when”0010”=>cnt<=”111111011”

when”0011”=>cnt<=。111110111’

.耋三。。...。。。.。。。........一

when’O100”=>cnt<=”1iI10111l”

when”0101”:>cnt<=41i101IiIl”

when”0110”=>cnt<=’110111111”

when”0111”=>cnt<=”101111Iii”

when’i000”=>cnt<=”011lilIii”

whenothers=>nul1:

endcase:

endprocess:end:

基于FPGA的全同步数字频率计的设计

作者:

学位授予单位:包本刚湖南大学

相似文献(10条)

1.期刊论文 曹瑞.CAO Rui EDA工具如何应对FPGA设计中的多重挑战 -半导体技术2007,32(7)

不同领域优化的多平台FPGA以其革命性的能力促使FPGA技术加速进入更多的应用领域.随着器件复杂性的增加,设计人员需要更加精密复杂的工具,定位于FPGA设计的EDA工具也面临着更大的挑战和机遇.指出了EDA工具在FPGA设计中所面临的挑战,通过对Synplicity公司的解决方案和工具的分析,提出EDA工具应对FPGA设计挑战的一般方法和创新方向,并指出EDA工具在面临挑战的同时也将迎来发展机遇.

2.期刊论文 邓志娟.Deng Zhijuan EDA电子仿真技术及其FPGA步进电机细分驱动控制设计 -科技广场2008(8)

EDA技术是电子设计领域的一场革命,成为现代系统设计和电子产品开发的有效工具.本文详细介绍了EDA技术的发展历程,着重分析EDA技术的主要内容及设计流程.通过FPGA步进电机细分驱动控制设计实例仿真过程的具体描述,说明EDA技术大大简化了工控电路的设计,并且降低了成本.

3.期刊论文 蒋昊.李哲英.JIANG HAO.LI ZHEYING 基于多种EDA工具的FPGA设计流程 -微计算机信息2007,23(32) 本文介绍了FPGA的完整设计流程,其中包括电路设计与输入、功能仿真、综合优化、综合后仿真、实现与布局布线、时序仿真、板级仿真与验证、调试与加载配置等主要步骤.并通过一个8-bit RISC CPU的设计实例系统地介绍了利用多种EDA工具进行FPGA协同设计的实现原理及方法.

4.期刊论文 陈新华.范炜琳.王成义.张建立.赵义珂.黄泊 基于FPGA芯片和EDA技术的逻辑分析仪系统设计 -微电子学与计算机2004,21(7)

应用EDA技术和FPGA芯片设计完成了逻辑分析仪,简要介绍了该分析仪中各个模块的设计特点和功能,以及模块选择的方式和根据.

5.期刊论文 梁玉红.黄晓林 基于EDA技术的CPLD/FPGA应用前景 -广东自动化与信息工程2001,22(2)

本文指出基于EDA的CPLD/FPGA的应用和技术推广将是我国未来电子设计技术发展的主要方向。

6.期刊论文 王乐毅.WANG Le-yi DA设计技术与方法(Ⅰ)-EDA方法及其进展 -青岛化工学院学报(自然科学版)2000,21(4)

EDA是现代电子学的标志。本研究对EDA设计方法及其发展进行了综述。

7.期刊论文 章礼宏.范全润.ZHANG Li-hong.FAN Quan-run 基于EDA软件和FPGA的IP核保护技术 -电子设计工程2009,17(3)

随着电路复杂性的增加,越来越多的设计者开始采用拥有知识产权的、设计良好的功能模块来加快系统开发.因此,需要相应的技术手段保护这些功能模块不被非法复制、篡改或窃取.针对FPGA开发中的知识产权保护问题,提出一种结合EDA软件和FPGA的IP(Intellectual Proterty)核保护方法,有效的防止IP核被窃取,以及防止最终在FPGA上实现设计的非法复制.

8.期刊论文 梁秀荣.周剑玲.朱小龙.LIANG Xiu-rong.ZHOU Jian-ling.ZHU Xiao-long 基于EDA软件和FPGA的电子设计 -华北科技学院学报2006,3(1)

采用EDA软件和FPGA可编程逻辑器件进行电子设计,以电子秒表为例,说明设计过程和方法.该方法提高了电子产品的集成度,减少故障率,降低开发成本,缩短开发周期,在电子设计实践教学中采用这一新的设计方法, 对学生电子设计软件的应用能力和创新能力的培养起到了促进作用.

9.期刊论文 卢勇威.LU Yong-wei 基于FPGA的EDA创新实验探讨 -实验室研究与探索2006,25(6)

文章探讨了一个基于FPGA的EDA创新实验.由于传统的使用实验箱进行实验的方法在某些方面存在不足,因此本创新实验提倡完全由学生自己动手设计.详细讨论了EP1K30TC144-3的管脚功能以及该芯片最小系统的构成,还介绍了下载线的原理和电路连接方法.通过本实验不但使学生深刻地理解FPGA器件最小系统的构成和调试技巧还培养了学生的学习积极性和创新精神.

10.期刊论文 柯建伟.周嘉农 多种EDA工具的FPGA协同设计 -今日电子2004(5)

在FPGA开发的各个阶段,市场为我们提供了很多优秀的EDA工具.面对眼花缭乱的EDA工具,如何充分利用各种工具的特点,并规划好各种工具的协同使用,对FPGA开发极其重要.本文将通过开发实例"带顺序选择和奇偶检验的串并数据转换接口"来介绍基于多种EDA工具-Quartusll、FPGA Compilerll、Modelsim-的FPGA协同设计.

本文链接:http://d..cn/Thesis_Y1209343.aspx

下载时间:20xx年12月10日

-

数字频率计课程设计报告

赣南师院物理与电子信息学院数字电路课程设计报告书姓名班级学号时间数字频率计的设计一设计任务和要求1能够测量正弦波三角波锯齿波矩形波…

-

简易数字频率计课程设计报告

摘要在电子技术中频率是最基本的参数之一并且与许多电参量的测量方案测量结果都有十分密切的关系因此频率的测量显得更为重要测量频率的方法…

-

简易数字频率计设计实验报告 季克宇

电子线路课程设计报告第1页共14页电子线路课程设计报告姓名季克宇学号110404130专业通信工程日期20xx1010南京理工大学…

-

数字电路课程设计——数字频率计设计报告

I在电子技术中频率是一个重要参量应用计数法原理制成的数字式频率测量仪器具有精确度高测频范围宽便于实现测量过程自动化等一系列突出特点…

-

简易数字频率计课程设计报告 .

目录第一章概述11数字频率计功能及特点12数字频率计应用意义第二章设计方案21设计指标与要求22设计原理23方案论证第三章数字频率…

-

基于单片机的数字频率计的设计开题报告

题目:基于单片机的数字频率计的设计1.结合课题任务情况,查阅文献资料,撰写1500~20xx字左右的文献综述。单片机又称单片微控制…

- 基于单片机的频率计设计开题报告

-

无线遥控数字电子钟-开题报告

毕业论文设计开题报告题目无线遥控数字电子钟学生姓名韩二虎学号051641055所在院系机械工程学院专业班级测控052班指导教师杨帆…

-

数字频率计开题报告

武汉大学珞珈学院本科生毕业论文设计开题报告毕业论文设计题目数字频率计系统设计系电子信息科学系学号20xx05060姓名一论文选题的…

-

开题报告数字频率计

杭州电子科技大学毕业设计论文开题报告题目学院专业姓名班级学号指导教师数字频率计的设计与实现通信工程学院通信工程孔冬滨120xx41…