�ɱ��������ʵ�鱨��������

20##��ɱ����������

�γ���Ʊ���

1 ������ݸ���

1.1 ���ܸ���:

һ�����м��롢�Ʒ֡���λ�������ӣ������Ӵ�0��ʼ��ʱ������60����Զ����㣬���Ӽ�1������ʱ��ʾ59��59�롣��A7������Ϊϵͳʱ�Ӹ�λ����λ��ȫ����ʾ00 00�����¿�ʼ��ʱ��

1.2 ��������ӿڣ�

NET "clk" LOC = "B8" ; NET "dula[0]" LOC = "L14" ; NET "dula[1]" LOC = "H12" ;

NET "dula[2]" LOC = "N14" ; NET "dula[3]" LOC = "N11" ; NET "dula[4]" LOC = "P12" ;

NET "dula[5]" LOC = "L13" ;NET "dula[6]" LOC = "M12" ; NET "dula[7]" LOC = "N13" ;

NET "rst" LOC = "A7" ;NET "wela[0]" LOC = "F12" ; NET "wela[1]" LOC = "J12" ;

NET "wela[2]" LOC = "M13" ; NET "wela[3]" LOC = "K14" ;

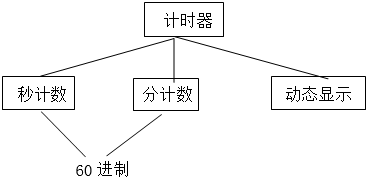

2 ϵͳ��ͼ��ģ�黮��

�����Զ����·ֲ����˼��Ĵ�����ʾ��ͼ����:

3 ��Ա����

1�����𱾿���Ŀ�չ����֯��Э������������밲�����⣬���ҿ���������ϣ�����������ӿڿ����ļ��ı�д��

2����ɷ�Ƶ��ģ��ij����д���Լ����ı���������

3�����ҿ���������ϣ������ӳ��������ģ��ı�д��

4���������ܲ��ֳ���ı�д������ɳ���ķ��漰���ԡ�

4 ��ģ����ϸ���

4.1 ģ��1����Ƶ��

4.1.1 ���ܣ�

��Ƶ�����ܽ���Ƶ����任Ϊ��Ƶ���壬�����ɴ������Լ�����������ɡ�����һ������������һ������Ƶ����N������������2N����Ƶ��������ü���������Ƶ������Ҫ�����������з�Ƶ������ʮ���Ƽ���������ʮ��Ƶ����M���Ƽ�������ΪM��Ƶ���� һ��ʹ�õ�ʯӢ��������Ƶ��Ϊ32768HZ��Ҫ���ø������õ�һ��Ƶ��Ϊ1HZ���������źţ�����Ҫ�÷�Ƶ�����з�Ƶ����Ƶ���ĸ���Ϊ2N= 32768HZ��N =15 ����15����Ƶ���������ͽ�һ��Ƶ��Ϊ32768HZ�����źŽ���Ϊ1HZ�ļ�ʱ�źţ������������˼�ʱ���ɵ�����60��=1���ӣ�60��=1Сʱ��

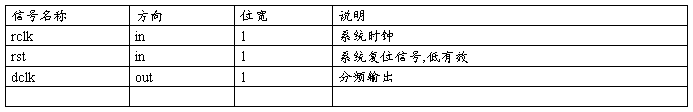

��������ӿڶ���

��1 ģ��1��������ӿڶ���

4.1.2 ģ����ϸ���˼·��

��Ƶ��ģ����verilog����ʵ�ֲ���“����-��ת”�ķ�������ģ����,����������������ijһֵnʱ����źŷ�תһ��,���ѭ��,��������ռ�ձ�Ϊ50%�ķ����ź�,��Ƴ���Ϊ��

module DIV_FRE(

rclk,

dclk,

rst);

input rclk;

input rst;

output dclk;

reg dclk;

parameter DIV=50;

reg[25:0] buff=26'd0;

always @(posedge rclk or posedge rst)

begin

if(rst)

begin

buff��=0;

dclk��=0;

end

else

begin

if(buff==DIV-1)

begin

buff��=0;

dclk��=1;

end

else

begin

dclk��=0;

buff��=buff+1;

end

end

end

Endmodule

4.2 ģ��2��������

4.2.1 ���ܣ�

4.2.2 ��ʱ�������ּ����������������������仯��Ƶ�ʺ�1Hzʱ���źŵ�Ƶ����һ���ġ���ʱ�����еĹ������м���ʱ��ڵ�����Ҫ�ر�ע��ģ�59�롢59��59�룬������ʱ�̽��������λ��59��59�����ʱ��ʱ�佫����㣬ֻҪע���⼸��ʱ�̵��жϲ���ȡ��Ӧ�Ĵ�ʩ�����������ļ�����

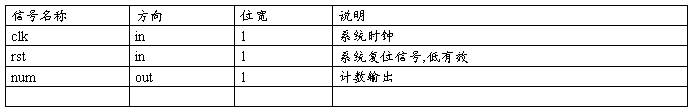

��2 ģ��2��������ӿڶ���

4.2.3 ģ����ϸ���˼·��

������м�ʱ��ģ����ȫ����verilog��������,��ʱ���Ļ���ԭ������������ģ60������,��������,ͬʱ����һ��ʱ��ͳһ���ơ���������£�

module counter_num(

clk,

num,

rst);

input clk;

input rst;

output[3:0] num;

reg[3:0] num=4'd0;

parameter COUNTER=10;

initial

begin

num=4'd0;

end

always@ (posedge clk or posedge rst)

begin

if(rst)

begin

num��=4'd0;

end

else

begin

if(num==COUNTER-1)

num��=4'd0;

else

num��=num+1;

end

end

Endmodule

4.3 ģ��3�������

4.3.1 ���ܣ�

��̬��ʾʱ�����ݣ�ǰ��λ��ʾ�֣�����λ��ʾ�롣

4.3.2 ���˼·��

��̬��ʾ4λ����ʱ����Ҫһ��4ѡ1����ѡ������һ��16ѡ4����ѡ��������һ��7����ʾ������Э��������4ѡ1����ѡ������������ѡ�����������ܣ�16ѡ4����ѡ������������ѡ���Ӧ�����Ӧ����������ݣ�7����ʾ�������������Ƕ�BCD��������룬�����������ʾ��

��Ϊ���Ʋ��ֺͼ������֡�

����ģ�飺

module digit_num_fluid_display_4bit(

clk,

num0,

num1,

num2,

num3,

wela,

dula,

rst );

input clk;

input rst;

input[3:0] num0;

input[3:0] num1;

input[3:0] num2;

input[3:0] num3;

output[3:0] wela;

output[7:0] dula;

wire[3:0] num;

reg[3:0] num_buff;

wire[1:0] pos;

reg[1:0] pos_buff;

reg[1:0] i=2'b0;

assign num=num_buff;

assign pos=pos_buff;

digit_led_display_1bit led_display (

.clk(clk),

.num(num),

.pos(pos),

.dula(dula),

.wela(wela) );

always@(posedge clk or posedge rst)

begin

if(rst)

begin

i��=2'b00;

pos_buff��=2'b00;

num_buff��=0;

end

else

begin

case(i)

2'b00:

begin

pos_buff��=2'b00;

num_buff��=num0;

end

2'b01:

begin

pos_buff��=2'b01;

num_buff��=num1;

end

2'b10:

begin

pos_buff��=2'b10;

num_buff��=num2;

end

2'b11:

begin

pos_buff��=2'b11;

num_buff��=num3;

end

endcase

i��=i+1;

end

end

endmodule

����ģ�飺

module digit_led_display_1bit( //display digit led 1bit

clk, //clk of refresh

num, //the num to display

pos, //the position

dula, //duan bianma

wela);

input clk;

input[3:0] num;

input[1:0] pos;

output[7:0] dula;

output[3:0] wela;

reg[7:0] dula=8'b1111_1111;

reg[3:0] wela=4'b1111;

parameter[7:0] num_0=8'b1100_0000,

num_1=8'b1111_1001,

num_2=8'b1010_0100,

num_3=8'b1011_0000,

num_4=8'b1001_1001,

num_5=8'b1001_0010,

num_6=8'b1000_0010,

num_7=8'b1111_1000,

num_8=8'b1000_0000,

num_9=8'b1001_0000 ;

always@(posedge clk)

begin

case(pos)

2'b00: wela��=4'b1110;

2'b01: wela��=4'b1101;

2'b10: wela��=4'b1011;

2'b11: wela��=4'b0111;

endcase

case(num)

4'b0000: dula��=num_0;

4'b0001: dula��=num_1;

4'b0010: dula��=num_2;

4'b0011: dula��=num_3;

4'b0100: dula��=num_4;

4'b0101: dula��=num_5;

4'b0110: dula��=num_6;

4'b0111: dula��=num_7;

4'b1000: dula��=num_8;

4'b1001: dula��=num_9;

endcase

end

Endmodule

5 ��������Լ�ʵ������

�����ļ���

module testclock;

// Inputs

reg clk;

reg rst;

// Outputs

wire [7:0] dula;

wire [3:0] wela;

// Instantiate the Unit Under Test (UUT)

clock uut (

.clk(clk),

.dula(dula),

.wela(wela),

.rst(rst));

initial begin

// Initialize Inputs

clk = 0;

rst = 1;

// Wait 100 ns for global reset to finish

#100;

rst = 1'b0;

// Add stimulus here

end

always #5 clk = ~clk;

endmodule

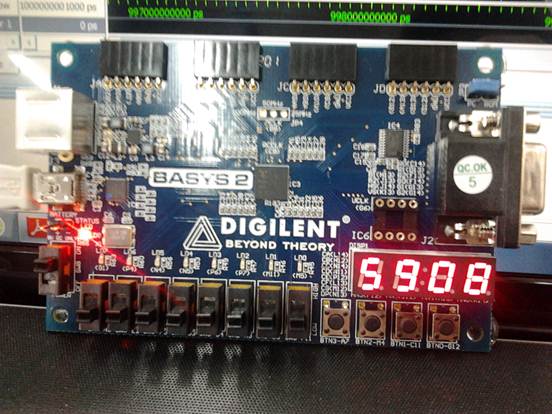

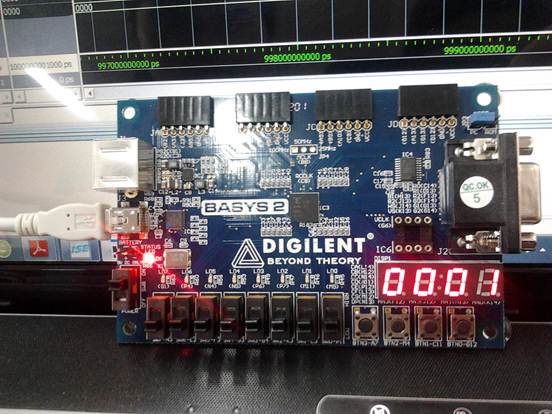

����ʱ��ͼ��

ʵ������

��ʵ�������ʾ����:

59��08�룺

0��1�룺

18��04�룺

18��04�룺

6 �γ�����ܽἰ����ĵ�

ͨ��������ƣ�ѧϰ��FPGA��֪ʶ����FPGA��Ӧ������һ������ʶ��������Ƶ���Ҫ�����ͳɹ�����

�� 1����ѧϰ��verilong���ԵĻ����ϣ��ܵ�����verilong���Խ��е�·��ơ�

2�������Զ����µ����˼��,�Լ�ʱ����������ģ����зֽ���ơ�

3�����з�����֤������ģ�鹦�ܵ���ȷ�ԡ�

4��������ģ�����ӣ����һ��ϵͳ�����ڲ��ϵ����з������⣬����ʱ�����

5����ʵ������γɼ�ʱ����������Ʒ��

�����ĵã�

1��

�ڴ˴�ʵ��Ĺ�������Ҳ�й������в�̫������˵ĵط��������Ҳ�û�����٣������������������Լ�Ѱ��ʧ�ܵ�ԭ����ϸ�ļ����������ͬѧ�������ʦ������һ�������Ҷ�FPGA���������˸���һ���ļ��⣬ �Һ��ҵ���Ա�ֹ���������������Լ���ģ�飬����ѧϰ�����ߡ��������Լ��������Ժ��ʵ�������ѧ��������֪ʶ����Ϊһ��ȫ�淢չ��ѧ����ѧ����

2��

ͨ���μ����ʵ�飬��ѧ���˺ܶණ����������ͨ������ʦ�����������鱾������ȶ�������ѧϰ��FPGA��֪ʶ����ѧϰ�Ĺ����У��Ҽ���ᵽ��ѧϰ����Ȥ��������˺����������������˶������������¹����з��ֵ�����Ҫ�侲��˼������ҪäĿ�Ľ��С��������ƹ��������õ�����ᣬ�ڹ�ȥ��û�й��ģ����鱾����Ҳ�����ҵ��ġ����Ժ�Ŭ����ѧϰ�ⷽ���֪ʶ��

3��

��ѧϰFPGA�����������У��ҽ������FPGAѧϰ����Ȥ����������ʱҪ���������������취�����Ҫ������ϵͳ����бȽ�ȫ��İ��գ���Ĵ������ڴ桢��������DSP�ȣ������ؿ��Լ���֪ʶ�棬�������ֵ�·������ʱ��ϵͳ����·���շ��漰ϵͳ��Ƶȡ� ��Ͼ�����Ŀ������ƿ���Ӧ�ã�����������һ����ȷ�Ľ����������Ŵ�Ӳ���ײ������һЩ��������ơ��ද�֣�����ʵ�����顣����óɹ��ߵľ��飬�ؿ��Լ�����Ұ��ͨ�����絽����EDA��̳���м�����ƽ���������Լ���

4��

ͨ�������ѧϰ�ɱ�������������˽���һЩ�����ص㣺FPGA�ṩ����ߵ����ܶȡ���ḻ�����Ժ���ߵ����ܡ����˽�����Ļ���ʹ�÷�����ѧ������ϰ������߱༭һЩ�ij�����ͨ�������������з��档ͬʱ��ͨ��ѧϰFPGA�����γ���Ӳ�����˼�룬��Ȼ����Verilog���Բ��Ǻܶ������������Ժ��������Ϥ�ġ������������ѧ�ߣ�һ��Ҫ�ද�֣�����ϰ������档��֮��FPGA���Ҵ�����˼���ϵ���������������ġ��Ҿ����Ժ�Ҫ�ú�ѧϰ��

-

�ɱ�̿�����ʵ�鱨��

�㽭�Ƽ�ѧԺ��е����������ѧԺ�㽭�Ƽ�ѧԺʵ�鱨�����ϵͳʵ��ɱ�̿�������Ŀ���Զ�����װ��ѧԺ��еѧԺרҵ��е������켰���Զ�����

-

�ɱ�̿�����Ӧ�ü���ʵ�鱨��

�ɱ�̿�����Ӧ�ü���ʵ�鱨��ѧ��ѧָ�����������ŵ���ʦ��20xx��11ʵ��һS7200PLC�������ʹ��ʵ��1ʵ��Ŀ����ϤSTEP��

- �ɱ�̿����������γ���Ʊ���

- �ɱ�̼����������ԭ����Ӧ�� ʵ�鱨��

- �ɱ�̿�����ʵ�鱨��

-

��һ��ܽ�

����һ�������ܽ�20xx��x��x�գ��������ģ��ݷ�ͳ�����ƽ��˾ֵ����һ�����Ͷ��ڡ�����֮�ʣ��ڹ�˾�쵼�Ĵ���֧�ֺ����£�ͨ��

- �����ֹ����ܽ�(�����������С����չ����ܽ�)

- ����Ͻ��������ܽ�20xx.7

-

�����Ṥ���ܽ�

�ܼ���᳹��Դ�е�5�ε����ᾫ�����ܽ�����й���Դ��ί������������������Դ�е���ε����ᾫ��ѧϰ�����᳹��Ľ���֪ͨ������ί����

-

����һ,���ھ�ҵ,�Ϲ������Ƚ�ģ���¼�������ܽ�

�����ֵ��Ϲ���������20xx�ꡰ����һ���ھ�ҵ�Ϲ������Ƚ������¼�����ᡱ��ܽ�Ϊӭ����һ�Ͷ��ڣ�ͬʱΪ�㷺�����Ƚ����ͣ��ƶ�ȫ��