篇一 :数字逻辑电路课程设计实验报告

数字逻辑电路课程设计

---------多功能数字时钟

班级:信息安全1002

姓名:潘祥熙

学号:3100604048

指导老师:袁晓云

时间:20##-6-25

目录

【封面】---------------------------------------------------------------------------- -1-

【目录】----------------------------------------------------------------------------- -2-

…… …… 余下全文

篇二 :数字逻辑电路实验报告

数字逻辑电路实验报告

——计数器设计与应用

学院:电 信 学 院

班级:电子72班

姓名:冯天宇

学号:07051042

日期:20##年12月31日

一、实验目的:

1.全面、系统的认识与提高《数字逻辑》课程的学习。

2.熟悉和掌握EDA软件(Quartus II 6.0)设计调试电路的方法。

3.通过实验,提高运用数字逻辑电路解决实际问题的能力,并使学生更深入的理解所学知识 。

4. 用D触发器设计同步十六进制加法计数器。

5. 用74LS163(同步清零)设计一个六十进制计数器。

6.用74LS163或74LS190设计24小时制计时器。

二、设计电路及说明:

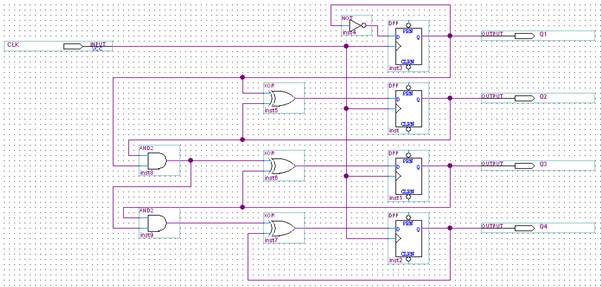

1. 用D触发器设计同步十六进制加法计数器。

电路如下:

所用器件:2个或门,3个异或门,1个非门,4个D触发器。

同步计数器中,所有触发器的时钟输入端均接受统一计数脉冲并同时产生进位信号,进位信号需要用控制门加以控制。

图中:D1=/Q1 D2=Q1+Q2 D3=(Q2·Q1) +Q3 D4=(Q3·Q2·Q1) +Q4

…… …… 余下全文

篇三 :数字逻辑电路实验报告

数字逻辑电路实验报告

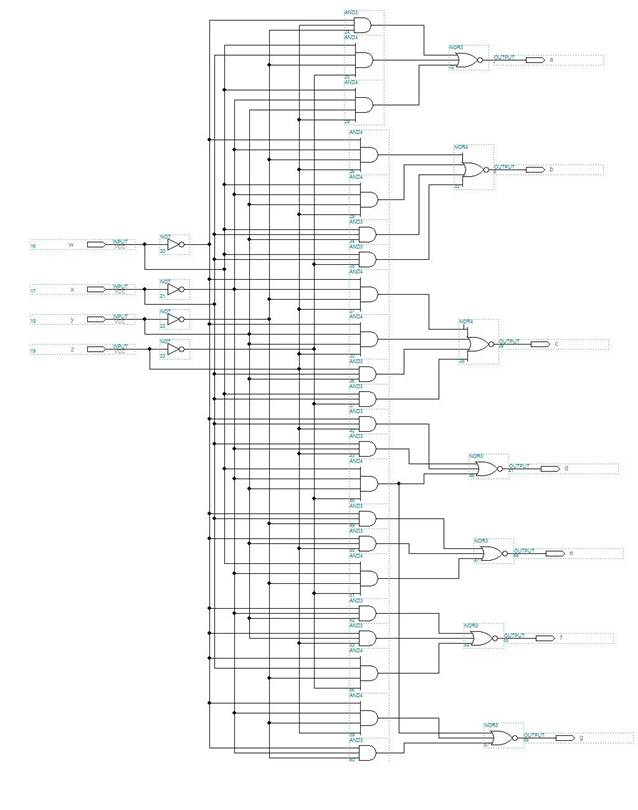

实验二:16进制译码器

原理图:

GAL方程:

PLD16V8

BASIC GATES

2009.04.16

LQY USTC V0.1

W X Y Z NC NC NC NC NC GND

NC A B C D E F G NC VCC

/A=/W*/X*/Y*Z+/W*X*/Y*/Z+W*/X*Y*Z+W*X*/Y*Z/

/B=/W*/X*/Y*Z+/W*X*/Y*Z+/W*X*Y*/Z+W*/X*Y*Z+W*X*/Y*/Z+W*X*Y*/Z

/C=/W*/X*/Y*Z+/W*/X*Y*/Z+W*X*/Y*/Z+W*X*Y*/Z+W*X*Y*Z

/D=/W*/X*/Y*Z+/W*X*/Y*/Z+/W*X*Y*Z+W*/X*Y*/Z+W*X*Y*Z

/E=/W*/X*Y*Z+/W*X*/Y*/Z+/W*X*/Y*Z+/W*X*Y*Z+W*/X*/Y*Z

/F=/W*/X*Y*/Z+/W*/X*Y*Z+/W*X*Y*Z+W*X*/Y*Z

/G=/W*/X*/Y*Z+/W*X*Y*Z+W*X*/Y*/Z+/W*/X*/Y*/Z

DESCRIPTION

…… …… 余下全文

篇四 :数字逻辑电路实验报告模板

《数字逻辑电路》实验报告

第次实验:

姓名:

学号:

级系班

邮箱:

时间:

正文(由下面八项内容评定每次实验报告成绩)

一、 实验目的

本次实验预期要学习到的知识、方法等

二、实验原理(背景知识)

本次实验需要的理论知识背景、实验环境和工具等前期准备知识,预习时完成的引导性实验内容一般在此有所体现。

三、 实验器材/环境

本次实验中使用的硬件器材和软件环境

四、 实验设计思路(验收实验)

验收实验的设计流程图/卡诺图/真值表/代码等或其他

五、 实验过程(验收实验的过程)

充分截图,详细说明实验过程步骤等

六、 实验结果

简单介绍本次实验完成的工作,学到的知识等。

七、 实验中遇到的问题及解决方案

请将已经解决的问题写在这里,没有解决的问题也可以保留在这里,但是可能不能立即得到回答,没有得到回答的问题请在下一次课时向老师和助教当面提问。

八、 实验的启示/意见和建议

1 对本课程或本次实验的意见建议等,如:实验内容难度,实验时间安排,如何提高实验效果等。

2 对本次实验内容你有没有让同学更有兴趣的建议,或者如何才能让你对本次实验更有兴趣?

…… …… 余下全文

篇五 :数字逻辑电路实验报告

学院:计算机科学与通信工程

专业:

姓名:

学号:

指导老师:

多功能数字钟

一、设计任务及要求

(1)拥有正常的时、分、秒计时功能。

(2)能利用实验板上的按键实现校时、校分及清零功能。

(3)能利用实验板上的扬声器做整点报时。

(4)闹钟功能

(5)在MAXPLUS II 中采用层次化设计方法进行设计。

(6)在完成全部电路设计后在实验板上下载,验证设计课题的正确性。

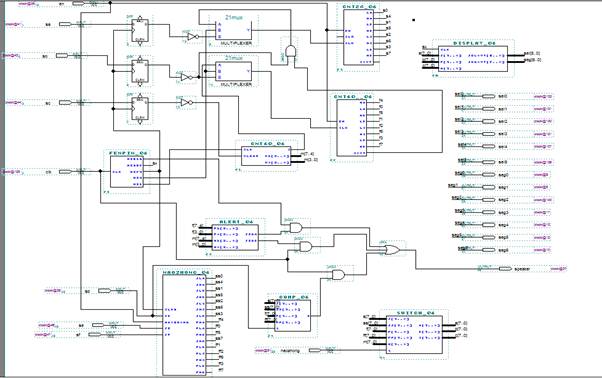

二、多功能数字钟的总体设计和顶层原理图

作为根据总体设计框图,可以将整个系统分为六个模块来实现,分别是计时模块、校时模块、整点报时模块、分频模块、动态显示模块及闹钟模块。

(1)计时模块

该模块使用74LS160构成的一个二十四进制和两个六十进制计数器级联,构成数字钟的基本框架。二十四进制计数器用于计时,六十进制计数器用于计分和秒。只要给秒计数器一个1HZ的时钟脉冲,则可以进行正常计时。分计数器以秒计数器的进位作为计数脉冲。

用两个74160连成24进制的计数器,原图及生成的器件如下:

用两个74160连成的60进制计数器,原图及生成的器件如下:

…… …… 余下全文

篇六 :哈工大 数字逻辑电路与系统实验报告

Harbin Institute of Technology

数字逻辑电路与系统

课程名称: 数字逻辑电路与系统

院 系: 电子与信息工程学院

班 级:

姓 名:

学 号:

教 师: 吴芝路

…… …… 余下全文

篇七 :大连海事大学数字逻辑电路课程设计实验总结报告

数字逻辑电路课程设计实验总结报告 题目一:用J-K触发器设计13进制加法计数器

一、设计过程:参见设计实验报告(真值表,卡诺图)。 二、逻辑电路图:

三、电路图描述:

4个J-K触发器同步接法,每一位J-K触发器的输出端经与非门与灯泡连接(具体c参见设计报告卡诺图下表达式),4个小灯泡代表4位2进制数,左边为高位,右边为低位,小灯泡的亮、灭分别代表“1”,“0”。 四、实验结果:

小灯泡由“灭灭灭亮”依次到“亮灭亮灭”,然后到“灭灭灭灭”,代表“0001”依次累加到“1010”然后清零为“0000”,实现0~12,模13加法计数器。

题目二:用74LS194实现M=10序列为1100110101

一、设计过程:参见设计实验报告。 二、逻辑电路图:

由74LS194双向移位寄存器产生M=10的1100110101。由Q3,Q2,Q1,Q0代表194四位输出端。灯的亮灭代表10,最右边的灯代表F,即代表所产生的序列。 四、实验结果

Q3,Q2,Q1,Q0从“1100”到“1110”成一循环,F的值与之依次对应。参见设计报告真值表。

题目三:用74LS163设计0~98以内的数显电路。

…… …… 余下全文

篇八 :哈工大电信学院数字逻辑电路实验报告

数字逻辑电路与系统

上机实验报告

院系: 电信学院

班级: 1205102班 学号: 1120510213 姓名:

实验一 组合逻辑电路的设计与仿真

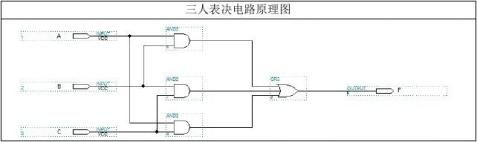

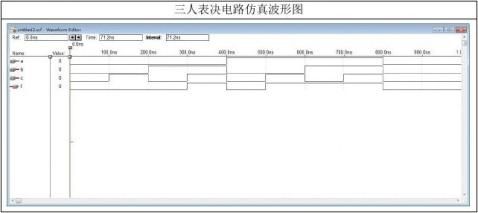

2.2三人表决电路实验

2.2.4 实验步骤

1. 打开MAXPLUS II, 新建一个原理图文件,命名为EXP2_2.gdf。

制输入信号A、B、C的波形(真值表中的每种输入情况均需出现)。

4. 运行仿真器得到输出信号F

的波形,将完整的仿真波形图(包括全部输入输

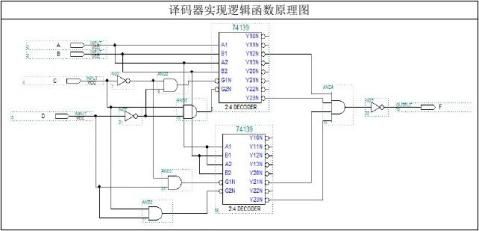

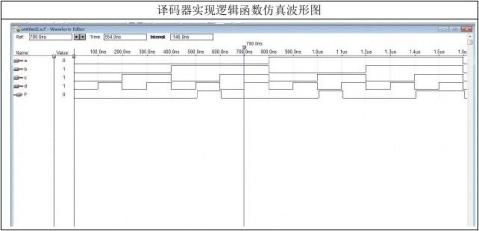

2.3 译码器实验

2.3.4 实验步骤

1. 打开MAXPLUS II, 新建一个原理图文件,命名为EXP2_3.gdf。

制输入信号A、B、C、D的波形(每种输入情况均需出现)。

4. 运行仿真器得到输出信号F

的波形,将完整的仿真波形图(包括全部输入输

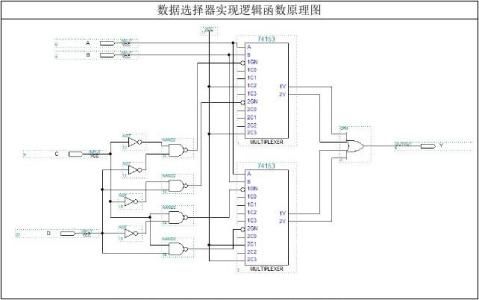

2.4 数据选择器实验

2.4.4 实验步骤

1. 打开MAXPLUS II, 新建一个原理图文件,命名为EXP2_4.gdf。

3. 新建一个波形仿真文件,命名为EXP2_4.scf,加入所有输入输出信号,并绘制输入信号A、B、C、D的波形(每种输入情况均需出现)。

…… …… 余下全文