篇一 :频率计实验报告

频率计实验报告

一, 实验目的

1. 应用AT89S52单片机、单片机的I/O端口外扩驱动器74HC573和74HC138、LED数码管动态显示等实现对外部信号频率进行准确计数的设计。

二,实验要求

A.基本要求:

使用单片机的定时器/计数器功能,设计频率测量装置。

(1)当被测频率fx<100Hz时,采用测周法,显示频率XXX.XXX;当被测频率fx>100Hz时,采用测频法,显示频率XXXXXX。

(2)利用键盘分段测量和自动分段测量。

(3)完成单脉冲测量,输入脉冲宽度范围是100µs-0.1s。

B.扩展部分:

三,实验基本原理

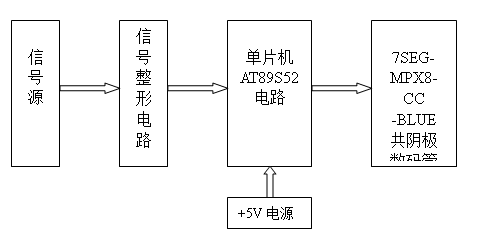

以单片机AT89S52为核心,利用单片机AT89S52的计数/定时器(T1和T0)的功能来实现频率的计数,并且利用单片机的动态扫描把测出的数据送到数字显示电路显示。利用7SEG-MPX8-CC-BLUE共阴极数码管,显示电路共由六位共阴极数码管组成,总体原理框图如图1.1所示。

图1.1 总体设计框图

测频原理

测量频率有测周法和测频法两种。如图2.2和图2.3所示

图1.2测周法 图1.3测频法

…… …… 余下全文

篇二 :数字频率计实验报告

大连理工大学城市学院

数字电路与系统课程设计

设计题目:数字频率计

学 院:电子与自动化学院

专 业: 自动化

学 生: 揣智涵

同 组 人: 王晓宁 周英茹

指导教师: 于海霞

完成日期: 20##年3月26日

…… …… 余下全文

篇三 :频率计设计实验报告

频率计设计实验报告

智能0901

2009010993

周红蕊

一、 设计任务

设计一个频率计电路,要求有4位十进制数码显示,可测量函数发生器输出的信号频率。

1. 可测量9.999KHZ以内的频率并显示。

2. 4位数的任意脉冲计数和显示。

3. 将灵敏度从100mv提高到5mv。

二、技术要求

1. 电源电压: +5V。

2. 输入信号幅度范围: 5mv~10 V。

3. 信号输入方式: 交流输入。

4. 输入信号波形要求:任意波形周期信号、任意波形脉冲信号。

三、设计器材及仪器

1.晶体振荡器。

…… …… 余下全文

篇四 :数字频率计实验报告 20xx年

20##年电子技术实验

实验报告

频率计

一、概述

数字频率计是使用领域非常广泛的测量仪器,在计算机、通讯设备、音频视频等科研生产领域不可缺少。通过十进制数字显示被测信号频率,具有测量迅速,精度高,显示直观等诸多优点。

本实验中,我们使用VHDL开发FPGA的一般流程,采用频率计开发的基本原理和相应的测量方案,在FPGA实验开发板进行数字频率计的设计和实现。

数字频率计是数字电路中的一个典型应用,随着复杂可编程逻辑器件(CPLD)的广泛应用,以EDA工具作为开发手段,运用VHDL语言,将使整个系统大大简化,提高整体的性能和可靠性。本次的频率计设计主要是顶层设计,通过各个模块综合使用,学习常用的数字系统设计方法。采用VDHL编程设计实现的数字频率计,除被测信号的整形部分、键输入部分以外,其余全部在一片FPGA芯片上实现,整个系统非常精简,而且具有灵活的现场可更改性。在不更改硬件电路的基础上,对系统进行各种改进还可以进一步提高系统的性能。该数字频率计具有高速、精确、可靠、抗干扰性强和现场可编程等优点。

本实验,我采用硬件描述语言VHDL,在软件开发平台ISE上完成,该设计的频率计能准确的测量频率在10Hz到100MHz之间的信号。使用ModelSim仿真软件对VHDL程序做了仿真,并完成了综合布局布线,最终下载到FPGA上。

…… …… 余下全文

篇五 :频率计实验报告_20xx011014

数字逻辑与处理器基础

实验三 频率计

实验报告

实验目的:

掌握频率计的原理和设计方法。

实验工具:

1 Verilog语言

2 Quartus II 9.0

3 DE2实验板

实验设计:

1 总体思路以及模块总述

设计的基本思路是按照实验指导书上给出的原理图划分模块。

① 待测信号产生模块signalinput.v:由指导书给出,用于产生待测信号sigin;

② 1Hz时钟产生模块clk_1hz.v:通过实验板50MHz产生1Hz时钟clk_1hz;

③ 控制信号产生模块control.v:通过1Hz时钟,产生频率计所需的使能信号en,同步清零信号reset,锁存信号la,生成一个3秒钟的频率计数周期;

④ 十分频模块div_10.v:若量程选择信号sw_2为高电平,则待测信号需进行十分频;

⑤ 计数器模块counter.v:频率计的核心部分,包括四位十进制计数器,以及对应七段译码器的译码器。这里我把实验指导书中的译码模块整合在了里面,原因是认为在这个设计中单做一个译码模块意义不大,整合在里面翻倒方便一些;

…… …… 余下全文

篇七 :四位数字频率计实验报告

数字逻辑电路大型实验报告

姓 名

指导教师

专业班级

学 院 信息工程学院

提交日期

一、实验目的

学习用FPGA实现数字系统的方法

二、实验内容

1.FPGA, Quartus II 和VHDL使用练习

…… …… 余下全文