实验报告的书写格式

实验报告的书写是一项重要的基本技能训练。它不仅是对每次实验的总结,更重要的是它可以初步地培养和训练学生的逻辑归纳能力、综合分析能力和文字表达能力,是科学论文写作的基础。因此,参加实验的每位学生,均应及时认真地书写实验报告。要求内容实事求是,分析全面具体,文字简练通顺,誊写清楚整洁。

实验报告内容与格式

(一) 实验名称

要用最简练的语言反映实验的内容。如验证某程序、定律、算法,可写成“验证×××”;分析×××。

(二) 所属课程名称

(三)学生姓名、学号、及合作者

(四) 实验日期和地点(年、月、日)

(五) 实验目的

目的要明确,在理论上验证定理、公式、算法,并使实验者获得深刻和系统的理解,在实践上,掌握使用实验设备的技能技巧和程序的调试方法。一般需说明是验证型实验还是设计型实验,是创新型实验还是综合型实验。

(六) 实验内容

这是实验报告极其重要的内容。要抓住重点,可以从理论和实践两个方面考虑。这部分要写明依据何种原理、定律算法、或操作方法进行实验。详细理论计算过程.

(七) 实验环境

实验用的软硬件环境(配置)。

硬件:QTH-2008PC嵌入式32位微机原理与接口技术实验仪。

软件:QTHPCI集成操作软件。

(八) 实验步骤

只写主要操作步骤,不要照抄实习指导,要简明扼要。还应该画出实验流程图(实验装置的结构示意图),再配以相应的文字说明,这样既可以节省许多文字说明,又能使实验报告简明扼要,清楚明白。

(九) 实验结果

实验现象的描述,实验数据的处理等。原始资料应附在本次实验主要操作者的实验报告上,同组的合作者要复制原始资料。

对于实验结果的表述,一般有三种方法:

1. 文字叙述: 根据实验目的将原始资料系统化、条理化,用准确的专业术语客观地描述实验现象和结果,要有时间顺序以及各项指标在时间上的关系。

2. 图表: 用表格或坐标图的方式使实验结果突出、清晰,便于相互比较,尤其适合于分组较多,且各组观察指标一致的实验,使组间异同一目了然。每一图表应有表目和计量单位,应说明一定的中心问题。

3. 曲线图应用记录仪器描记出的曲线图,这些指标的变化趋势形象生动、直观明了。

在实验报告中,可任选其中一种或几种方法并用,以获得最佳效果。

(十) 讨论

根据相关的理论知识对所得到的实验结果进行解释和分析。如果所得到的实验结果和预期的结果一致,那么它可以验证什么理论?实验结果有什么意义?说明了什么问题?这些是实验报告应该讨论的。但是,不能用已知的理论或生活经验硬套在实验结果上;更不能由于所得到的实验结果与预期的结果或理论不符而随意取舍甚至修改实验结果,这时应该分析其异常的可能原因。如果本次实验失败了,应找出失败的原因及以后实验应注意的事项。不要简单地复述课本上的理论而缺乏自己主动思考的内容。

另外,也可以写一些本次实验的心得以及提出一些问题或建议等。

(十一) 结论

结论不是具体实验结果的再次罗列,也不是对今后研究的展望,而是针对这一实验所能验证的概念、原则或理论的简明总结,是从实验结果中归纳出的一般性、概括性的判断,要简练、准确、严谨、客观。

(十二) 参考资料

详细列举在实验中所用到的参考资料.

格式:

作者 书名 出版社 年代 页数

作者 篇名 期刊名 年代

第二篇:实验报告的撰写格式及样本

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity CNT16 is

port( CLK,RST,EN: in std_logic;

CQ: OUT std_logic_vector(3 downto 0);

COUT:OUT std_logic);

end CNT16;

architecture behav of CNT16 is

begin

process(CLK,RST,EN)

VARIABLE CQI:std_logic_vector(3 downto 0);

begin

if RST='1' then CQI:=(others=>'0');

elsif CLK'event and CLK='1' then

if EN='1'then

if CQI<15 THEN CQI:=CQI+1;

else CQI:=(others=>'0');

end if;

end if;

end if;

if CQI=15 THEN COUT<='1';

else COUT<='0';

end if;

CQ<=CQI;

end process;

end architecture behav;

实验报告的格式:

实 验 名 称

一、实验目的

二、实验内容

三、实验条件

(1)、开发软件 Max+Plus II 或者 Quartus II

(2)、实验设备 GW-48系列EDA实验开发系统

(3)、所用芯片 Altera公司ACEX1K系列的EP1K30TC144-3芯片

四、实验设计

(1)、系统的原理框图

(2)、原理图/VHDL源程序

(3)、波形及仿真文件

(4)、管脚锁定文件(管脚锁定情况,在rpt文件里可以看到)

五、实验结果及总结

(1)、系统仿真情况

(2)、硬件验证情况

(3)、实验过程中出现的问题及解决的办法

注意:统一用五号宋体,行间距为1.5倍。

实验报告样本:

姓名: 李某某 学号: 06005

数字频率计设计实验

一、 实验目的

1. 熟悉Max+PlusⅡ和GW-48型EDA开发系统的使用

2. 掌握具有一定复杂程度的综合电路设计

二、 实验内容

设计并调试好4位十进制数字频率计,并用EDA实验开发系统进行硬件验证。

三、 实验条件

(1)、开发软件 Max+Plus II 或者 Quartus II

(2)、实验设备 GW-48系列EDA实验开发系统

(3)、所用芯片 Altera公司ACEX1K系列的EP1K30TC144-3芯片

四、 实验设计

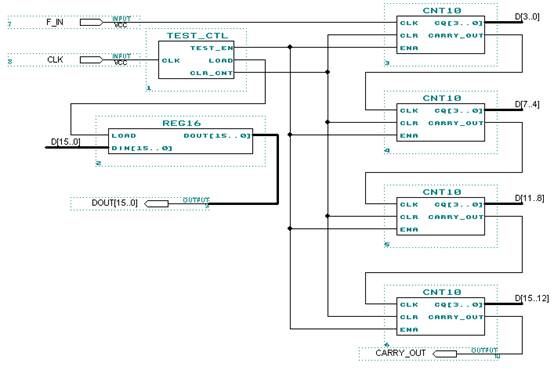

(1)、系统的原理框图

图1 系统的总原理框图

(2)、VHDL源程序及时序仿真

文件一:TEST_CTL.VHD测频控制信号发生器:产生1S脉宽的周期信号和锁存、清零信号

---------------------------------------------------------------------------

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY TEST_CTL IS

PORT(

CLK : IN STD_LOGIC; --1hZ的输入时钟

TEST_EN : OUT STD_LOGIC; --计数时钟使能,脉宽为1S

LOAD : OUT STD_LOGIC; --锁存信号

CLR_CNT : OUT STD_LOGIC); --清零信号

END TEST_CTL;

…………

ELSE CLR_CNT <= '0';

END IF;

END PROCESS;

TEST_EN <= DIV2_CLK;

LOAD <= NOT DIV2_CLK;

END a;

-------------------------------------------------------------------------

图2 TEST_CTL.VHD的时序仿真波形图

文件二:CNT10.VHD--带有时钟使能异步清零的十进制计数器

-------------------------------------------------------------------------

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY IS

PORT(

CLK : IN STD_LOGIC; --计数时钟信号

…………

END a;

--------------------------------------------------------------------

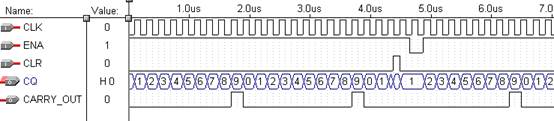

图3 cnt10.vhd的时序仿真波形图

文件三:REG16.VHD--16位锁存器,好处:显示的数据稳定,不会由于周期性的清零信号而不断的闪烁。

------------------------------------------------------------------

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY REG16 IS

PORT(

LOAD : IN STD_LOGIC; --锁存允许信号

DIN : IN STD_LOGIC_VECTOR(15 DOWNTO 0);

DOUT : OUT STD_LOGIC_VECTOR(15 DOWNTO 0));

END REG16;

……

END PROCESS ;

END a;

―――――――――――――――――――――――――――

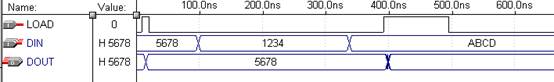

图4 REG16.VHD的时序仿真波形图

图5 顶层设计文件的时序仿真波形图

(CLK=1S,F_IN=175US,END_TIME=5S)

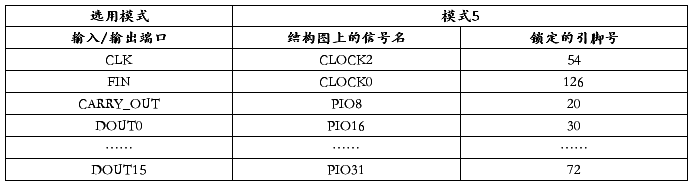

(3)、管脚锁定情况

五、实验结果及总结

1.CLK接CLOCK2中的1Hz。

2.当FIN接CLOCK5中的1024Hz-显示1024Hz;4096Hz-显示4196Hz;

32768Hz-显示2776Hz,并且指示灯D1周期性变化,每周期连续闪动三次。

3.当FIN接CLOCK0中的16384Hz-显示6410Hz,指示灯D1周期性闪动。

4. 当测量四位或四位以下的频率值,数码显示的准确性较高。

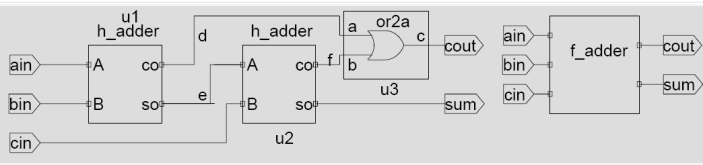

实实验一 用原理图输入法设计一位全加器

一 实验目的

1、熟悉利用QuartusII的原理图输入方法设计简单组合电路

2、掌握层次化设计方法

3、并通过一个一位全加器的设计把握利用EDA软件进行电子线路设计的详细流程

二 实验内容

1、器材用品:

计算机一台

2、步骤

1、建立工作库文件夹;

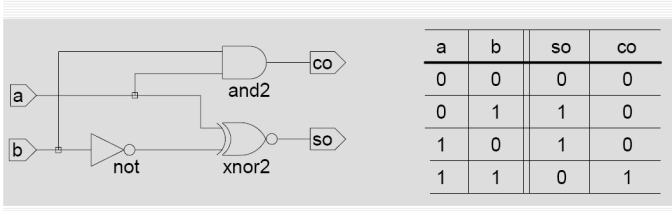

2、编辑设计一位全加器的原理图;半加器原理图

3、在QuartusII软件上进行原理图仿真;

4、

5、实验结果及总结。

l LIBRARY IEEE; --半加器描述(2):真值表描述方法

l USE IEEE.STD_LOGIC_1164.ALL;

l ENTITY h_adder IS

l PORT (a, b : IN STD_LOGIC;

l co, so : OUT STD_LOGIC);

l END ENTITY h_adder;

l ARCHITECTURE fh1 OF h_adder is

l SIGNAL abc : STD_LOGIC_VECTOR(1 DOWNTO 0) ; --定义标准逻辑位矢量数据类型

l BEGIN

l abc <= a & b ; --a相并b,即a与b并置操作

l PROCESS(abc)

l BEGIN

l CASE abc IS --类似于真值表的CASE语句

l WHEN "00" => so<='0'; co<='0' ;

l WHEN "01" => so<='1'; co<='0' ;

l WHEN "10" => so<='1'; co<='0' ;

l WHEN "11" => so<='0'; co<='1' ;

l WHEN OTHERS => NULL ;

l END CASE;

l END PROCESS;

l END ARCHITECTURE fh1 ;

LIBRARY IEEE; --半加器描述(1):布尔方程描述方法

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY h_adder IS

PORT (a, b : IN STD_LOGIC;

co, so : OUT STD_LOGIC);

END ENTITY h_adder;

ARCHITECTURE fh1 OF h_adder is

BEGIN

so <= NOT(a XOR (NOT b)) ; co <= a AND b ;

END ARCHITECTURE fh1;

-

有关实验报告的书写格式

有关实验报告的书写格式江苏省泗阳县李口中学沈正中一、完整实验报告的书写完整的一份实验报告一般包括以下项目:实验名称:实验目的:实验…

-

实验报告格式要求

北京邮电大学世纪学院实验实习课程设计报告撰写格式与要求试行一实验报告格式要求1有实验教学手册按手册要求填写若无则采用统一实验报告封…

-

实验报告书写规范及评分标准

怀化学院基础实验中心实验报告书写规范及评分标准一实验报告书写规范预习报告预习报告的内容包括以下六项1实验名称2实验目的3实验仪器4…

-

实验报告书写要求

实验报告的书写是一项重要的基本技能训练。它不仅是对每次实验的总结,更重要的是它可以初步地培养和训练学生的逻辑归纳能力、综合分析能力…

- 实验报告单格式

-

实验报告书写要求

实验报告的书写是一项重要的基本技能训练。它不仅是对每次实验的总结,更重要的是它可以初步地培养和训练学生的逻辑归纳能力、综合分析能力…

-

有关实验报告的书写格式

有关实验报告的书写格式江苏省泗阳县李口中学沈正中一、完整实验报告的书写完整的一份实验报告一般包括以下项目:实验名称:实验目的:实验…

-

课程设计报告书写主要内容及格式要求20xx

电子技术课程设计设计报告书写要求一关于摘要中文摘要概述设计电路功能结构设计方法结论不超过300字中文关键词35个与设计报告核心内容…

-

实验报告格式及相关要求

本科生实验报告实验课程机械工程测试学院名称核技术与自动化工程学院专业名称机械工程及自动化学生姓名学生学号指导教师实验地点8103实…

- C语言实验报告书写格式及模板

-

初中物理实验报告范文

“浮力消失”了做下面的小试验器材找一个底面很平的容器,让一个蜡烛头紧贴在容器底部,再往容器里倒水,蜡烛头并不会浮起来;轻轻地把蜡烛…