ББгЪЪ§ЕчЪЕбщБЈИц

Ъ§зжЕчТЗгыТпМЩшМЦЪЕбщБЈИц

вЛЁЂвЊЧѓвЊЧѓЃК

ЩшМЦжЦзївЛИіМђвзМЦЫуЦїЃЌЪЕЯжзюДѓЪфШыСНЮЛЪЎНјжЦЪ§зжЕФМгМѕГЫдЫЫуЁЃ

ЛљБОвЊЧѓЃК

1ЁЂ ЪЕЯжзюДѓЪфШыСНЮЛЪЎНјжЦЪ§зжЕФМгМѕГЫдЫЫуЃЛАЫИіВІТыПЊЙиАДСНЮЛ8421bcdТыЪфШыЁЃ

2ЁЂ ФмЙЛЪЕЯжЖрДЮСЌЫуЃЈЮогХЯШМЖЃЌДгзѓЕНгвМЦЫуНсЙћЃЉЃЌШч 12+34×56-78=2498ЁЃ

3ЁЂ зюДѓГЄЖШвдЪ§ТыЙмзюДѓИіЪ§ЮЊЯоЃЌвчГіБЈОЏЁЃ

ЬсИпвЊЧѓЃК

1ЁЂ гае§ИКЪ§ЧјЗжЁЃ

2ЁЂ ЪЕЯжГ§ЗЈЃЈВЛФмећГ§ЪБаЁЪ§БЃСє2ЮЛгааЇЪ§зжЃЉЁЃ

3ЁЂ ЦфЫќРЉеЙЙІФмЁЃ

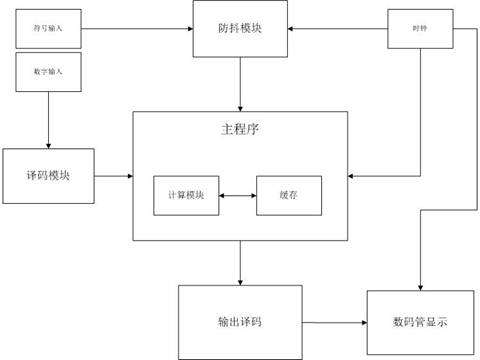

ЖўЁЂЯЕЭГЩшМЦЃК

ЩшМЦЫМТЗЃК

1ЁЂ НЋИУГЬађНјааЗжФЃПщЩшМЦЁЃПЩвдНЋГЬађЗжЮЊЃКжїГЬађЁЂвыТыФЃПщКЭЗРЖЖФЃПщЁЃЦфжаЃЌ

жїГЬађИКд№НЋЪфШыЕФЪ§ОнНјааДцДЂЃЌЖдЪ§ОнНјаадЫЫуЃЌНЋЪ§ОнЪфГіЕНЪ§ТыЩЯЕШЃЛЗРЖЖФЃПщИКд№ЖдАДМќЪфШыЕФЪ§ЗРЖЖЃЛвыТыФЃПщИКд№ЖдЪфШыЕФЪ§ОнНјаавыТыЃЈгЩ8421bcdТызЊЛЏЮЊЪЎНјжЦЕФБрТыЃЉЁЃ

2ЁЂ ЗжФЃПщНјааЯргІФЃПщЕФБраДЁЃ

3ЁЂ ЖдБрКУЕФФЃПщНјааВтЪдЁЃ

4ЁЂ БраДжїГЬађВЂНјааЕїЪдЁЃ

змЬхПђЭМЃК

СїГЬЭМЃК

ЗжПщЩшМЦЃК(АДЪЕМЪВйзїЕФЗжПщ)

ЪфШыФЃПщЃКгЩЗћКХПЊЙиКЭВІТыПЊЙиЙЙГЩЁЃВЩгУађСаДцДЂЕФЗНЪНДцДЂЯргІЕФЪфШыЁЃ

ЪфШывыТыФЃПщЃКНЋЪфШыЕФЗћКХађСазЊЛЏГЩЯШгУзДЬЌЃЌвдБубЁШЁЖдгІЕФМЦЫуЗНЗЈЃЛНЋЪфШыЕФ8421bcdТызЊЛЏГЩЯргІЕФСНЮЛЪЎНјжЦЪ§ЁЃ

Ъ§ТыЯдЪОФЃПщЃКНЋМФДцЦїФкЕФЪ§НјааЪфГіЕНЪ§ТыЙмЩЯЁЃЯдЪОЫљЪфШыЕФЕквЛИіЪ§вдМАзюКѓЕФНсЙћЁЃ

МЦЫуФЃПщЃКЕїгУЯргІЕФМЦЫуЗНЪНЃЌЖдЫљЪфШыЕФЪ§НјааМЦЫуЁЃ

ЗРЖЖФЃПщЃКдкгУАДМќЪфШыЪБЃЌЫљЕУЕНЕФаХКХПЩФм ЛсгаЖЖЖЏЃЌвђДЫМгШыДЫЖЖЖЏЕчТЗЁЃ

Ш§ЁЂЗТецВЈаЮМАВЈаЮЗжЮіЃК

ЗжЮіЃЈВЈаЮЗТецЪБЃЌЮЊСЫЗНБуЙлВьЃЌНЋ8421bcdТыЪфШыЗНЪНЃЌИУЮЊСЫЪЎНјжЦЕФжБНгЪфШыЗНЪНЃЌВЂНЋЪфГіЃЌгадРДЕФЪ§ТыЙмЯдЪОИФГЩСЫжБНгЪ§зжЯдЪОЃЉ

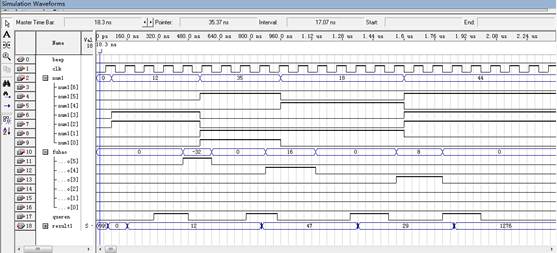

гЩЭМжаПЩвдПДГіЃЌЕБЪфШы12 ЃЌАДЯТ“ШЗЖЈ”ЃЌЪ§зжОЭЪфШыЕНСЫМФДцЦїжаЃЌЪфШы“+”КХЃЈЖдгІЗТецжаЕФfuhao“100000”ЃЉЃЌдкЪфШывЛИіЪ§35ЃЌАДЯТ“ШЗЖЈ”ЃЌИУМЦЫуЦїОЭМўМФДцЦїжаЕФЪ§гыЕкЖўДЮЪфШыЕФЪ§НјааЯрМгЃЌЕУЕННсЙћ47ЁЃДЫЪБИУНсЙћгжБЛжБНгБЃДцЕНСЫМФДцЦїжаЃЌМЬајЪфШыдЫЫуЗћ“-”ЃЈЖдгІЗТецжаЕУfuhao“010000”ЃЉЃЌЪфШыЕкШ§ИіЪ§18ЃЌАДЯТ“ШЗЖЈ”ЃЌМЦЫуЦїЖдЦфзіМѕЗЈдЫЫуЃЌЕУЕННсЙћ29ЃЌИУНсЙћгждкМФДцЦїжаДцДЂзХЁЃМЬајКѓајЪфШыЯргІЗћКХЃЌЯргІЪ§зжПЩвдМЬајНјааЯргІЕФМЦЫуЃЌжЛвЊНсЙћдкЃЈ-99999,99999ЃЉжЎМфЃЌОЭПЩвдвЛжБНјааМЦЫуЁЃ

ЫФЁЂдДГЬађЃК

жїГЬађЃК

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_SIGNED.ALL;

Entity lzjisuanqi is

port(

cat: OUT STD_LOGIC_VECTOR(5 DOWNTO 0);

digital:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);

clk:in std_logic;

beep:out std_logic;

num:in std_logic_vector(7 downto 0);

fuhao:in std_logic_vector(5 downto 0)

);

end entity lzjisuanqi;

architecture lz of lzjisuanqi is

component transform

port(cin:in std_logic_vector(7 downto 0);

cout: out integer range 0 to 99);

end component;

component fangdou IS

PORT(

clk : IN STD_LOGIC;

key_in: IN STD_LOGIC_VECTOR(5 DOWNTO 0);

key_out:OUT STD_LOGIC_VECTOR(5 DOWNTO 0)

);

end component;

type state_type is (s0,s1,s2);

signal state:state_type;

type time_type is (t1,t2,t3,t4,t5,t6);

signal time1:time_type;

signal num1:integer range 0 to 99;

signal result1:integer range -99999 to 99999;

signal result2:integer range -99999 to 99999;

signal cat0:integer range 0 to 9;

signal cat1:integer range 0 to 9;

signal cat2:integer range 0 to 9;

signal cat3:integer range 0 to 9;

signal cat4:integer range 0 to 9;

signal cnt : integer range 0 to 50000;

signal clk_tmp : std_logic;

signal ffuhao: std_logic_vector(5 downto 0);

begin

u1:transform port map(cin=ЃОnum,cout=ЃОnum1); выТы

выТы

u2:fangdou port map(clk=ЃОclk,key_in=ЃОfuhao,key_out=ЃОffuhao);

ЗРЖЖ

ЗРЖЖ

process(clk)

begin

if (clk'event and clk='1') then

if cnt=49999 then

cntЃМ=0;

clk_tmpЃМ= not clk_tmp;

else

cntЃМ=cnt+1;

end if;

end if;

end process;

p1:process(clk_tmp)

variable result:integer range -9999999 to 9999999;  ЛКДц

ЛКДц

variable fuhao1:integer range 0 to 6:=0;

begin

if (clk_tmp'event and clk_tmp='1') then

case state is

when s0=ЃОresult:=num1;

stateЃМ=s1;

when s1=ЃО

if(ffuhao="000010")then

fuhao1:=0;stateЃМ=s1;

elsif(ffuhao="000001")then

result:=num1;fuhao1:=0;stateЃМ=s0;beepЃМ='0';

elsif(ffuhao="001000")then

Ѓffuhao1=3

fuhao1:=3;

stateЃМ=s2;

elsif(ffuhao="010000")then

fuhao1:=2;

stateЃМ=s2;

elsif(ffuhao="100000")then

fuhao1=1

fuhao1:=1;

stateЃМ=s2;

else stateЃМ=s1;

end if;

when s2=ЃОif(fuhao1=0)then

result:=result;stateЃМ=s1;

elsif(fuhao1=1)then

result:=result+num1;

if(resultЃО99999 or resultЃМ-99999)then

result:=num1;beepЃМ='1';stateЃМ=s0;

else beepЃМ='0';stateЃМ=s1;

end if;

elsif(fuhao1=2)then

result:=result-num1;

if(resultЃО99999 or resultЃМ-99999)then

result:=num1;beepЃМ='1';stateЃМ=s0;

else beepЃМ='0';stateЃМ=s1;

end if;

elsif(fuhao1=3)then

result:=result*num1;

if(resultЃО99999 or resultЃМ-99999)then

result:=num1;beepЃМ='1';stateЃМ=s0;

else beepЃМ='0';stateЃМ=s1;

end if;

end if;

end case;

result2ЃМ=result;

if(result2ЃМ0)then result1ЃМ=abs(result2);

else result1ЃМ=result;

end if;

if(result1ЃО=90000)then cat4ЃМ=9;

elsif(result1ЃО=80000 and result1ЃМ90000)then cat4ЃМ=8;

elsif(result1ЃО=70000 and result1ЃМ80000)then cat4ЃМ=7;

elsif(result1ЃО=60000 and result1ЃМ70000)then cat4ЃМ=6;

elsif(result1ЃО=50000 and result1ЃМ60000)then cat4ЃМ=5;

elsif(result1ЃО=40000 and result1ЃМ50000)then cat4ЃМ=4;

elsif(result1ЃО=30000 and result1ЃМ40000)then cat4ЃМ=3;

elsif(result1ЃО=20000 and result1ЃМ30000)then cat4ЃМ=2;

elsif(result1ЃО=10000 and result1ЃМ20000)then cat4ЃМ=1;

elsif(result1ЃМ10000)then cat4ЃМ=0;

end if;

if((result1-cat4*10000)ЃО=9000 and (result1-cat4*10000)ЃМ10000)then cat3ЃМ=9;

elsif((result1-cat4*10000)ЃО=8000 and (result1-cat4*10000)ЃМ9000)then cat3ЃМ=8;

elsif((result1-cat4*10000)ЃО=7000 and (result1-cat4*10000)ЃМ8000)then cat3ЃМ=7;

elsif((result1-cat4*10000)ЃО=6000 and (result1-cat4*10000)ЃМ7000)then cat3ЃМ=6;

elsif((result1-cat4*10000)ЃО=5000 and (result1-cat4*10000)ЃМ6000)then cat3ЃМ=5;

elsif((result1-cat4*10000)ЃО=4000 and (result1-cat4*10000)ЃМ5000)then cat3ЃМ=4;

elsif((result1-cat4*10000)ЃО=3000 and (result1-cat4*10000)ЃМ4000)then cat3ЃМ=3;

elsif((result1-cat4*10000)ЃО=2000 and (result1-cat4*10000)ЃМ3000)then cat3ЃМ=2;

elsif((result1-cat4*10000)ЃО=1000 and (result1-cat4*10000)ЃМ2000)then cat3ЃМ=1;

elsif((result1-cat4*10000)ЃМ1000)then cat3ЃМ=0;

end if;

if((result1-cat4*10000-cat3*1000)ЃО=900and (result-cat4*10000-cat3*1000)ЃМ1000)then cat2ЃМ=9;

elsif((result1-cat4*10000-cat3*1000)ЃО=800and (result1-cat4*10000-cat3*1000)ЃМ900)then cat2ЃМ=8;

elsif((result1-cat4*10000-cat3*1000)ЃО=700and (result1-cat4*10000-cat3*1000)ЃМ800)then cat2ЃМ=7;

elsif((result1-cat4*10000-cat3*1000)ЃО=600and (result1-cat4*10000-cat3*1000)ЃМ700)then cat2ЃМ=6;

elsif((result1-cat4*10000-cat3*1000)ЃО=500and (result1-cat4*10000-cat3*1000)ЃМ600)then cat2ЃМ=5;

elsif((result1-cat4*10000-cat3*1000)ЃО=400and (result1-cat4*10000-cat3*1000)ЃМ500)then cat2ЃМ=4;

elsif((result1-cat4*10000-cat3*1000)ЃО=300and (result1-cat4*10000-cat3*1000)ЃМ400)then cat2ЃМ=3;

elsif((result1-cat4*10000-cat3*1000)ЃО=200and (result1-cat4*10000-cat3*1000)ЃМ300)then cat2ЃМ=2;

elsif((result1-cat4*10000-cat3*1000)ЃО=100and (result1-cat4*10000-cat3*1000)ЃМ200)then cat2ЃМ=1;

elsif((result1-cat4*10000-cat3*1000)ЃМ100) then cat2ЃМ=0;

end if;

if((result1-cat4*10000-cat3*1000-cat2*100)ЃО=90and (result1-cat4*10000-cat3*1000-cat2*100)ЃМ100)then cat1ЃМ=9;

elsif((result1-cat4*10000-cat3*1000-cat2*100)ЃО=80and (result1-cat4*10000-cat3*1000-cat2*100)ЃМ90)then cat1ЃМ=8;

elsif((result1-cat4*10000-cat3*1000-cat2*100)ЃО=70and (result1-cat4*10000-cat3*1000-cat2*100)ЃМ80)then cat1ЃМ=7;

elsif((result1-cat4*10000-cat3*1000-cat2*100)ЃО=60and (result1-cat4*10000-cat3*1000-cat2*100)ЃМ70)then cat1ЃМ=6;

elsif((result1-cat4*10000-cat3*1000-cat2*100)ЃО=50and (result1-cat4*10000-cat3*1000-cat2*100)ЃМ60)then cat1ЃМ=5;

elsif((result1-cat4*10000-cat3*1000-cat2*100)ЃО=40and (result1-cat4*10000-cat3*1000-cat2*100)ЃМ50)then cat1ЃМ=4;

elsif((result1-cat4*10000-cat3*1000-cat2*100)ЃО=30and (result1-cat4*10000-cat3*1000-cat2*100)ЃМ40)then cat1ЃМ=3;

elsif((result1-cat4*10000-cat3*1000-cat2*100)ЃО=20and (result1-cat4*10000-cat3*1000-cat2*100)ЃМ30)then cat1ЃМ=2;

elsif((result1-cat4*10000-cat3*1000-cat2*100)ЃО=10and (result1-cat4*10000-cat3*1000-cat2*100)ЃМ20)then cat1ЃМ=1;

elsif((result1-cat4*10000-cat3*1000-cat2*100)ЃМ10)then cat1ЃМ=0;

end if;

cat0ЃМ=result1-cat4*10000-cat3*1000-cat2*100-cat1*10;

if(resultЃО=0)then  вдЯТЮЊЪ§ТыЙмЯдЪОЯргІЪ§зж

вдЯТЮЊЪ§ТыЙмЯдЪОЯргІЪ§зж

CASE time1 IS

WHEN t1 =ЃО

cat ЃМ= "101111";

CASE cat4 IS

WHEN 0=ЃО digital ЃМ= "1111110";

WHEN 1=ЃО digital ЃМ= "0110000";

WHEN 2=ЃО digital ЃМ= "1101101";

WHEN 3=ЃО digital ЃМ= "1111001";

WHEN 4=ЃО digital ЃМ= "0110011";

WHEN 5=ЃО digital ЃМ= "1011011";

WHEN 6=ЃО digital ЃМ= "1011111";

WHEN 7=ЃО digital ЃМ= "1110000";

WHEN 8=ЃО digital ЃМ= "1111111";

WHEN 9=ЃО digital ЃМ= "1111011";

END CASE;

time1 ЃМ= t2;

WHEN t2 =ЃО

cat ЃМ= "110111";

CASE cat3 IS

WHEN 0=ЃО digital ЃМ= "1111110";

WHEN 1=ЃО digital ЃМ= "0110000";

WHEN 2=ЃО digital ЃМ= "1101101";

WHEN 3=ЃО digital ЃМ= "1111001";

WHEN 4=ЃО digital ЃМ= "0110011";

WHEN 5=ЃО digital ЃМ= "1011011";

WHEN 6=ЃО digital ЃМ= "1011111";

WHEN 7=ЃО digital ЃМ= "1110000";

WHEN 8=ЃО digital ЃМ= "1111111";

WHEN 9=ЃО digital ЃМ= "1111011";

end case;

time1 ЃМ= t3;

WHEN t3 =ЃО

cat ЃМ= "111011";

CASE cat2 IS

WHEN 0=ЃО digital ЃМ= "1111110";

WHEN 1=ЃО digital ЃМ= "0110000";

WHEN 2=ЃО digital ЃМ= "1101101";

WHEN 3=ЃО digital ЃМ= "1111001";

WHEN 4=ЃО digital ЃМ= "0110011";

WHEN 5=ЃО digital ЃМ= "1011011";

WHEN 6=ЃО digital ЃМ= "1011111";

WHEN 7=ЃО digital ЃМ= "1110000";

WHEN 8=ЃО digital ЃМ= "1111111";

WHEN 9=ЃО digital ЃМ= "1111011";

END CASE;

time1 ЃМ= t4;

WHEN t4 =ЃО

cat ЃМ= "111101";

CASE cat1 IS

WHEN 0=ЃО digital ЃМ= "1111110";

WHEN 1=ЃО digital ЃМ= "0110000";

WHEN 2=ЃО digital ЃМ= "1101101";

WHEN 3=ЃО digital ЃМ= "1111001";

WHEN 4=ЃО digital ЃМ= "0110011";

WHEN 5=ЃО digital ЃМ= "1011011";

WHEN 6=ЃО digital ЃМ= "1011111";

WHEN 7=ЃО digital ЃМ= "1110000";

WHEN 8=ЃО digital ЃМ= "1111111";

WHEN 9=ЃО digital ЃМ= "1111011";

END CASE;

time1 ЃМ= t5;

WHEN t5 =ЃО

cat ЃМ= "111110";

CASE cat0 IS

WHEN 0=ЃО digital ЃМ= "1111110";

WHEN 1=ЃО digital ЃМ= "0110000";

WHEN 2=ЃО digital ЃМ= "1101101";

WHEN 3=ЃО digital ЃМ= "1111001";

WHEN 4=ЃО digital ЃМ= "0110011";

WHEN 5=ЃО digital ЃМ= "1011011";

WHEN 6=ЃО digital ЃМ= "1011111";

WHEN 7=ЃО digital ЃМ= "1110000";

WHEN 8=ЃО digital ЃМ= "1111111";

WHEN 9=ЃО digital ЃМ= "1111011";

END CASE;

time1 ЃМ= t1;

WHEN OTHERS =ЃО time1 ЃМ= t1;

END CASE;

elsif(resultЃМ0)then

CASE time1 IS

WHEN t1 =ЃО

cat ЃМ= "101111";

CASE cat4 IS

WHEN 0=ЃО digital ЃМ= "1111110";

WHEN 1=ЃО digital ЃМ= "0110000";

WHEN 2=ЃО digital ЃМ= "1101101";

WHEN 3=ЃО digital ЃМ= "1111001";

WHEN 4=ЃО digital ЃМ= "0110011";

WHEN 5=ЃО digital ЃМ= "1011011";

WHEN 6=ЃО digital ЃМ= "1011111";

WHEN 7=ЃО digital ЃМ= "1110000";

WHEN 8=ЃО digital ЃМ= "1111111";

WHEN 9=ЃО digital ЃМ= "1111011";

END CASE;

time1 ЃМ= t2;

WHEN t2 =ЃО

cat ЃМ= "110111";

CASE cat3 IS

WHEN 0=ЃО digital ЃМ= "1111110";

WHEN 1=ЃО digital ЃМ= "0110000";

WHEN 2=ЃО digital ЃМ= "1101101";

WHEN 3=ЃО digital ЃМ= "1111001";

WHEN 4=ЃО digital ЃМ= "0110011";

WHEN 5=ЃО digital ЃМ= "1011011";

WHEN 6=ЃО digital ЃМ= "1011111";

WHEN 7=ЃО digital ЃМ= "1110000";

WHEN 8=ЃО digital ЃМ= "1111111";

WHEN 9=ЃО digital ЃМ= "1111011";

end case;

time1 ЃМ= t3;

WHEN t3 =ЃО

cat ЃМ= "111011";

CASE cat2 IS

WHEN 0=ЃО digital ЃМ= "1111110";

WHEN 1=ЃО digital ЃМ= "0110000";

WHEN 2=ЃО digital ЃМ= "1101101";

WHEN 3=ЃО digital ЃМ= "1111001";

WHEN 4=ЃО digital ЃМ= "0110011";

WHEN 5=ЃО digital ЃМ= "1011011";

WHEN 6=ЃО digital ЃМ= "1011111";

WHEN 7=ЃО digital ЃМ= "1110000";

WHEN 8=ЃО digital ЃМ= "1111111";

WHEN 9=ЃО digital ЃМ= "1111011";

END CASE;

time1 ЃМ= t4;

WHEN t4 =ЃО

cat ЃМ= "111101";

CASE cat1 IS

WHEN 0=ЃО digital ЃМ= "1111110";

WHEN 1=ЃО digital ЃМ= "0110000";

WHEN 2=ЃО digital ЃМ= "1101101";

WHEN 3=ЃО digital ЃМ= "1111001";

WHEN 4=ЃО digital ЃМ= "0110011";

WHEN 5=ЃО digital ЃМ= "1011011";

WHEN 6=ЃО digital ЃМ= "1011111";

WHEN 7=ЃО digital ЃМ= "1110000";

WHEN 8=ЃО digital ЃМ= "1111111";

WHEN 9=ЃО digital ЃМ= "1111011";

END CASE;

time1 ЃМ= t5;

WHEN t5 =ЃО

cat ЃМ= "111110";

CASE cat0 IS

WHEN 0=ЃО digital ЃМ= "1111110";

WHEN 1=ЃО digital ЃМ= "0110000";

WHEN 2=ЃО digital ЃМ= "1101101";

WHEN 3=ЃО digital ЃМ= "1111001";

WHEN 4=ЃО digital ЃМ= "0110011";

WHEN 5=ЃО digital ЃМ= "1011011";

WHEN 6=ЃО digital ЃМ= "1011111";

WHEN 7=ЃО digital ЃМ= "1110000";

WHEN 8=ЃО digital ЃМ= "1111111";

WHEN 9=ЃО digital ЃМ= "1111011";

END CASE;

time1 ЃМ= t6;

when t6=ЃО

catЃМ="011111";digitalЃМ="0000001";

time1ЃМ=t1;

WHEN OTHERS =ЃО time1 ЃМ= t1;

END CASE;

end if;

end if;

end process;

end lz;

ЗРЖЖФЃПщЃК

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY fangdou IS

PORT(

clk : IN STD_LOGIC;

key_in: IN STD_LOGIC_VECTOR(5 DOWNTO 0);

key_out:OUT STD_LOGIC_VECTOR(5 DOWNTO 0)

);

END fangdou;

ARCHITECTURE behave OF fangdou IS

SIGNAL clk_tmp : STD_LOGIC;

SIGNAL cnt : integer range 0 to 199999;

signal tmp1,tmp2: STD_LOGIC_VECTOR(5 DOWNTO 0);

BEGIN

process(clk)

begin

if (clk'event and clk='1') then

if cnt=199999 then

cntЃМ=0;

clk_tmpЃМ= not clk_tmp;

else

cntЃМ=cnt+1;

end if;

end if;

end process;

PROCESS(clk_tmp)

BEGIN

IF (clk_tmp'EVENT AND clk_tmp='0') THEN

tmp2ЃМ=tmp1;

tmp1ЃМ=key_in;

END If;

END PROCESS;

key_out(0)ЃМ=clk_tmp and tmp1(0) and (not tmp2(0));

key_out(1)ЃМ=clk_tmp and tmp1(1) and (not tmp2(1));

key_out(2)ЃМ=clk_tmp and tmp1(2) and (not tmp2(2));

key_out(3)ЃМ=clk_tmp and tmp1(3) and (not tmp2(3));

key_out(4)ЃМ=clk_tmp and tmp1(4) and (not tmp2(4));

key_out(5)ЃМ=clk_tmp and tmp1(5) and (not tmp2(5));

END behave;

выТыФЃПщЃК

library ieee;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

use ieee.std_logic_1164.all;

entity transform is

port(cin:in std_logic_vector(7 downto 0);

cout: out integer range 0 to 99

);

end entity transform;

architecture behave of transform is

signal h1: integer range 0 to 10;

signal l1: integer range 0 to 10;

begin

m1:process(cin)

begin

case cin(7 downto 4) is

when "0000"=ЃО

h1ЃМ=0;

when "0001"=ЃО

h1ЃМ=1;

when "0010"=ЃО

h1ЃМ=2;

when "0011"=ЃО

h1ЃМ=3;

when "0100"=ЃО

h1ЃМ=4;

when "0101"=ЃО

h1ЃМ=5;

when "0110"=ЃО

h1ЃМ=6;

when "0111"=ЃО

h1ЃМ=7;

when "1000"=ЃО

h1ЃМ=8;

when "1001"=ЃО

h1ЃМ=9;

when others=ЃО

h1ЃМ=10;

end case;

end process m1;

m2:process(cin)

begin

case cin(3 downto 0) is

when "0000"=ЃО

l1ЃМ=0;

when "0001"=ЃО

l1ЃМ=1;

when "0010"=ЃО

l1ЃМ=2;

when "0011"=ЃО

l1ЃМ=3;

when "0100"=ЃО

l1ЃМ=4;

when "0101"=ЃО

l1ЃМ=5;

when "0110"=ЃО

l1ЃМ=6;

when "0111"=ЃО

l1ЃМ=7;

when "1000"=ЃО

l1ЃМ=8;

when "1001"=ЃО

l1ЃМ=9;

when others=ЃО

l1ЃМ=10;

end case;

end process m2;

coutЃМ=h1*10+l1;

end behave;

ЮхЁЂЙІФмЫЕУїЃК

ЪЕбщЕФЛљБОвЊЧѓвбОЪЕЯжЁЃМДФмЪЕЯжЛљБОЕФМгМѕГЫЃЌВЛКЌГ§ЗЈЕФИДКЯЫФдђдЫЫуЃЈДгзѓЕНгвЕФдЫЫуЃЌЮодЫЫугХЯШМЖЃЉЁЃФмзіЕНвчГіБЈОЏЁЃНсЙћгае§ИКЕФЪфГіЁЃОпЬхР§згЃК

99×99=9801 Жј 99×99×99—БЈОЏ

12+21×31-40=983 20-51×8=-248

СљЁЂдЊМўЦїМўЧхЕЅМАзЪдДРћгУЧщПіЃК

ИУЪЕбщЫљашЃКДјquartersЕФМЦЫуЛњвЛЬЈЃЌЪ§зжЕчТЗгыТпМЩшМЦЪЕбщАхвЛИіЁЃзЪдДРћгУЧщПіЃКЫљашТпМЕЅдЊЮЊ81%ЁЃ

ЦпЁЂЙЪеЯМАЮЪЬтЗжЮіЃК

1ЁЂ ЯТдиКѓЃЌАДМќУЛгаЗДгІЁЃ МьбщЯргІЙмНХЪЧЗёЩшжУе§ШЗЃЌМьВщЙмНХЪЧЗёЪЇаЇЁЃ

2ЁЂ Ъ§ТыЙмЯдЪОТвТыЁЃ МьВщЯргІЕФЪфГівыТыВПЗжЪЧЗёе§ШЗЃЌЯргІЙмНХЩшжУЪЧЗёе§ШЗЁЃ

3ЁЂЗфУљЦїВЛЯьЃЌвЛПЊЪМЮвжБНгМьВщДњТыЃЌМьВщСЫКУОУЖМУЛЗЂЯжДэЮѓЃЌКѓРДЛЛСЫИіЪЕбщАхЃЌжиаТЯТдиКѓОЭКУСЫЁЃ

4ЁЂЗТецНсЙћГіВЛРДЃЌПЩФмЪЧгЩгкend timeЩшжУЕУВЛЖдЃЌАбend timeаоИФЁЃ

АЫЁЂзмНсМАНсТлЃК

ЕБбЁЭъЪдбщКѓЃЌЫљгіЕНЕФЕквЛИіЮЪЬтОЭЪЧЩшМЦЫМТЗЕФЮЪЬтЁЃИеПЊЪМЪБЃЌЖдзХЬтФПЃЌИаОѕгааЉЮоДгЯТЪжЃЌКСЮоЭЗаїЁЃгкЪЧевЯргІЕФЪщМЎЃЌдкЭјТчЩЯВщбЏЯрЙизЪСЯЁЃзюКѓжегкгаСЫвЛЕуЕуЫМТЗЁЃЫГзХетЫМТЗЃЌЖдЯргІФЃПщНјааСЫЯргІЩшМЦЃЌдкздМКШЯЮЊПЩвджЎКѓЃЌгкЪЧПЊЪМСЫЯргІДњТыЕФБраДЁЃдкБраДЙ§ГЬжаЃЌгагіЕНСЫЖдvhdlгяЗЈгааЉвХЭќЕФЮЪЬтЃЌгкЪЧЃЌгжЛиЙ§ЭЗШЅИДЯАЯргІЕФгяЗЈЙцдђЁЃВЛЙ§МДБуШчДЫЃЌдкБраДЪБЛЙЪЧГіЯжСЫКмЖрДэЮѓЁЃвЛБрвыЃЌГіЯжСЫКУЖрДэЮѓЃЌгкЪЧвЛИівЛИіШЅевЃЌЗЂЯжздМКДэЕУзюЖрЕФЛЙЪЧifЕФЯрЙигУЗЈЁЃ

етДЮЪЕбщЪеЛёзюЖрЕФЛЙЪЧЖдгкЪ§зжЕчТЗЕФЩшМЦЗНЪНЁЃжЎЧАЫљНгДЅзюЖрЕФЛЙЪЧРэТлЕФЩЯЕФЖЋЮїЁЃЫфШЛЩЯИібЇЦквВзіИіЪ§зжЕчТЗЕФЪЕбщЃЌЕЋФЧИіЪБКђЃЌЮвУЧЫљзіЕФЖМЪЧНЯЮЊМђЕЅЕФЪ§зжЕчТЗЕФЪЕЯжЁЃЖјетИібЇЦкЃЌЮвУЧЫљзіЕФетИіЪЕбщзлКЯадКмИпЁЃДгЪЕбщЕФЩшМЦЕНЪЕбщЭъГЩЃЌЫљвЊОРњЕФЖЋЮїЯрЖдгкжЎЧАЕФвЊЖрЬЋЖрЁЃЭЈЙ§етДЮЪЕбщЃЌЮвЩюПЬвтЪЖЕНЃЌЪ§зжЕчТЗЕФЩшМЦзюРЇФбвдМАзюживЊЕФЛЙЪЧЪЕбщЕФЩшМЦЃЌЖјВЛЪЧДњТыЕФБраДЁЃжЛвЊЩшМЦЫМТЗЖдСЫЃЌНЋЫљашЕФФЃПщЖМЩшМЦКУСЫЃЌДњТыЕФБраДЯрЖдгкЩшМЦЛЙЪЧШнвзЕУЖрЕФЁЃ