毕业设计中期报告

毕业设计(论文)

中期报告

题目名称:基于FPGA的函数信号发生器 院系名称:电子信息学院

班 级:信息072

学 号:xxx

学生姓名:xxx

指导教师:xxx

2011 年 4月

目录

一、 课题任务……………………………………………………2

二、 课题总体方案论述…………………………………………2

三、 阶段性成果…………………………………………………3

四、 后期工作计划………………………………………………9 参考文献 …………………………………………………10

。

1 13

1. 课题任务

1.毕业设计题目:基于FPGA的函数信号发生器。

2.毕业设计要求:本设计要求产生频率,幅度,可调的正弦波,三角波和方波。

2.总体设计方案

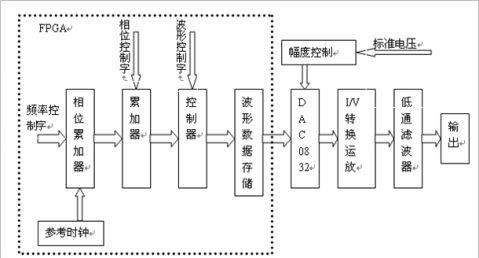

该方案采用FPGA作为中心控制逻辑,由于其具有高速和逻辑单元数多的特点,因此可以由FPGA、DAC和I/V运放直接构成信号源发生器的最小系统。在该方案中通过FPGA控制DAC并直接向DAC发送数据,这样就提高了所需波形的频率并绕过了通用存储器读取速度慢的特点,再加上外部的开关按钮就能够简单控制波形切换与频率选择。当然,为了增加人机界面的交互性与系统功能,可以在原有的基础上添加一个标准键盘和LED或LCD,这样就能够通过编程实现波形的任意性、幅度变化的灵活性。

图1系统总体方案图

2 13

3 阶段性成果

FPGA软件设计部分

3.1频率控制部分(相位累加器)

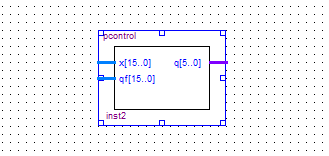

相位累加器模块如图2所示,相位累加器根据参考时钟fc=1024hz以频率控制字K进行累加,实现频率的控制,输出信号频率:fo=Kfc/2N;本设计采用16位的相位累加器,N=16,输出信号频率范围0.015-1024hz。

LIBRARY IEEE;--频率控制器

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY fcontrol IS

PORT ( clk:in std_logic;

f:in std_logic_vector(15 downto 0);

q:out std_logic_vector(15 downto 0));

END ENTITY fcontrol;

ARCHITECTURE behave OF fcontrol IS

signal qf: std_logic_vector(15 downto 0);

signal q1: std_logic_vector(15 downto 0);

BEGIN

PROCESS(clk)

BEGIN

if clk'event and clk='1' then

qf<=f;

q1<=qf+q1;

end if;

q<=q1;

END PROCESS;

END ARCHITECTURE behave;

3

13

图2 相位累加器

3.2相位控制部分

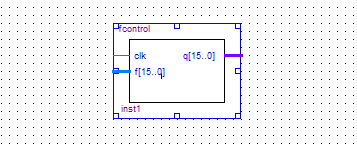

相位增量模块如图3所示,最小相位增量 δ=2π/2N=9.6e-5弧度LIBRARY IEEE;--相位控制器

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY pcontrol IS

PORT ( x:in std_logic_vector(15 downto 0);

qf:in std_logic_vector(15 downto 0);

q:out std_logic_vector(5 downto 0));

END ENTITY pcontrol;

ARCHITECTURE behave OF pcontrol IS

signal q1: std_logic_vector(15 downto 0);

BEGIN

q1<=qf+x;

q<=q1(15 downto 10);

END ARCHITECTURE behave;

图3 相位控制器

4

13

3.3主控器

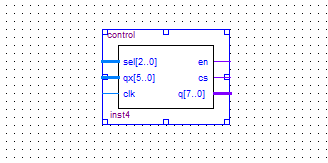

主控器模块如图4所示相位累加器根据参考时钟fc以频率控制字K进行累加,将所得N位的二进制代码,加上相位控制字P和波形控制字W,取其高L位作为ROM的地址,已选择波形。当sel=‘000’,输出为正弦波;sel=‘001’,输出为方波;sel=‘010’,输出为三角波;

LIBRARY IEEE;--主控制器

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY control IS

PORT ( sel:in std_logic_vector(2 downto 0);

qx:in std_logic_vector(5 downto 0);

clk:in std_logic;

en:out std_logic;

cs:out std_logic;

q:out std_logic_vector(8 downto 0));

END ENTITY control;

ARCHITECTURE behave OF control IS

BEGIN

PROCESS(sel,qx,clk)

BEGIN

if sel>"100" then

en<='1';

cs<='1';

q<="000000000";

else

en<=clk;

5

13

cs<='0'; q<=sel&qx; end if; end process;

END ARCHITECTURE behave;

图4 波形选择部分

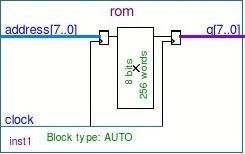

3.4波形数据存储器ROM

波形rom如图5所示,波形数据的建立,FPGA输出的数字信号需要经D/A转换器转换成各种波形输出。而由D/A转换器可知,TLC7528的分辨率是8位,这样,将模拟信号的各种波行在一个周期内平均分成255份,由于已经确定每周期的取样点数为64,即每隔2π/64的间隔取值一次,所取的值为该点对应的波形的值,通过计算可以获得64个取样点的值;也可以通过查表的方法取得64个取样点的值。同理可以获取方波和三角波的波形数据。

图5 波形ROM存储器

6 13

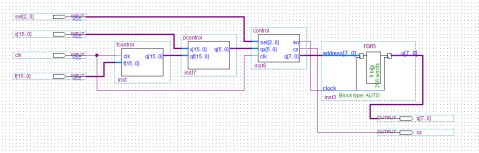

3.5 FPGA顶层设计

图6 顶层设计文件

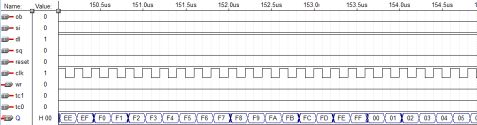

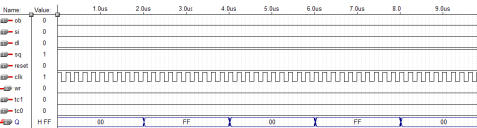

3.6仿真结果

仿真环境是ALTERA公司的Quartus II 9.0sp2软件的一项特殊功能,设置不同的输入信号,可实现不同的波形数据的输出。根据选择的不同开关信号组合,可得到如下图所示各种仿真数据。

(a)正弦波仿真波形

图6

7 13

(b)三角波仿真波形

图7

(c)方波仿真波形

图8

3.7仿真结果分析

对比仿真与实际所得结果,本次课程设计基本上达到了预期的要求,当然在对部分波形输出的处理与最终结果的得出上,我们也中遇到并解决了系列问题。

首先,我们对实验箱的电路组成及连接情况不清楚,不利于编写程序及为实体的各个端口分配引脚。为此,我们找到实验箱的电路原理图,对照原理图结合硬件电路,最终我们搞清楚了电路的组成及连接情况,还有知道了一些必要的硬

8 13

件设置,比如开关是否有效、低通滤波电路电容的选择等问题。

然后,就是带给我们最大困惑的部分——三角波信号的输出。起初的时候我们采用IF语句利用条件赋值语句产生数字信号,但是观察不到预想的波形。经过多次检查修改还是无果后,我们改变了方法利用计数器和CASE语句产生信号,但是编译后发现硬件资源不够,只能放弃这种方法,采用第一种方法。调试分为软件和硬件两部分。在软件调试部分,我们把产生的数字信号送给LED,经过观察,所送的数据与预想的数字信号一致,这表明了软件部分没有问题;结合其它波形能够正确输出并在示波器上显示,我们判断硬件部分也没问题。在百般无奈的情况下,我们向老师请教,最终弄明白了问题。原来正斜率斜波信号经过一段时间后基本上相当于直流信号,而示波器的档位没有调节,仍为交流耦合,故不能观察到信号波形。当调节为直流档位后就可观察到直流波形。

4 时间进度

第一学期

08-12周:阅读相关的外文文献并翻译(汉字3000字以上);

13-17周:熟悉掌握设计任务的要求,查阅资料,确定系统方案;

第二学期

03-04周:完成顶层文件的设计;

05-06周:完成相关软件流程图及主程序的设计;

07-08周:硬件焊接、测试、软件编程;

09-10周:系统软件调试。

11-13周:系统调试;整理有关资料,完成毕业论文的初稿。

14-16周:系统测试、完成毕业论文的修改。

17周: 完成论文,准备毕业答辩。

9 13

参考文献

[1] 卢毅 .VHDL.与数字电路设计[M].科学出版社.北京:2003.

[2] 樊昌信等.通信原理[M].国防工业出版社.北京:1995.

[3] 潘松等.EDA技术实用教程[M].科学出版社[M].北京:2007.

[4] 郝小江,罗彪.基于FPGA的函数信号发生器[J],电测与仪表.2008.(5).

[5] 许开华 .DDS任意波形发生函数器数据生成及传输接口设计[D].电子科技大学硕士学位论文,2007

[6] 杨守良,程正富,基于Matlab/DSP Builder 多波形信号发生器的设计[J].微计算机信息。2007,(10)

[7] 高士友,胡学深,杜兴莉,刘桥.基于FPGA的DDS信号发生器设计[期刊论文]-现代电子技术 2009(16)

[8] 学位论文万永波.基于ARM的任意波发生器开发研究 2006

[9] 学位论文黄振华.基于FPGA函数信号发生器的设计与实现 2009

[10] Altera公司Altera数字图书馆20xx年

a

10 13

第二篇:毕业设计中期报告07071523

毕业设计中期总结报告 ------带侧向抽芯塑件的注塑模设计 专 业:机械设计制造及其自动化指导教师:滕晓燕

姓 名:宾

学 号: 勇 07071523

一、通过设计,达到以下目的

1、从直观的产品入手,正确确定产品的成型方法和分型面,选择合理的成型设备和参数。

2、确定成型方法后,能合理选择相应成型的模具,并确定合理的模具结构。

3、能利用有关设计软件,正确设计模具。

4、熟悉并应用模具标准,以及国家相关技术标准。

5、综合应用所学知识,以及提高理论与实践相结合的应用能力。

二、设计的进展情况

1、分析零件的成形工艺性。

通过对几种塑料进行性能对比,最终确定使用ABS塑料

2、注塑机的选择和参数校核。

根据所设计塑件的特性选择注射机,初步确定选用国产注射机SZ-60/630。

3、模具类型及结构的确定,及有关零件的必要计算和校核。

(1)分型面的选择。选在塑件截面最大的部位。

(2)型腔数目的确定。使用一模两腔。

(3)浇口的确定。使用侧浇口。

(4)模架的选用。选用315×315标准模架。

(5)浇注系统设计。包括主流道、分流道、浇口等。

(6)顶出系统设计。采用推杆脱模机构。

(7)温度调节系统设计。确定冷却方式以及冷却水道的位置和数目。

4、绘制完成了模具装配图的大部分结构。

三、存在的问题及解决措施

在设计过程当中,我深感部分资料和知识的缺乏,尤其是其中注塑机选择校核和部分机构的计算部分,资料中不是一笔带过就是笼统的泛泛而谈,很少有专业细致的探讨。但最后决定弃异存同,将其共性作为本次设计的重点,选择基础结构进行设计。

另外,我还应该多阅读模具设计的有关资料,使设计的模具更有适用性。同时,还应该再加强与指导老师的交流和沟通,加深对本次设计的认识和理解。 总之,我相信自己会继续保持积极的态度,在指导老师的悉心点拨下,能够

快速有效展开接下来的设计流程,顺利完成毕业设计工作。

四、后期工作安排

1、用两周时间绘制模具各主要零部件的零件图及总体装配图。

2、用两周时间用Pro/Engineer绘图软件对主要零部件进行三维建模。

3、用两周时间整理相关资料,撰写毕业论文,准备毕业答辩。

-

毕业论文中期报告+范文

毕业论文中期报告范文根据教务处关于做好二九届本科学生毕业设计论文中期检查的通知文件精神教科学院认真组织了自查工作现将自查情况汇报如…

-

毕业论文中期报告(改)

《代数方程组的MATLAB求解》中期报告专业、班级:数学与应用数学(师范)2班学号:20xx06034250报告人:蔡松廷1、前期…

-

毕业设计(论文)中期报告

毕业设计论文中期报告题目AnAnalysisofsymbolisminAFarewelltoArms院系外国语学院专业英语班级10…

-

毕业论文中期报告

毕业设计论文中期报告院系名称经济管理学院班级工商081学号20xx00634114学生姓名马凯指导教师王海宇20xx年4月毕业设计…

- 毕业论文设计中期检查报告模板

-

20xx届本科毕业论文中期检查自查报告

20xx届本科毕业论文中期检查自查报告根据本学年度教务处和系部具体教学工作的安排,我系于20xx年x月x日组织了20xx届毕业论文…

-

20xx届毕业论文中期检查情况报告

各学院:为做好本科毕业论文(设计)工作,保证本科毕业论文(设计)质量,根据《沈阳农业大学本科毕业论文(设计)工作规范》的要求,学校…

-

20xx届本科毕业论文(设计)中期检查工作汇报

20xx届本科毕业论文(设计)中期检查工作汇报本科毕业论文(设计)是教学工作的一项重要组成部分,它对于培养学生综合运用知识能力、提…

-

毕业设计(论文)中期检查总结表(学生用)

附件毕业设计论文中期检查总结表学生用2总结表由学生填写经指导教师确认签章后统一交各学院存档保留安徽工程大学学院专业毕业设计论文中期…

-

毕业设计(论文)中期检查总结表

附件毕业设计论文中期检查总结表学生用2总结表由学生填写经指导教师确认签章后统一交各学院存档保留安徽工程大学人文学院行政管理专业毕业…

-

毕业论文中期报告(改)

《代数方程组的MATLAB求解》中期报告专业、班级:数学与应用数学(师范)2班学号:20xx06034250报告人:蔡松廷1、前期…