四选一数据选择器实验报告

四选一数据选择器

11微电子 黄跃 1117426021

【实验目的】

1.四选一数据选择器,

2.学习Verilog HDL文本文件进行逻辑设计输入;

3.学习设计仿真工具modelsim的使用方法;

【实验内容】

1. 实现四选一数据选择器的“ Verilog ”语言设计。

2. 设计仿真文件,进行验证。

【实验原理】

数据选择器又称为多路转换器或多路开关,它是数字系统中常用的一种典型电路。其主要功能是从多路数据中选择其中一路信号发送出去。所以它是一个多输入、单输出的组合逻辑电路。

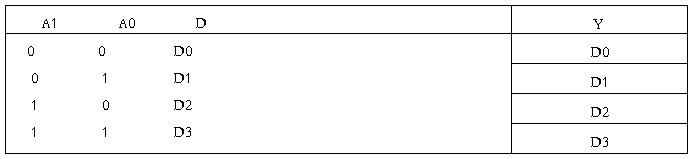

4选1数据选择器的元件符号如图一所示,其中D0、D1、D2、D3是4位数据输入端,A0和A0是控制输入端,Y是数据输出端。当A1A0=00时,输出Y=D1;A1A0=01时,Y=D1;A1A0=10时,Y=D2;A1A0=11,Y=D3。 。

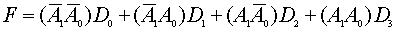

由真值表写出输出逻辑表达式

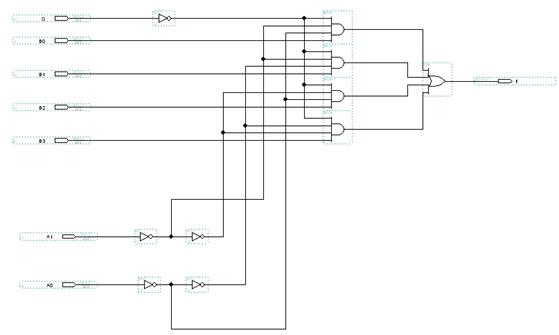

由逻辑表达式做出逻辑电路图。

由逻辑表达式做出逻辑电路图。

【程序源代码】

module mux4_1(sel,in,out);

input [1:0] sel;

input [3:0] in;

output out;

reg out;

always@(sel or in) begin

case ({sel[1],sel[0]})

2'b00: out=in[0];

2'b01: out=in[1];

2'b10: out=in[2];

2'b11: out=in[3];

default: out=1'bx;

endcase

end

Endmodule

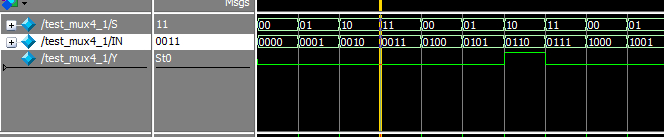

测试程序代码如下:

module test_mux4_1;

reg [1:0] S;

reg [3:0] IN;

wire Y;

mux4_1 M1(.sel(S),

.in(IN),

.out(Y));

always #10 IN[0]=~IN[0];

always #20 IN[1]=~IN[1];

always #40 IN[2]=~IN[2];

always #80 IN[3]=~IN[3];

initial

begin S=1'b0;IN=4'h0;

#100 $stop;

end

always #10 S=S+1;

endmodule

【仿真和测试结果】

【实验心得和体会】

这次实验与上次相比有明显的进步,通过这次实验我对modelsim的应用更加得心应手,深切的体会到了verilog是一种描述性语言,这次实验总的来说是比较顺利的,但在实验过程中还是遇到了一些问题,比如端口的匹配问题,在写程序的时候误将位宽写在了变量名的后面,虽然程序能够运行但有警告,仿真波形是错误的,可见在写程序时警告有时也是致命的,这要求我们在学习的过程中思想一定要严谨!其次在做实验时一定要多想,例如在学习这门课时,书上说在模块外部输入可以是wire型或reg型,但在写程序时激励模块往往要初始化数据,所以编程时其类型往往声明为reg型,通过这个例子我明白了书上所说的有时往往是一个比较笼统的,而更多的需要我们自己去实践、探索、勤思考,只有这样我们才能把书本上的知识转化为属于我们自己的知识,才能在学习的道路上走的更远!

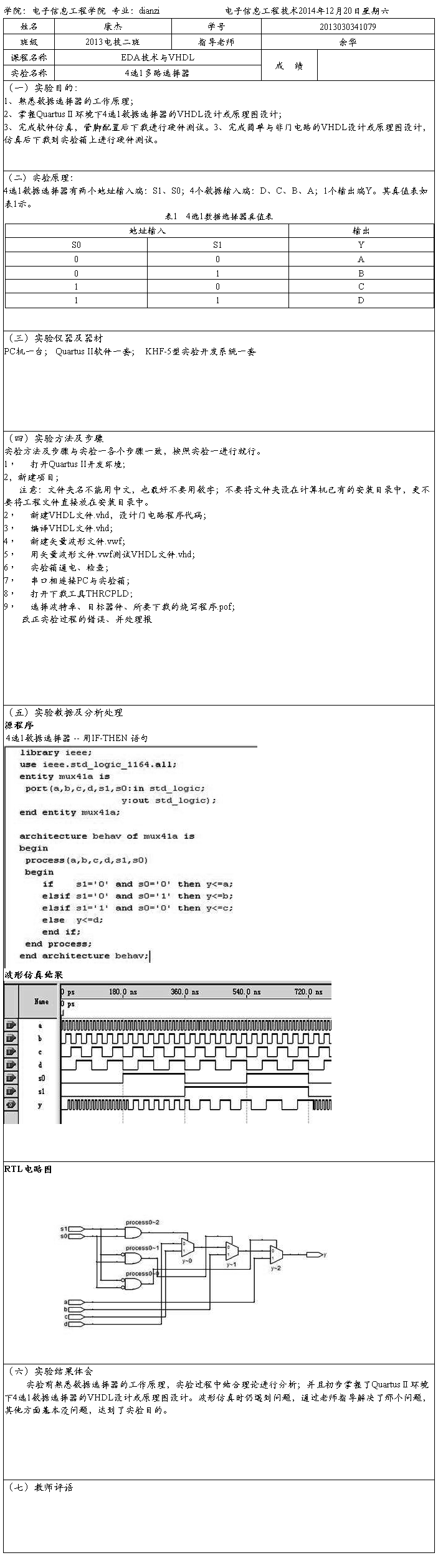

第二篇:EDA技术4选1多路选择器实验报告

实验报告

-

数据选择器实验报告

实验三数据选择器实验人员班号学号一实验目的1熟悉并掌握数据选择器的功能2用双4选1数据选择器74LS153设计出一个16选1的数据…

- 电子技术实验报告3-数据选择器及其应用

- 实验报告:数据选择器

-

(集成电路应用设计实验报告)数据选择器及其应用

电子科技大学成都学院课程结题报告20xx年6月数据选择器及其应用一实验器材设备元器件1数字模拟实验装置1台2数字电路实验板1块37…

-

数据选择器实验报告

数电实验二姓名:##学号:##组别:5实验题目:数据选择器实验目的:了解数据选择器的工作原理;熟悉数据选择器的引脚及其作用;熟悉数…

-

译码器和数据选择器 实验报告(有数据)

实验三译码器和数据选择器一实验目的1熟悉集成译码器2学习集成译码器和数据选择器的应用二实验仪器及器件1双踪示波器2实验用元器件74…

-

译码器和数据选择器实验报告

译码器和数据选择器12级电子信息工程20xx1060192朱加熊实验目的1熟悉集成译码器和数据选择器2掌握集成译码器和数据选择器的…

-

数据选择器和译码器实验报告

数字逻辑实验报告题目数据选择器和译码器一实验目的1熟悉数据选择器的逻辑功能2熟悉译码器的逻辑功能二实验所用器件和仪表1双4选1数据…

-

数据选择器实验报告

实验三数据选择器实验人员班号学号一实验目的1熟悉并掌握数据选择器的功能2用双4选1数据选择器74LS153设计出一个16选1的数据…

-

:数据选择器设计(实验报告)

实验报告一实验目的熟悉Quartus的VHDL文本设计流程全过程学习简单组合电路的设计多层次电路设计仿真和硬件测试二实验设备GW4…

-

数据选择器实验报告

数据选择器的应用一实验目的1了解74LS0074LS8674LS153芯片的内部结构和功能2了解数据选择器的结构和功能3了解全加器…