实验三 8选1数据选择器实验报告

实验三、八选一数据选择器

一、 实验目的:

1.熟悉Quartus II6.0软件的使用和FPGA设计流程

2.用VHDL语言进行八选一数据选择器的设计

二、 实验步骤:

一. 建立文件夹:在D盘 “xingming”的文件夹下建立一个名为“choice8”的文件夹。

二. 建立新工程

1. 双击桌面上Quartus II6.0 的图标,启动该软件。

2. 通过File => New Project Wizard… 菜单命令启动新项目向导。在随后弹出的对话框上点击Next按钮,在 What is the working directory for this project 栏目中设定新项目所使用的路径:D:\xingming\choice8;在 What is the name of this project 栏目中输入新项目的名字:choice8,点击 Next 按钮。在下一个出现的对话框中继续点击Next,跳过这步。

3. 为本项目指定目标器件:选择器件系列为ACEX1K ,选择具体器件为EP1K30TC144-3 1728 24576 ,再点击Next。在弹出的下一对话框中继续点击Next ,最后确认相关设置,点击Finish按钮,完成新项目创建。

三. 设计输入

1. 建立一个VHDL文件。通过 File => New 菜单命令,在随后弹出的对话框中选择 VHDL File选项,点击 OK 按钮。通过 File => Save As 命令,将其保存,并加入到项目中。

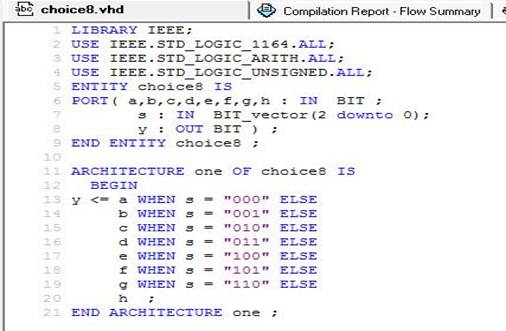

2.  在VHDL界面输入8选1数据选择器程序,然后通过File => Save As 命令保存。

在VHDL界面输入8选1数据选择器程序,然后通过File => Save As 命令保存。

四. 综合适配

1. 选择Processing =>Start Compilation命令,检查发现无程序语法错误。

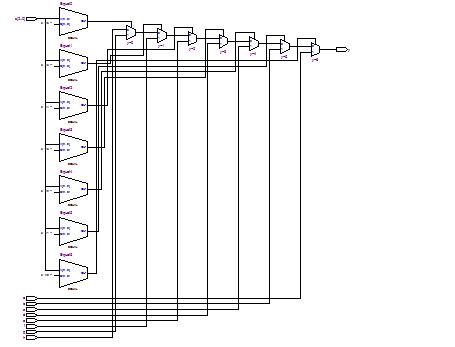

2. 执行Tools =>Netlist Viewer =>RTL Viewe, 生成RTL图。

五. 模拟仿真

1. 在 File 菜单下,点击 New 命令。在随后弹出的对话框中,切换到 Other Files 页。选中 Vector Waveform File 选项,点击 OK 按钮。

2. 选择命令 Edit=>End Time ,时间设置为30000ns , 进入到波形编辑界面。在 Edit 菜单下,点击 Insert Node or Bus… 命令,或在结点名字区连续双击鼠标左键两次,在新出现的框图中点击Node Finder出现结点查找器窗口搜索结点名, 在上一个框图中点击 Node Finder… 按钮后,打开 Node Finder 对话框。点击 List 按钮,列出电路所有的端子。点击 >> 按钮,全部加入。点击 OK 按钮,确认。

3. 回到 Insert Node or Bus 对话框,点击 OK 按钮,确认。

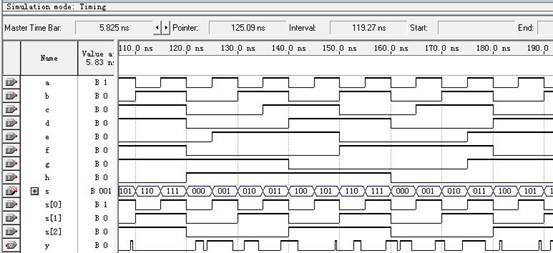

4. 编辑输入激励信号波形.选中 a 信号,在 Edit 菜单下,选择 Value => Clock… 命令。在随后弹出的对话框的 Period 栏目中设定参数为10ns,点击 OK 按钮,重复前面的操作,设置输入信号b的参数为20ns ,c信号的参数为30ns,d信号的参数为40ns,e信号的参数为50ns,f信号的参数为60ns,g信号的参数为70ns,h信号的参数为80ns,输入激励信号波形编辑完毕。同样的,s[0]、s[1]、s[2]的参数分别设置为10ns、20ns、30ns。

5. 功能仿真:(1)Processing=>Generate Functional Simulation Netlist

(2)使用命令Processing=>Simulator Tool ,出现模拟器窗口 ,在simulation mode中选择Functional ,指定波形文件为choice8.vwl ,点击start 开始,成功后点击Report查看仿真波形

1. 时序仿真:

(1)Processing=>Generate Functional Simulation Netlist

(2)使用命令Processing=>Simulator Tool ,出现模拟器窗口

在simulation mode中选择timing,指定波形文件为choice8.vwl ,点击start 开始,成功后点击Report查看仿真波形

六. 引脚分配

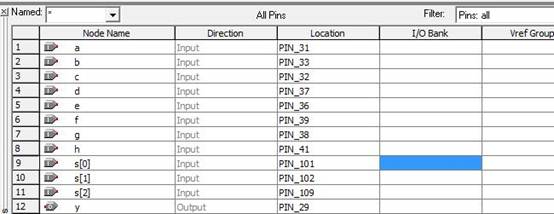

1. 在 Assignments 菜单下,点击 Pin Planner 命令,出现如下图示。在这个工具中,我们可以为我们的电路的端子分配器件的引脚。在 All Pins 表格中,双击 Node Name 列的 new node 单元,选择所有端口的名字。在同一行的 Location 列,选择要分配的位置。重复操作,为每个端子都分配适当的脚位。

2. 在 Assignments 菜单下,点击 Device… 命令。在随后弹出的对话框中点击 Device & Pin Options… 按钮,进入 Device & Pin Options 对话框。切换到 Unused Pins 页,在 Reserved all unused pins 栏目中,选择 As input tri-stated 。点击确定按钮,确认设置。回到 Seting 对话框,点击 OK 按钮。

3. 在这些均设置好后,选择 Processing 菜单下,点击 Start Compilation 命令,开始再一次编译我们的项目。编译结束后,点击“确定”按钮。

七. 下载与配置

1. 可编程器件通过专用电缆和计算机相连,使用命Tools=>Programmer打开编程模块窗口,目标器件名和编程文件名必须正确地显示在该窗口中。

2. 回到编程器窗口,选中program/configure,再点击Start启动编程。

3.下载成功后,在试验箱中进行试验,可观察到实验结果。

三、实验感想

在这次的试验中,因为是第三次使用Quartus II6.0做实验,所以,对于实验的步骤和流程比较熟悉了,这次试验是根据二选一和四选一数据选择器来改编八选一数据选择器,但是,在改编VHDL语言程序的过程中,遇到的一个问题就是由于输入法没有调整到英文状态,导致程序无法正常进行编译,后面检查后就修正过来了。

这个实验一共做了两次,因为第一次做之后,写实验报告时发现实验截图不全,即功能仿真和时序仿真的仿真波形图没有截出输入输出信号的字母标识。这样从图中并不能清楚看出实验仿真结果,在第二次做的时候,只需要打开原来建好的工程,而不需要重新输入实验图。在这反复的犯错与练习的过程中,使我基本上掌握了该软件的使用,以后碰到一些问题也会自己解决了。

通过这次的实验,也是我更加熟悉了VHDL语言设计程序的一些基本规则和他的简单语法结构,巩固和加深了课堂知识。

第二篇:实验二 4选1数据选择器的设计

实验二 4选1数据选择器的设计

实验学时:2学时

实验类型:设计

实验要求:必做

一、实验目的

通过实验让学生掌握组合逻辑电路的EDA原理图输入设计法,通过电路的仿真和硬件验证,让学生进一步了解4选1数据选择器的功能。

二、实验原理

数据选择器又叫“多路开关”。数据选择器在地址码(或叫选择控制)电位的控制下,从几个数据输入中选择一个并将其送到一个公共的输出端。数据选择器的功能类似一个多掷开关。数据选择器为目前逻辑设计中应用十分广泛的逻辑部件,它有2选1、4选1、8选1、16选1等类别。数据选择器的电路结构一般由于活门阵列而成,也有用传输门开关和门电路混合而成的。

图1 4选1数据选择器原理图

图1是一个4选1数据选择器,d3—d0是数据输入端,s1和s0是控制输入端,y是4选1数据输出端。

三、实验内容

设计并实现一个4选1数据选择器,要求根据原理图写出它的逻辑关系,并利用开发工具软件对其进行编译和仿真,最后通过实验开发系统对其进行硬件验证。

四、实验步骤

1)在Maxplus2的图形编辑方式下,从prim元件库中调出4选1数据选择器电路所需要的元件。并按照图1所示的原理电路,完成4选1数据选择器原理图的输入设计。

2)保存好原理图文件,以mux41.gdf为文件名保存在工程目录中。执行Compiler命令对设计文件进行编译。执行Create Default Symbol命令,可为4选1数据选择器生成一个元件符号。

3)在波形编辑方式下,编辑mux41.gdf的波形文件,并完成输入信号d3,d2,d1和d0,控制信号s1和s0电平的设置。波形文件编辑结束后以mux41.scf为波形文件名存盘。执行仿真器Simulator命令,仿真开始,观察仿真波形进行设计电路的功能验证。

五、实验结果

1. 4选1数据选择器的逻辑功能及真值表

2.仿真波形

-

数据选择器实验报告

实验三数据选择器实验人员班号学号一实验目的1熟悉并掌握数据选择器的功能2用双4选1数据选择器74LS153设计出一个16选1的数据…

- 电子技术实验报告3-数据选择器及其应用

- 实验报告:数据选择器

-

(集成电路应用设计实验报告)数据选择器及其应用

电子科技大学成都学院课程结题报告20xx年6月数据选择器及其应用一实验器材设备元器件1数字模拟实验装置1台2数字电路实验板1块37…

-

数据选择器实验报告

数电实验二姓名:##学号:##组别:5实验题目:数据选择器实验目的:了解数据选择器的工作原理;熟悉数据选择器的引脚及其作用;熟悉数…

- 电子技术实验报告5-触发器及其应用

-

译码器和数据选择器 实验报告(有数据)

实验三译码器和数据选择器一实验目的1熟悉集成译码器2学习集成译码器和数据选择器的应用二实验仪器及器件1双踪示波器2实验用元器件74…

-

译码器和数据选择器实验报告

译码器和数据选择器12级电子信息工程20xx1060192朱加熊实验目的1熟悉集成译码器和数据选择器2掌握集成译码器和数据选择器的…

-

数据选择器和译码器实验报告

数字逻辑实验报告题目数据选择器和译码器一实验目的1熟悉数据选择器的逻辑功能2熟悉译码器的逻辑功能二实验所用器件和仪表1双4选1数据…

-

实验二 译码器与数据选择器的功能测试及应用 (实验报告)

实验2译码器与数据选择器的功能测试及应用一实验目的与要求5分1掌握中规模集成译码器与数据选择器的逻辑功能和使用方法2学习用集成译码…

-

数据选择器实验报告

实验三数据选择器实验人员班号学号一实验目的1熟悉并掌握数据选择器的功能2用双4选1数据选择器74LS153设计出一个16选1的数据…