数码管扫描显示控制器设计与实现——北京邮电数字电路实验报告

北京邮电大学

实 验 报 告

实验名称:数码管扫描显示控制器设计与实现

学 院: 信息与通信工程学院

班 级:

姓 名:

学 号:

日 期: 20##年5月

索 引

一.实验目的... 3

二.实验所用仪器及元器件... 3

三.实验任务要求... 3

四.实验设计思路及过程... 4

1.实验原理... 4

2.设计思路... 4

3.VHDL代码... 5

A.实验任务1. 5

B.实验任务2-I 8

C.实验任务2-II 11

五.仿真波形及分析... 12

1.仿真波形... 12

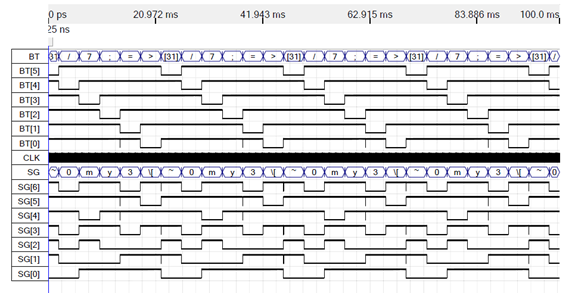

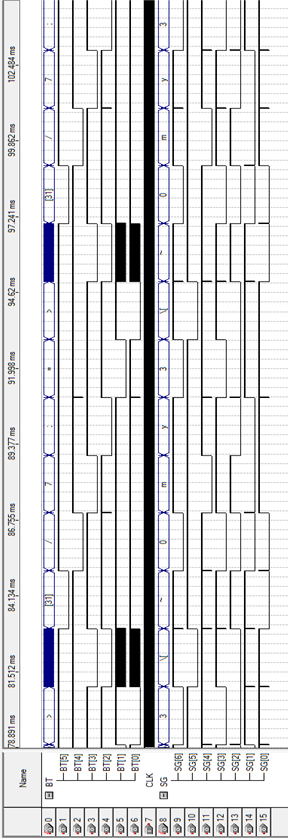

①实验任务1. 12

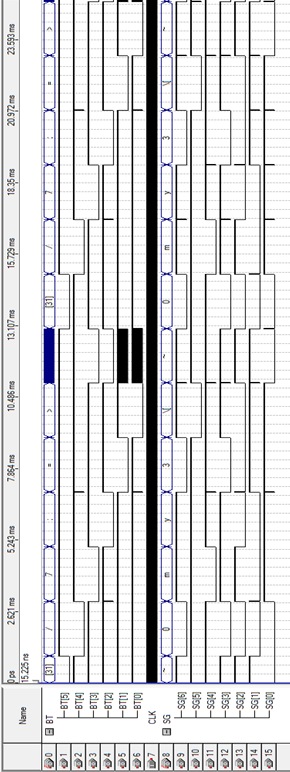

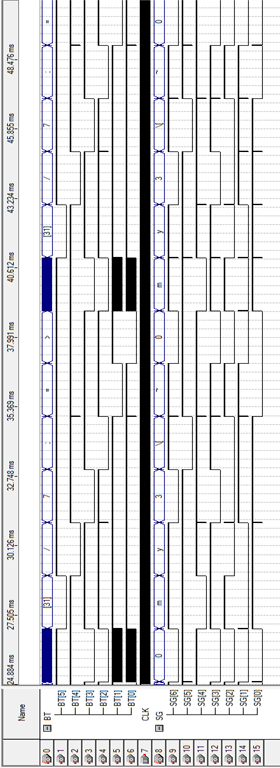

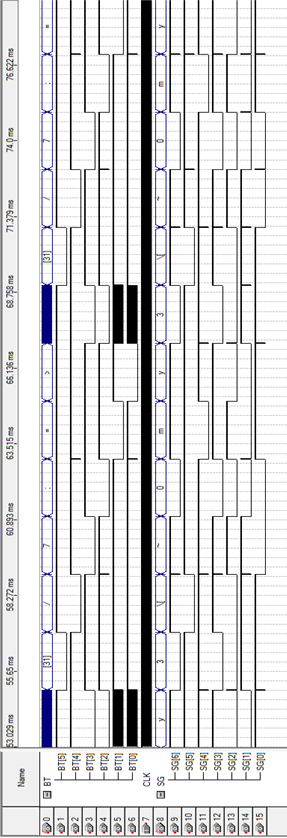

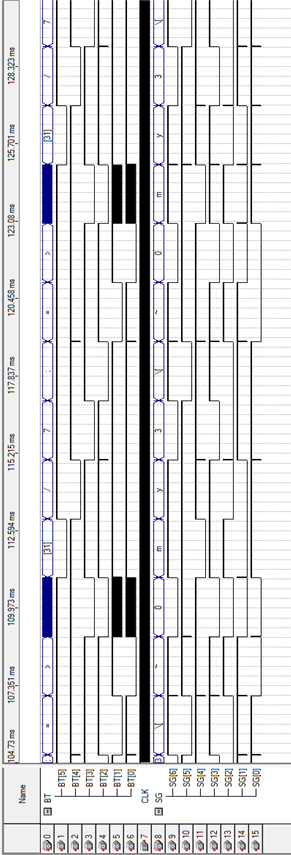

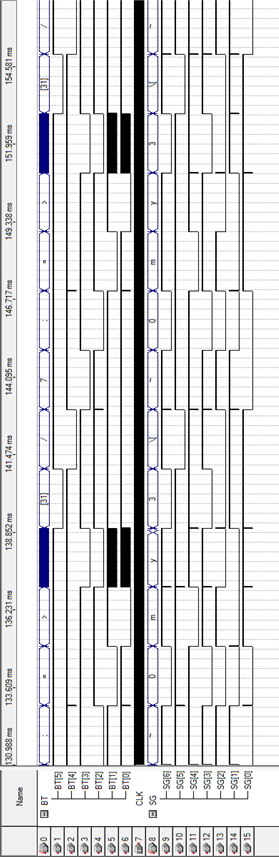

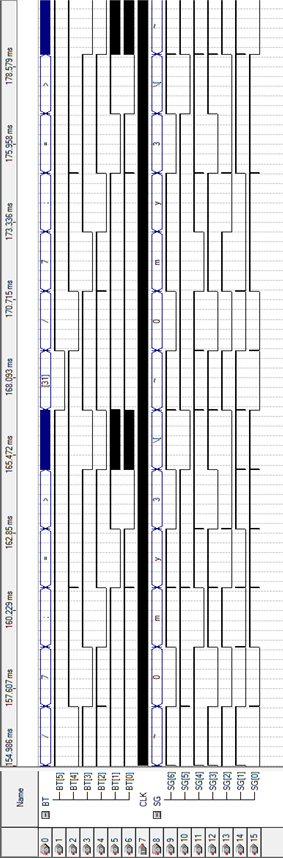

②实验任务2-I 13

3.波形分析... 17

①实验任务1. 17

②实验任务2-I 17

六.故障及问题分析... 18

1.频率设置问题... 18

2.触发问题... 18

3.逻辑实现问题... 18

七.本实验总结与结论... 19

八.学期总结... 19

九.参考文献... 19

一.实验目的

1. 掌握VHDL语言的语法规范,掌握时序电路描述方法

2. 掌握多个数码管动态扫描显示的原理及设计方法

二.实验所用仪器及元器件

1. 计算机

2. 直流稳压电源

3. 数字系统与逻辑设计实验开发板

三.实验任务要求

1. 用VHDL语言设计并实现六个数码管串行扫描电路,要求同时显示0,1,2,3,4,5这六个不同的数字图形到六个数码管上,仿真下载验证其功能。

2. 用VHDL语言设计并实现六个数码管滚动显示电路。(选作)

I. 循环滚动,始终点亮6个数码管,左出右进。状态为:012345-123450-234501-345012-450123-501234-012345

II. 向左滚动,用全灭的数码管充右边,直至全部变灭,然后再依次从右边一个一个地点亮。状态为:012345-12345X-2345XX-345XXX-45XXXX-5XXXXX-XXXXXX-XXXXX0-XXXX01-XXX012-XX0123-X01234-012345,其中’X’表示数码管不显示。

四.实验设计思路及过程

1.实验原理

为使得输入控制电路简单且易于实现,采用动态扫描的方式实现设计要求。动态扫描显示需要由两组信号来控制:一组是字段输出口输出的字形代码,用来控制显示的字形,称为段码;另一组是位输出口输出的控制信号,用来选择第几位数码管工作,称为位码。

各位数码管的段线并联,段码的输出对各位数码管来说都是相同的。因此在同一时刻如果各位数码管的位选线都处于选通状态的话,6位数码管将显示相同的字符。若要各位数码管能够显示出与本位相应的字符,就必须采用扫描显示方式,即在某一时刻,只让某一位的位选线处于导通状态,而其它各位的位选线处于关闭状态。同时,段线上输出相应位要显示字符的字型码。这样在同一时刻,只有选通的那一位显示出字符,而其它各位则是熄灭的,如此循环下去,就可以使各位数码管显示出将要显示的字符。

虽然这些字符是在不同时刻出现的,而且同一时刻,只有一位显示,其它各位熄灭,但由于数码管具有余辉特性和人眼有视觉暂留现象,只要每位数码管显示间隔足够短,给人眼的视觉印象就会是连续稳定地显示。

总之,多个数码管动态扫描显示,是将所有数码管的相同段并联在一起,通过选通信号分时控制各个数码管的公共端,循环一次点亮多个数码管,并利用人眼的视觉暂留现象,只要扫描的频率大于50Hz,将看不到闪烁现象。6个数码管则需要50*6=300Hz以上才能看到持续稳定点亮的现象。

2.设计思路

设计时序电路,输入时钟经过一个分频器,产生2kHz的扫描信号作为时钟,驱动计数器工作。选用模值为6的计数器,通过一个3线至6线译码器,产生段码,依次控制6个LED的亮灭,使得某一时刻有且仅有一个LED点亮,同时产生对应的,将点亮的LED数码管赋值显示为相应的数码予以显示。由于扫描频率较高,6位LED数码管序列将显示持续稳定的0至5的数码。

3.VHDL代码

A.实验任务1

①实现代码

--2kHz 分频器

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity div2k is

port(clk_in : in std_logic;

clk_out : out std_logic);

end;

architecture a of div2k is

signal cnt : integer range 0 to 999;

signal clk_tmp : std_logic;

begin

process(clk_in)

begin

if (clk_in'event and clk_in='1') then

if cnt=999 then

cnt<=0; clk_tmp<= not clk_tmp;

else

cnt<=cnt+1;

end if;

end if;

end process;

clk_out<=clk_tmp;

end;

--SCAN_LED:LED动态扫描

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY SCAN_LED IS

PORT ( CLK : IN STD_LOGIC;

SG : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);

BT : OUT STD_LOGIC_VECTOR(5 DOWNTO 0) );

END;

ARCHITECTURE arc OF SCAN_LED IS

component div2k

port(clk_in: in std_logic; clk_out: out std_logic);

end component;

SIGNAL CNT6 : INTEGER RANGE 0 TO 6;

SIGNAL A : INTEGER RANGE 0 TO 5;

SIGNAL clk_tmp: STD_LOGIC;

BEGIN

u1:div2k port map(clk_in=>CLK,clk_out=>clk_tmp);

P1:process(CNT6)

BEGIN

CASE CNT6 IS --3线至6线译码器

WHEN 0 => BT <= "011111" ; A <= 0 ; --A为位码

WHEN 1 => BT <= "101111" ; A <= 1 ;

WHEN 2 => BT <= "110111" ; A <= 2 ;

WHEN 3 => BT <= "111011" ; A <= 3 ;

WHEN 4 => BT <= "111101" ; A <= 4 ;

WHEN 5 => BT <= "111110" ; A <= 5 ;

WHEN OTHERS => NULL ;

END CASE ;

END PROCESS P1;

P2:process(clk_tmp)

BEGIN

IF clk_tmp'EVENT AND clk_tmp = '1' THEN --实现模6计数器

CNT6 <= CNT6 + 1;

if CNT6 = 5 then

CNT6 <= 0;

end if;

END IF;

END PROCESS P2;

P3:process(A)

BEGIN

CASE A IS --实现数码管的显示功能

WHEN 0 => SG <= "1111110"; WHEN 1 => SG <= "0110000";

WHEN 2 => SG <= "1101101"; WHEN 3 => SG <= "1111001";

WHEN 4 => SG <= "0110011"; WHEN 5 => SG <= "1011011";

WHEN OTHERS => NULL ;

END CASE ;

END PROCESS P3;

END arc;

②代码说明

通过分频器输入产生选通脉冲,控制0至5号LED数码管依次亮灭,同时使用数码显示信号使得数码管显示相应数码。实现时通过连接引入分频信号,通过数据选择器选择数码管。计数器信号触发数据选择器,赋值给位码触发数码管显示数码。最终实现动态扫描显示数字序列。

B.实验任务2-I

①实现代码

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY scan_led_2 IS

PORT ( CLK : IN STD_LOGIC;

SG : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);

BT : OUT STD_LOGIC_VECTOR(5 DOWNTO 0) );

END;

ARCHITECTURE arc OF scan_led_2 IS

component div2k

port(clk_in: in std_logic;

clk_out: out std_logic);

end component;

SIGNAL CNT6 : INTEGER RANGE 0 TO 6;

SIGNAL A : INTEGER RANGE 0 TO 5;

SIGNAL COUNT : INTEGER RANGE 0 TO 5001 := 0;

SIGNAl FLAG : INTEGER RANGE 0 TO 7 := 0;

SIGNAl FLAG_A : INTEGER RANGE 0 TO 5;

SIGNAL clk_tmp : STD_LOGIC;

BEGIN

u1:div2k port map(clk_in=>CLK,clk_out=>clk_tmp);

P1:process(CNT6)

BEGIN

CASE CNT6 IS

WHEN 0 => BT <= "011111" ; A <= 0 ; --3线至6线译码器

WHEN 1 => BT <= "101111" ; A <= 1 ;

WHEN 2 => BT <= "110111" ; A <= 2 ;

WHEN 3 => BT <= "111011" ; A <= 3 ;

WHEN 4 => BT <= "111101" ; A <= 4 ;

WHEN 5 => BT <= "111110" ; A <= 5 ;

WHEN OTHERS => NULL ; END CASE ;

END PROCESS P1;

P2:process(clk_tmp)

BEGIN

IF clk_tmp'EVENT AND clk_tmp = '1' THEN --实现模6计数器

CNT6 <= CNT6 + 1;

if CNT6 = 5 then

CNT6 <= 0;

end if;

IF (FLAG = 6) THEN --设置标志

FLAG <= 0;

END IF;

IF COUNT = 5000 THEN --相当于另一个时钟

COUNT <= 0; --计数周期为5000

FLAG <= FLAG + 1; --当记满5000时左移动一位

ELSE

COUNT <= COUNT + 1; --不满5000继续计数

END IF;

END IF;

END PROCESS P2;

P3:process(A)

BEGIN

FLAG_A <= (( A + FLAG ) mod 6) ; --使用求余运算实现移位

CASE FLAG_A IS --实现数码管的显示功能

WHEN 0 => SG <= "1111110"; WHEN 1 => SG <= "0110000";

WHEN 2 => SG <= "1101101"; WHEN 3 => SG <= "1111001";

WHEN 4 => SG <= "0110011"; WHEN 5 => SG <= "1011011";

WHEN OTHERS => NULL ;

END CASE ;

END PROCESS P3;

END arc;

②代码说明

代码主体和实验任务1中一致,基本思想也一致。为实现移位,关键改动为新增一个计数器,技术周期远远大于扫描周期,这样,在一个大的计数周期内,对于要显示的6位数码进行动态扫描(和实验任务1中相同),显示出6种移位状态中的一种;在下一个大的周期内,利用FLAG标志,并使用求余运算将显示位的数码移位,比如,大的计数周期为0时,FLAG为0,显示“012345”六位数码,大的周期为1时,FALG为1,此时各位求余(即FLAG_A求余)对应的数码为123450,显示的数码也就为“123450”。以此类推,实现循环移位。

C.实验任务2-II

①实现代码

P2:process(clk_tmp)

BEGIN

IF clk_tmp'EVENT AND clk_tmp = '1' THEN

CNT6 <= CNT6 + 1; --模6计数器

if CNT6 = 6 then

CNT6 <= 0;

end if;

IF (FLAG = 7) THEN

FLAG_SC <= 1; --序列反移位标志

END IF;

IF (FLAG = 0) THEN

FLAG_SC <= 0; --序列左移位标志

END IF;

IF COUNT = 5000 THEN

COUNT <= 0;

IF FLAG_SC = 1 THEN

FLAG <= FLAG - 1 ; --记满大周期序列反移位

ELSE

FLAG <= FLAG + 1 ; --记满大周期序列左移位

END IF;

ELSE

COUNT <= COUNT + 1;

END IF;

IF FLAG_SC = 1 THEN

FLAG_A <= A - FLAG ; --序列反移位

ELSE

FLAG_A <= A + FLAG ; --序列左移位

END IF;

END IF;

END PROCESS P2;

②代码说明

此处为关键部分代码,其余代码同实验任务2-I中基本相同。实现基本思路为:先左移位,方法同实验任务2-I,进行加运算,稍有不同为左移出的数码不从右移入,因而没有取余运算,大于6的数码状态为灭灯,实现了左移且右端数码依次熄灭。待全部灯熄灭(此时FLAG已经加到了7)后数码依次从右移入,此时进行减运算(加减运算由FLAG_SC控制),右端数码最先达到0,显示数码“0”,然后是右端第二位达到0,显示数码“0”,右端第一位为1,显示数码“1”,其余灯灭,以此类推,实现了右端逐位移入数码的功能。

五.仿真波形及分析

1.仿真波形

①实验任务1

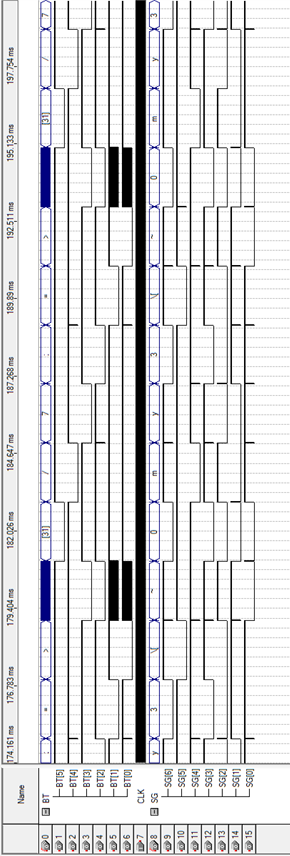

②实验任务2-I

3.波形分析

①实验任务1

由波形可见,随着时钟模六计数的不断重复,0至5号LED数码管依次打开,其余管熄灭,同时,数码管显示数字从0至5依次出现,两者保持同步,即n号管亮时显示的数码为n。这样每计数6次循环依次,可知仿真结果正确。当扫描速度很快时,人眼将能看到持续稳定的0至5号数码显示。在实验室实际测试时,下载到电路板测试成功,完成实验任务。

②实验任务2-I

为了使仿真结果便于打印,这里修改了COUNT值为6,也即在一个大的计数周期内,只扫描一遍(实际实现时需要动态扫描多次,如同实验任务1,产生稳定显示,只需把COUNT值加大即可)。由波形可见,随着大计数周期的增加,依次产生012345-123450-234501-345012-450123-501234-012345 ……,这样便实现了循环移位。实验室实测时,加大COUNT值为5000,观察到稳定持续的周期循环移位的数码显示,完成实验任务。

六.故障及问题分析

1.频率设置问题

当频率设置过高时,计数周期将大大增加,每个周期内的扫描次数也增加,但考虑到人眼的分辨能力,频率只需大于300Hz即可,过大将增大系统开销,故采用2kHz分频器。

2.触发问题

初始编写代码时,误将COUNT计数器放入p3进程中,导致触发逻辑错误,大周期计数不工作,显示数码不能移位。后将模6和模5000两个计数器同时放入p2进程,统一使用一个时钟边沿触发,这样符合了同步时序电路设计的基本思想,触发正确,显示数码才正常移位。

3.逻辑实现问题

实验任务2-II中,为节省硬件开销,摈弃使用过多CASE语句产生大量数据选择器的穷举法,采用一个加法器和一个减法器代替,小周期计数器控制每位数码的显示,大周期计数器控制数码的移位,加法器实现左移出,减法器实现右移入,综合起来实现实验任务要求。逻辑分析包括硬件分析均无问题,但实际下载到电路板上实现时,部分移位出现乱码。在实验室规定的时间内没能调试成功,真是遗憾。分析问题可能出在移位时间的选择上,需要再从仿真波形着手,仔细分析逻辑中的小BUG。

七.本实验总结与结论

1.经过逻辑分析,编写VHDL代码,然后调试,进行波形仿真,最后下载到实验板实现,一系列工序之后,成功实现了本实验要求的比做任务1和选作任务2-I,选作任务2-II逻辑上稍有问题,还需进一步改进编码,仿真测试。

2.进行数字电路实验,理论分析是十分重要的一环,只有逻辑分析透彻无误了,才能用语言进行描述,进而用硬件实现。这次实验让我对VHDL这样一门硬件描述语言有了更加深刻的认识。语言是描述设计者逻辑思想的,有什么样的逻辑思维就会产生什么样的代码,换句话说,逻辑思维错误将直接导致描述错误,进而不能实现数字逻辑。应该着重优化逻辑思维,才能写出优秀的硬件代码。

3.硬件描述语言的学习,不同于一般编程语言的描述,它没有汇编那样深入硬件最底层,但从硬件抽象出来的逻辑却与硬件密不可分。编写硬件描述代码,不仅要符合基本编程语言的规范,更应该时时刻刻联系实现功能的硬件,理解时序和组合的关系,理解同步和异步的差异,理解进程和信号的流程等等,这样才能使写出的代码效率更高。

八.学期总结

1.这学期开始了数字电路与逻辑设计课程,从理论课堂学习基本设计理论到实验课动测试数字电路参数、编写VHDL代码实现逻辑功能,我对数字电路设计与实现的基本思想方法有了初步的了解,为以后进一步的学习和应用到通信等系统打下了扎实的基础。

2.在数字电路应用日趋广泛的今天,学习基本数字电路理论和实现方法有十分重要的意义。而软件和硬件融合的趋势愈发明显,实验课开始VHDL编程也是很有意义的。理论分析有助于优化和提升逻辑思维能力,动手操作有利于锻炼实践能力。这两方面的训练都是很有益处的。

3.实验课使得我对课堂讲授的理论知识有了更加深刻的认识和体验,也让我体会到了数字电路的强大功能。我喜欢实验课中那种提出问题,分析逻辑,仿真验证,具体实现这一过程。尽管实验中困难也不少,但纠错和分析解决问题的过程总给人带来快乐,特别是经过长时间的思考,最终用电路板实现那些有趣的逻辑功能那一刹那,心中总是无比欣喜!

九.参考文献

[1] 数字电路与逻辑设计实验教程,北京:北京邮电大学电路中心,20##

[2] 刘培植等.数字电路与逻辑设计,北京:北京邮电大学出版社,2009

<报告结束>

-

单片机c语言版数码管动态显示实验报告

数码管动态显示实验一实验要求1在Proteus软件中画好51单片机最小核心电路包括复位电路和晶振电路2在电路中增加四个7段数码管共…

-

数码管动态显示实验报告

实验四数码管动态显示实验一一实验要求1在Proteus软件中画好51单片机最小核心电路包括复位电路和晶振电路2在电路中增加四个7段…

-

数码管显示实验报告

HUNANUNIVERSITY课程实验报告实验名称学生姓名学生学号专业班级指导老师数码管显示实验20xx1217实验三数码管显示实…

-

实验报告 实验七 八段数码管显示实验

实验七八段数码管显示实验1实验目的1了解数码管动态显示的原理2了解用总线方式控制数码管显示2实验要求利用实验仪提供的显示电路动态显…

-

实验四 七段数码管显示实验报告

实验四七段数码管显示实验一实验目的掌握数码管显示数字的原理二实验内容1静态显示数码管为共阴极通过BCD码译码驱动器CD4511驱动…

- 实验4 指示灯、数码管的中断控制实验报告

-

单片机c语言版数码管动态显示实验报告

数码管动态显示实验一实验要求1在Proteus软件中画好51单片机最小核心电路包括复位电路和晶振电路2在电路中增加四个7段数码管共…

-

机器人控制-数码管动态显示-仿真实验报告

机器人控制课程总结报告机器人控制仿真实验二数码管动态显示姓名李铃年级20xx级系别信息工程学院计科师学号1111000048同组人…

-

实验一_用七段数码管显示简单字符--译码器及其使用 实验报告

用七段数码管显示简单字符译码器及其应用实验报告专业班级20xx级计算机1班学号1137030姓名赵艺湾实验地点理工楼901实验时间…

-

数码管动态显示实验报告

实验四数码管动态显示实验一一实验要求1在Proteus软件中画好51单片机最小核心电路包括复位电路和晶振电路2在电路中增加四个7段…

- 扫描电镜实验报告