FPGA个人学习总结1

1. 综合方面

1) 经综合后:

普通的数据单端输入都会加一个IBUF缓冲器;

数据单端输出有个OBUF缓存器;

时钟输入口会加BUFGP缓冲器;

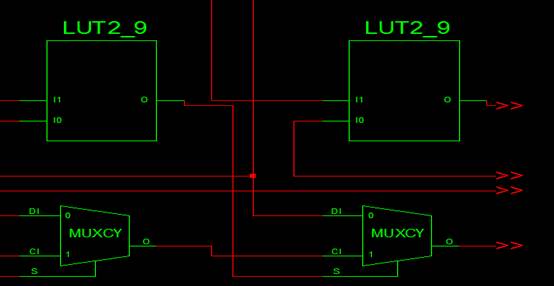

对于4选1的mux,if结构和case结构都只需要一个slice,由MUXF5控制两个LUT

下图为8选一case结构,MUXF6控制两个MUXF5,以两个slices实现8选1,用if结构实现的结构也是一样的

注意一点:

使用View Technology Schematic,来查看最底层的实现形式,即FPGA中的LUT、MUXF5等使用

但有的综合后RTL Schematic相同,Technoligy Schematic不同,而有的又相反(如one bit相加,加括号前后例子),那么我们应该以哪种为最优呢?

如下图:图上下分别为加括号前和加括号后RTL:只有根据实际需要来选择,如信号的先后顺序等等

2.LUT的名字后_数字,那个数字代表什么意思?

LUTa_b:a代表所有输入数据位宽,即输入数据的个数,切勿将位宽理解为“每个输入端口的数据宽度(因每个输入端口是单bit输入);b代表LUT被初始化的状态

3.比较器位宽大小对综合结构的影响

当比较的位宽高于一定位数时,综合会采用进位链结构,如下图:

4.在调用DCM核时,CLKFX_OUT为输出引脚,并且LOCKED_OUT必须勾上,否则波形无法输出,具体步骤参考本文件夹下“dcm核设置”

5.如何判断PCB板上的复位芯片是低复位还是高复位?

将复位芯片的输出连接至LED等,若正常工作后是亮(前提是LED另一端是接地),表示正常工作是高,说明之前是低,即为低复位,不亮则为高复位

6.两种不同下载接口的比较<具体还可参考项23>

1每个FPGA都有两组下载接口JTAG和SPI;

2JTAG中TMS为模式选择,TCK为时钟,TDI和TDO分别为输入输出数据;

3SPI中SS(有的为STB)为片选信号,SCK为时钟信号,另外两根为数据信号;

4通过JTAG下载程序到FPGA:编程管脚跳针要拔掉,掉电后程序也会丢失,即下次上电工作后需要重新下载程序

5通过SPI下载程序到FPGA:先将编程引脚PROG接地,SPI接口断开与FPGA通信,而与flash通信,程序下载到外挂FLASH中,然后将PROG跳针拔掉,FLASH中程序下载到FPGA中

6外部Flash不单是一个裸存储器,它还有SPI接口,图中的SPI接口就是从FLASH的SPI接口中引出来的引脚

7SPI接口是串行同步通信,串口UART是串行异步通信

7.关于示波器

当配置芯片相应寄存器后,观察输出的波形频率时,若出现频率跳动,可以检查示波器上的采样电平是否在波形的中间位置

8.关于复位信号与寄存器声明

寄存器在声明时最好给个初始值,即加载时的值,例如:reg[1:0] a = 2’b00或直接写0;

复位信号不要列在敏感列表中,直接使用if(rst),使rst成为控制信号

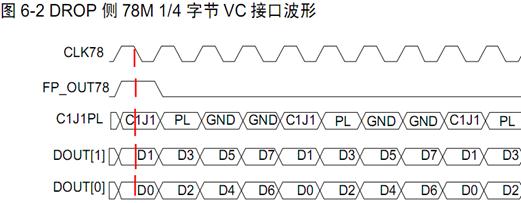

9.如何看出接口读取数据所用的时钟沿

上图可以看出,时钟的下降沿对准数据中心,说明该芯片的此接口是用时钟的下降沿来读取数据的

上图可以看出,时钟的上升沿对准数据中心,说明该芯片的此接口是用时钟的上升沿来读取数据的

故:如果芯片AB之间有走线延迟的话,那么我们在芯片A要用相反的时钟沿送出数据,经过走线延迟后,芯片B对应接口读取数据的时钟沿正好对准到达芯片B的数据的保持时间,即使最大延迟半个周期,也正好对准数据的中心

10.FPGA内部寄存器都是高复位,综合时综合工具会自动为复位信号反相,

若外部芯片为低复位,则可在FPGA设计时,先将复位信号反相,然后使用if(rst)

11.当控制信号高于slice的供应时,可将控制信号转化为数据信号,例如:

If(a) q <= b; 转换为 q <= (a & b)|(!a & q);

If(a) q <= b; 转换为 q <= (a & b)|(!a & q);

else q <= q;

12. 毛刺问题

概念:由于延迟的作用, 多个信号到达终点的时间有先有后, 形成了竞争, 由竞争产生的错误输出就是毛刺

产生条件:在同一时刻有多个信号输入发生改变

出现时间:由于冒险多出现在信号发生电平跳变的时刻, 即在输出信号的建立时间内会产生毛刺, 而在保持时间内不会出现,

13.调用ram

在建立RAM的IP核时,关于是否选择输出寄存器,根据需要!选择一个寄存器,数据则在采到地址后,延迟一个时钟周期,才会输出

14.综合后的寄存器

fd为普通的寄存器;fdr为带复位端的寄存器;fdre为带复位端和使能端得寄存器

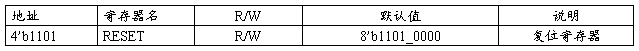

15.寄存器地址注重参数化设计

可以先用define定义相关寄存器的地址参数,然后在运用中使用该参数,如下:

`define reset_addr 4'b1101;

always @(posedge CLK32M or negedge RST)

begin

if(!RST)

begin

SPI_EN <= 8'b0010_0000;

CTL[7:1] <= 7'b1111_101;

RESET <= 8'b1101_0000;

end

else if ( wr_reg == 2'b01 )

case(ADDR)

`spi_en_addr : SPI_EN[7:0] <= DATA[7:0];

`reset_addr : RESET[7:0] <= DATA[7:0];

……….

则

当给寄存器的赋值是某一固定值时,为只读寄存器

16.综合问题

将一输入端口赋值给一个寄存器,再将该寄存器赋值给一个wire型输出端口,则在综合后,输入不会赋值给输出,注意上面的输入输出指的是整个工程的输入输出

解决办法:给输入添加一个ibuf,或者给输出添加一个obuf

有时不必延迟一个时钟周期,而直接将输入赋值给输出

17.时序约束问题

1寄存器到寄存器:过周期约束来设置,一般为实际时钟频率的110%;

2输入管脚到寄存器:通过offset in来设置,一般为半个时钟周期;

由于上游芯片的数据输出和该FPGA的数据输入使用的是同一个时钟,故如果上游芯片的数据输出采用下降沿,那么FPGA的offset in就需采用上升沿;

上游芯片的输出到FPGA寄存器之间的延迟可能不到半个周期;

3寄存器到输出管脚:参考2

18.系统同步接口和源同步接口的区别

1系统同步接口:上游芯片发送数据的时钟和FPGA接收数据的时钟均为系统时钟,或者FPGA发送数据的时钟和下游芯片接收数据的时钟均为系统时钟;

2源同步接口:上游芯片发送数据给FPGA的同时,也发送接收时钟给FPGA,或者FPGA发送数据给下游芯片的同时,也发送接收时钟给下游芯片。

19.在为寄存器分配地址时,常表示为0x…,这样也表示是十六进制!

20.FPGA设计面积与速度

面积指设计所占用的FPGA逻辑资源数目,即触发器FF和查找表LUT的数目

速度指芯片稳定运行时所能达到的最高频率

实际运用中,存在二者之间的平衡

操作有:模块复用、乒乓操作、串并转换以及流水线操作,其中流水线操作比较重要。

21.同步电路与异步电路

区别在于电路触发是否与驱动时钟同步,从行为上将就是所有电路是否在同一时钟沿的触发下处理数据。

以复位电路为例,如果在敏感表中使用negedge rst,则为异步电路

设计原则:

1在多时钟设计中,使设计做到局部同步,即同一时钟驱动的电路要同步于其同一时钟沿(要么均采用上升沿,要么均采用下降沿),即尽量使用单时钟和单时钟沿。

2避免使用门控时钟。门控时钟是指产生时钟使用了组合逻辑。门控时钟相关的逻辑不是同步电路,可能带有毛刺。虽可减小功耗,但随着低功耗FPGA的发展,应尽可能避免使用门控时钟。

3禁止在模块内部使用计数器分频来产生所需的时钟,这样会使时序分析变得复杂,产生较大的时钟漂移,浪费时序裕量,降低设计可靠性,不过对于低速系统采用一两个是没太大问题,可以设计成时钟使能电路,参考本目录下其他资料。

同步电路优点:

1有效避免毛刺,提高设计可靠性;

2简化时序分析过程;

3减少工作环境对设计的影响,异步电路受工作温度、电压等影响,器件延时变化较大,异步电路时序变得更加苛刻,导致芯片无法正常工作,而同步电路只要求时钟和数据沿相对稳定,时序要求相对宽松。

22.单片机与ARM

二者都可通过Intel总线或者SPI或者串口与外部芯片通信,并且通过CS信号来选择要通信的芯片,故允许一定数量的芯片挂在Intel总线上

23.FPGA配置过程及配置方式

配置过程:

1上电后,FPGA若满足相关条件便会自动进行初始化,初始化完成后DNOE信号将变低,并且以后都会是低电平;

2初始化完成后,FPGA会将INIT信号置低,开始清空配置寄存器,清空完后将INIT信号置高;用户可将PROG或者INIT信号置低,来延长清空寄存器时间(注:INIT信号为双向端口);

3清空寄存器后,FPGA对配置模式管脚M[2:0]采样,确定数据配置模式;<001>为SPI模式,<000>为JTAG模式;

4若需重新配置,只需将PROG置低即可,这里不要使用INIT。

配置模式:

1根据芯片能否自动加载配置数据,分为主模式、从模式和JTAG模式;

2主模式,能自动将配置数据从相应外存储器读入到SRAM中,实现内部结构映射,如我们比较常用SPI模式<FPGA是基于SRAM工艺的>;

3JTAG模式,数据直接从TDI进入FPGA,完成相应的配置,该模式用来对芯片进行测试。

<joint test action group>

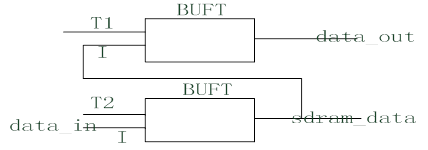

24.关于双向端口的综合结果分析

例如:input[15:0] data_in,

input[3:0] work_state,

input[1:0] cnt_cl,

inout[15:0] sdram_data,

output[15:0] data_out,

assign sdram_data = (work_state == W_WR)? data_in: 16'bz;----------------------------1

assign data_out = (cnt_cl == 2'd2)? sdram_data: 16'bz;------------------------------------2

综合后如下:

语句1综合成下面的BUFT;

当T2=0时,sdram_data输出data_in,当T2=1时,BUFT输出高阻。

需要注意两点:

1T1和T2要存在制约关系;

2不要去追究太多,程序中的式1就综合成下面的BUFT,式2就综合成上面的BUFT,另外,由于data_out不是双向端口,故可将2式改成:

assign data_out = (cnt_cl == 2'd2)? sdram_data: 16'b0;

这样上面BUFT就会用与门代替(本项目中综合后是这样的)

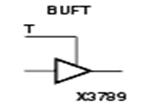

3上面的BUFT就等价于下面的电路:

在功能仿真时,双向端口上如果没有数据,则输出高阻态

25.关于设计中给寄存器赋初值的分析

赋初值后,在程序加载时,会自动为寄存器赋值,避免了在程序初始时刻出现“X”状态

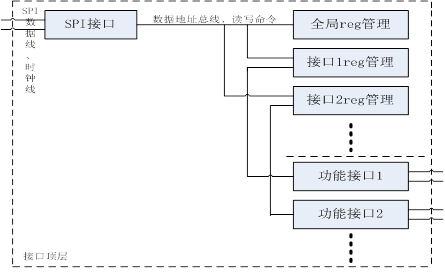

26.SPI系统设计,如下图所示

1 从SPI接口出来的数据地址总线以及读写命令进入各寄存器模块管理,注意数据收发总线是独立的两组总线;

2 数据线数据读写,通过地址线高位来控制,个人认为,用高位地址来产生片选,用片选去控制输出端,未被片选时输出高阻态,同时使用片选控读写信号,未被片选时,不进行读写操作;

3 功能接口只负责数据处理,然后数据送到相关寄存器模块,供外部访问;

4 对于被选中的寄存器管理模块,在写命令下,将从SPI送来的数据写入到功能接口发送寄存器,将数据从功能接口发送出去,或者也可写入其他相应的寄存器,由寄存器地址决定;在读命令下,将功能接口接收的数据写入SPI发送寄存器,从而发送到SPI总线上,注意地址要对应。

27.上电加载管脚PROG_B端的电容的容值要合适,在XC3S250E中为10UF,这样才能正确下载程序!

28.在FPGA上板调试过程中,如果相关信号不正确,考虑方向?

查看PCB板上的时钟芯片的时钟频率是否准确;

29.在问题26中,遇见如下问题:

例如:在接口1reg管理模块中,有个寄存器既输出给SPI接口端数据总线,也输出给功能接口1,在功能接口1中,对输入的数据进行了如下操作

4'b0110 : SERD <= datain [7];

4'b0111 : SERD <= datain[6];

4'b1000 : SERD <= datain[5];

4'b1001 : SERD <= datain[4];

4'b1010 : SERD <= datain [3];

4'b1011 : SERD <= datain[2];

4'b1100 : SERD <= datain[1];

4'b1101 : SERD <= datain[0];

结果导致从SPI接口读出的数据与写入的不一致

解决办法:将进入功能接口1的数据,先缓存,再使用,如下

reg [7:0] datai_delay;

always @( posedge CK4M or negedge RST )

if ( !RST )

datai_delay <= 8'b0;

else if(fame_len == 4'b0000)

datai_delay <= datain;

else

datai_delay <= datai_delay;

再将第一段程序datain换成datai_delay

所以,以后如果多个模块共用一个寄存器的数据,出现错误的话,不妨在某些模块中,将该寄存器数据延迟。

30.在顶层模块中,输出端口由多个模块的输出端口驱动时,综合时报错怎么办?

解决办法:在各个模块使用使能信号将各个驱动信号变成三态使能门

31.FPGA调试方法

对于在一段时间内,只在一个时钟发生变化的信号,可用点灯来测试该信号的正确性

测试程序是:当该信号来时,测试灯状态改变,其他时刻保持不变

同理:对于不循环的计数器的特定也可以这样来测试

程序参考:

reg run_r = 1'b1;

assign run = run_r;

always @ (posedge CLK32M)

if(!rst)

run_r <= 1'b1;

else if(cs_send_ram)

run_r <= 1'b0;

else

run_r <= run_r;

对于整个程序,从时序的后端往前端,逐步测试,逐步判断出错的地方

32.关于总线驱动

在CPLD中,用assign语句直接对信号进行驱动,不需要时钟;

同样在FPGA中对信号进行驱动,也采用一样的方法,不要用时钟去采样,直接用assign

33.关于时钟选取的问题

有两个时钟A和B,若要将它们合并成一个时钟C,从而在设计中使用C时钟沿

方法是:assign C = A & B, 而不要弄成A|B

34.数据选择

问题:使用x条件判断来从a和b中选择一个赋值给c

错误语言:

Wire[7:0] a, b, c;

Wire x;

Assign c = (!x &a) || (x &b);

错误原因:x是一位,a是8位,如何相与?

正确写法:Assign c = x ? a :b

注意:这里的括号并不对多位数据进行逻辑判断(已经综合验证),只有在if等判断语句中才对括号进行逻辑判断

35.FPGA错误排除方法

当得到的信号不正确时,检查该信号在顶层端口是否对应,位宽是否正确

36.FPGA选型

对于中低速信号,选择FPGA主要考虑两个方面:容量和管脚,其次还有价格和速度

容量:看FPGA内部的RAM的大小是否够存数据帧,以及RAM的数目是否够用

管脚: 数目是否够用

对于高速信号,才考虑速度

37. Block RAM 和 Distributed RAM 有什么区别?

1 较大的存储应用,建议用bram;零星的小ram,一般就用dram。但这只是个一般原则,具体的使用得看整个设计中资源的冗余度和性能要求

2 dram可以是纯组合逻辑,即给出地址马上出数据,也可以加上register变成有时钟的 ram。而bram一定是有时钟的。

3 如果要产生大的FIFO或timing要求较高,就用Block RAM。否则,就可以用Distributed RAM。 在Xilinx Asynchronous FIFO CORE的使用时,有两种RAM可供选择,Block memory和Distributed memory。差别在于,前者是使用FPGA中的整块双口RAM资源,而后者则是拼凑起FPGA中的查找表形成。

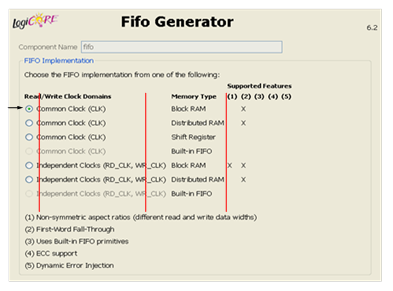

38.FIFO核生成时,如下界面:第一列是选择读写时钟是共用的还是独立的,第二列选择实现FIFO时是使用块RAM还是使用分布式RAM

第一列根据自己需要选择,第二列根据FIFO大小及时序来选择,如37题所述。

注:各项选择用同一个按钮来选择,而非分开选择

39.板上调试时,有时用示波器测量信号,出现问题是:无论量哪个管脚,都出来的是50HZ正弦波。

问题出在:探针的接地断了

40.调试FPGA,信号不输出

当仿真时,某信号不输出或者输出为高阻时,检查方向:该模块内的信号是否与该模块内被调用模块的信号相对应,包括被调用的IP核

例如A模块内有信号a,A模块内调用了模块B,模块B中的信号b与顶层模块A中的信号a相对应,则在A中,调用要正确,即对应为.b(a)

41.FIFO使用总结

如果使用IP核的RST端口,请注意RST是高复位

42.MCU数据双向端口处理

对于双向端口,要通过片选处理成两个独立的输入端口和输出端口,从而方便挂多个器件。方法如处理SDRAM双向数据端口一样。

43.MCU读写时序分析

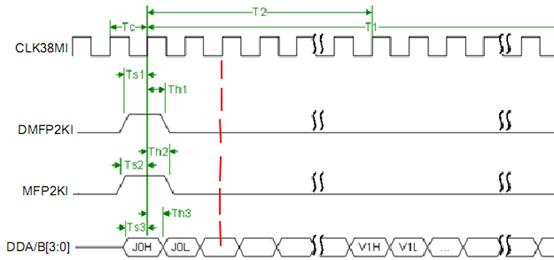

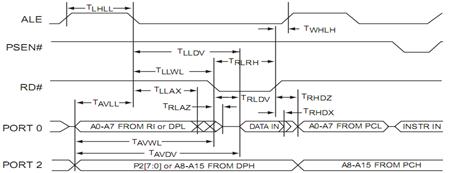

图一

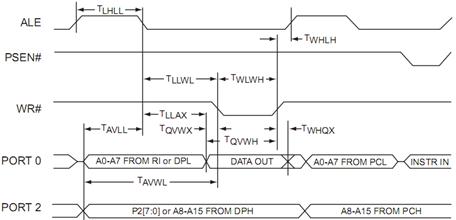

图二

由上图时序分析可知:单片机在ALE下降沿对准地址中心处,故FPGA用ALE下降沿去采样地址;单片机在读信号上升沿读取数据,故FPGA要在读信号下降沿给出数据;单片机在写信号下降沿送出数据,故FPGA在写信号上升沿读取数据。

44.FPGA模块调用问题——可参考项目OPU4中528K(V35网管信息)的FPGA设计

举例:工程中有相同的4组功能端口,它们实现相同的功能。在实现一组功能端口的功能后,不需要将该组模块复制3遍,只需要将该组模块在顶层模块例化三遍,改变例化端口名即可。

如下,P是同一个功能接口,x和y是整个工程的输入输出端口,由于有四组端口,故在例化时要给不同的变量名,而四组端口调用同一模块,故a和b不变。

综合时,例化了多少次,rtl级电路中便有多少个该电路模块,ip核同样例化调用。 input x1,x2,x3,x4;

output y1,y2,y3,y4;

P U1( .a(x1), .b(y1),……);

P U2( .a(x2), .b(y2),……);

P U3( .a(x2), .b(y2),……);

P U4( .a(x4), .b(y4),……);

45.模块间通信

功能相同,但作用不同的模块不要组合成一个模块。例如收发寄存器管理模块要分开,各自与收发功能模块相连,这样避免模块间信号交叉,增加电路复杂度

46. “普通IO管脚作时钟信号输入”问题

在ISE工程设计中,如果某个信号(如时钟信号AC97_CLK)是从非专用时钟引脚输入的,但在设计时又是作为时钟使用的,ISE布局布线时 也会自动将该信号作为全局时钟信号来布线,因其不是从全局时钟脚接入,故出现上述错误,无法布线成功。

如果不使用全局网络,这时可在约束文件(.ucf)中加上如下约束:

NET "AC97_CLK" CLOCK_DEDICATED_ROUTE=FLASE;

这样做是强制ISE不分配全局时钟网络给AC97_CLK,布线就能成功了。

注意:Xilinx的FPGA时钟管脚一定连着全局时钟管脚

47.对于offset in/out设置,上下流芯片时钟要与FPGA对应一致

48.差分信号

差分信号(Differential Signal)在高速电路设计中的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计。

何为差分信号?通俗地说,就是驱动端发送两个等值、反相的信号,接收端通过比较这两个电压的差值来判断逻辑状态“0”还是“1”。

对于高速信号,采用差分信号,可以抗干扰,进入FPGA内部后,通过例化差分转单端模块,将信息转化为单路进行处理,信息的速率不变,信息的内容不变(差分信号两路等值反相)

差分信号一般传输速率较高,因此对信号的完整性有严格要求。要通过UCF语句在FPGA内部添加差分termination。INST <I/O_BUFFER_INSTANTIATION_NAME> DIFF_TERM = "<TRUE/FALSE>"

49.关于保持时间

FPGA内部触发器所需保持时间很短,故一般设计都满足。

以自加1计数器为例,根据其综合RTL逻辑图,需要保持时间小于寄存器D端到Q端的最小时间与加法器组合逻辑延迟最小时间之和。

-

农村信用社个人学习总结范文

我叫xx,是××*市××*县农村信用社的一名职工。为了进一步完善自己的知识结构,不断提高自己的文化素质,不断拓宽自己的知识面,××…

-

个人学习总结范文

为提高自身的管理专业技能,培养创新经营和现代管理意识,促使在工作中进一步更新观念、理清思路。我从20xx年x月开始参加了杭州年代学…

-

大三上学期个人学习总结范文

时光流转,一晃大三上学期马上就要过去了。这是最不平凡的一学期,鲜花伴着汗水,一点一滴,无不倾注着我对于它的默默付出。同时,这又是一…

-

大学生个人学习总结范文

转眼间,到了大一的第一个学期末了,回想起半年前的现在,我还正在备战高考呢,想起高中时对大学的憧憬、追求。光阴如飞箭一般,就好像刚刚…

-

小学生学期个人学习总结范文

时光飞逝,斗转星移。回首这半年的点点滴滴,朝朝暮暮,心中顿生了许多感触。这半年中经历的每一天,都已在我心中留下了永久的印记,因为这…

-

20xx年度小继教个人学习总结

坪寨小学;方敏通过这一年度的学习,我感触很深,受益匪浅,使我学到了以前不了解的很多东西,知道了什么是开放式的课堂教学。老师的教学方…

-

党课个人学习总结

当我跨入大学校门后,我向党组织郑重递交了入党申请书,希望党组织培养我成为一名合格的共产党员。现在我很荣幸能参加贵州师范大学第77期…

-

小学教师继续教育个人学习总结

教学方式是直接影响学习方式形成、完善以及改变的重要因素,是转变学生学习方式的根本。在促进教师教学方式转变的过程中,要求教师做到四变…

-

继续教育个人学习总结.1doc

20xx年继续教育个人学习总结育红小学:何浩通过本年度继续教育培训的学习,使我在教育思想,教育理论及业务能力等方面受益颇多。我深切…

-

个人学习总结

了解发动机的结构我的任务是了解发动机的结构。汽车发动机可以分很多类。按使用燃油分,它们可分为汽油机和柴油机两种;按工作过程分,可分…