一位全加器VHDL的设计实验报告

EDA技术及应用实验报告

——一位全加器VHDL的设计

班级:XXX

姓名:XXX

学号:XXX

一位全加器的VHDL设计

一、实验目的:

1、学习MAX+PLUSⅡ软件的使用,包括软件安装及基本的使用流程。

2、掌握用VHDL设计简单组合电路的方法和详细设计流程。

3、掌握VHDL的层次化设计方法。

二、实验原理:

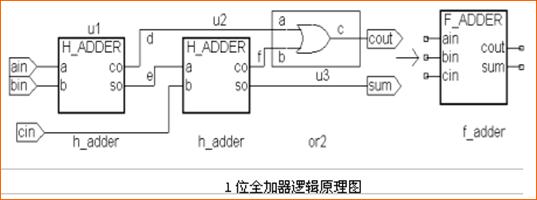

本实验要用VHDL输入设计方法完成1位全加器的设计。1位全加器可以用两个半加器及一个或门连接构成,因此需要首先完成半加器的VHDL设计。采用VHDL层次化的设计方法,用文本编辑器设计一个半加器,并将其封装成模块,然后在顶层调用半加器模块完成1位全加器的VHDL设计。

三、实验内容和步骤:

1、打开文本编辑器,完成半加器的设计。

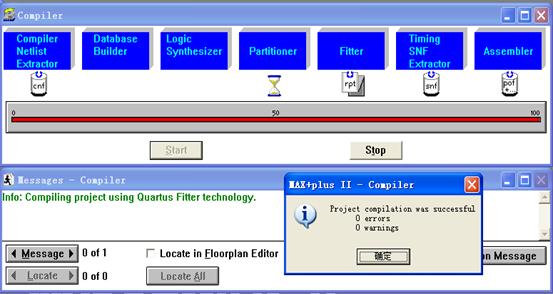

2、完成1位半加器的设计输入、目标器件选择、编译。

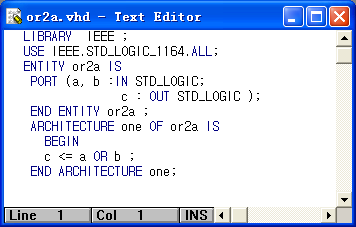

3、打开文本编辑器,完成或门的设计。

4、完成或门的设计输入、目标器件选择、编译。

5、打开文本编辑器,完成全加器的设计。

6、完成全加器的设计输入、目标器件选择、编译。

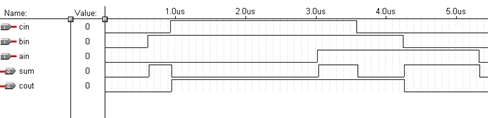

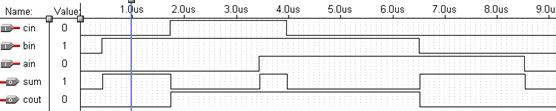

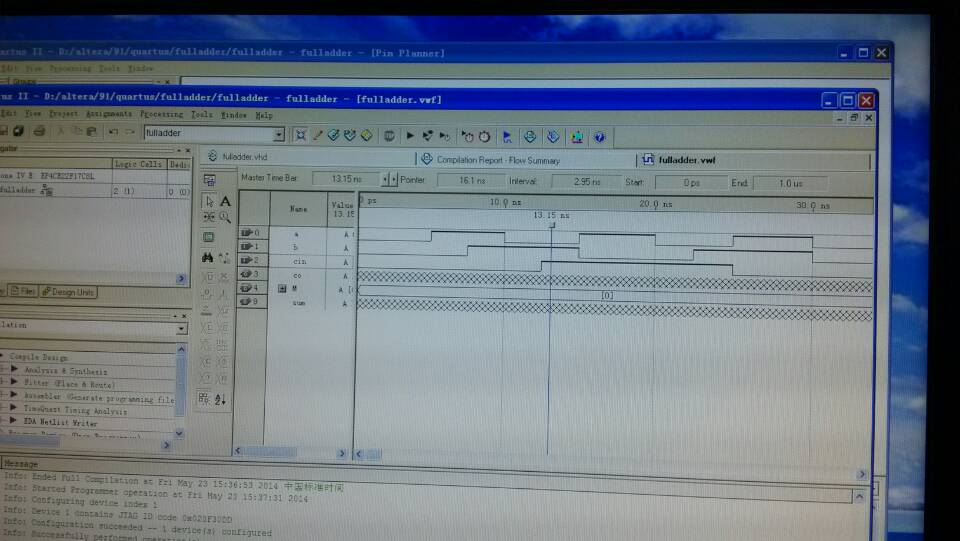

7、全加器仿真

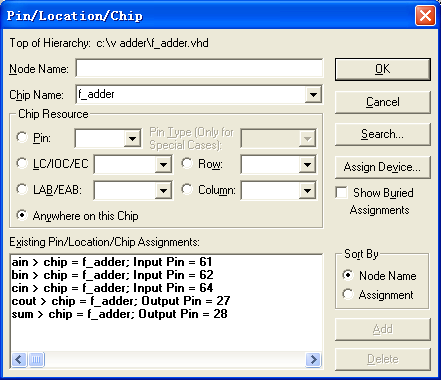

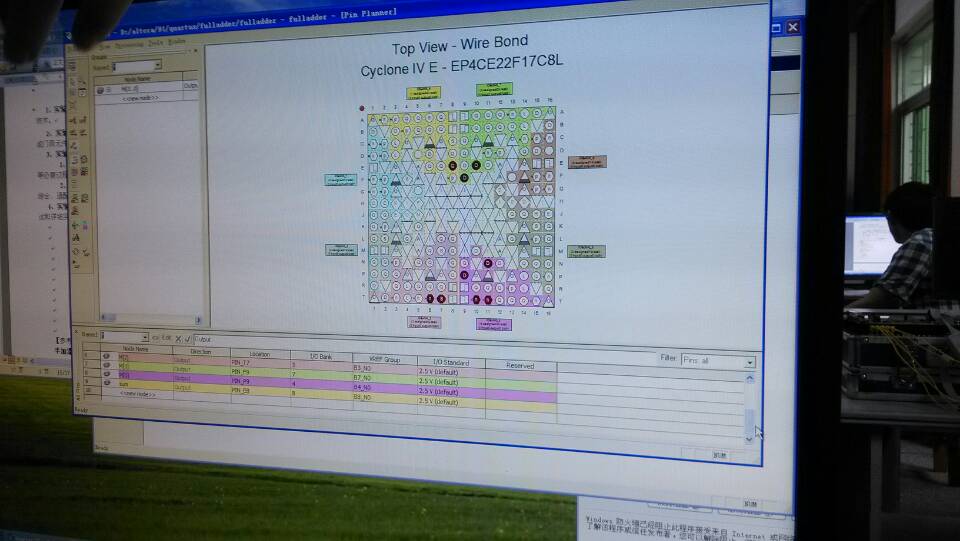

8、全加器引脚锁定

四、结果及分析:

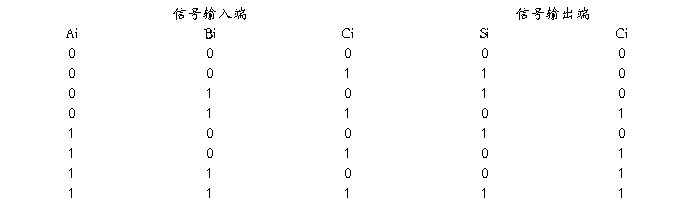

该一位加法器是由两个半加器组成,在半加器的基础上,采用元件的调用和例化语句,将元件连接起来,而实现全加器的VHDL编程和整体功能。全加器包含两个半加器和一或门,1位半加器的端口a和b分别是两位相加的二进制输入信号,h是相加和输出信号,c是进位输出信号。构成的全加器中,A,B,C分别是该一位全加器的三个二进制输入端,H是进位端,Ci是相加和输出信号的和,下图是根据试验箱上得出的结果写出的真值表:

第二篇:1位全加器VHDL文本输入设计

湖南文

湖南文

理学院

姓名: 彭仕林 学号:201111020205 成绩:

组号:

2 学院:

物理与电子科学学院

组号:

2 学院:

物理与电子科学学院

年级: 大三 专业:电子信息科学与技术

课程名称: EDA技术实验 日期:_____________

一、实验名称

1位全加器VHDL文本输入设计

二、实验目的

学习QuartusII软件的应用软件的应用,以及元件例化语句,进一步熟悉VHDL设计技术。

三、实验仪器

QuartusII软件、《E-Play-SOPC教学实验箱》

四、实验原理及原理图

五、实验程序

半加器:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY half_adder IS

PORT (a,b : IN STD_LOGIC;

s,co: OUT STD_LOGIC);

END half_adder;

ARCHITECTURE half1 OF half_adder IS

SIGNAL c,d : STD_LOGIC;

BEGIN

c<=a OR b;

d<=a NAND b;

co<=NOT d;

s<=c AND d;

END half1;

全加器:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY fulladder IS

PORT (a, b, cin: IN STD_LOGIC;

sum, co : OUT STD_LOGIC;

M : out std_logic_vector(3 downto 0)

);

END fulladder;

ARCHITECTURE full1 OF fulladder IS

COMPONENT half_adder

PORT (a,b :IN STD_LOGIC;

s,co:OUT STD_LOGIC);

END COMPONENT ;

SIGNAL u0_co,u0_s,u1_co : STD_LOGIC;

BEGIN

M <= "0001";

U0: half_adder PORT MAP(a,b,u0_s,u0_co);

U1: half_adder PORT MAP(u0_s, cin, sum, u1_co);

co<=u0_co OR u1_co;

END full1;

六、实验步骤

(1)、打开QuartusII软件。

(2)、选择路径。选择File/New Project Wizard,指定工作目录,指定工程和顶层设计实体称。

(3)、添加设计文件。将设计文件加入工程中。单击“Next”,如果有已经建立好的VHDL或者原理图等文件可以在File name中选择路径然后添加,或者选择Add All添加所有可以添加的设计文件(.VHDL ,.Verilog原理图等)。

(4)、选择FPGA器件。Family选择Cyclone II,Available device选EP2C35F484C8,Packge选择Any,Pin Count 选择484,Speed grade选择Any;点击“Next”。

(5)、选择外部综合器、仿真器和时序分析器。默认使用Quartus II自带的工具。

(6)、结束设置。单击“Next”,弹出“工程设置统计”窗口,上面列出了工程的相关设置情况。最后单击“Finish”,结束工程设置。

(7)、建立VHDL原文件。选择菜单“File”à“New…”。VHDL原文件编辑完后,选择File/Save,选择和工程相同的文件名。点击“保存”,文件就被添加进工程当中。

(8)、添加文件到工程中。VHDL原文件编辑完后,选择File/Save,选择和工程相同的文件名。点击“保存”,文件就被添加进工程当中。

(9)、编译。选择Processing/Start/Start Analysis&Synthesis,进行综合。

(10)仿真结果

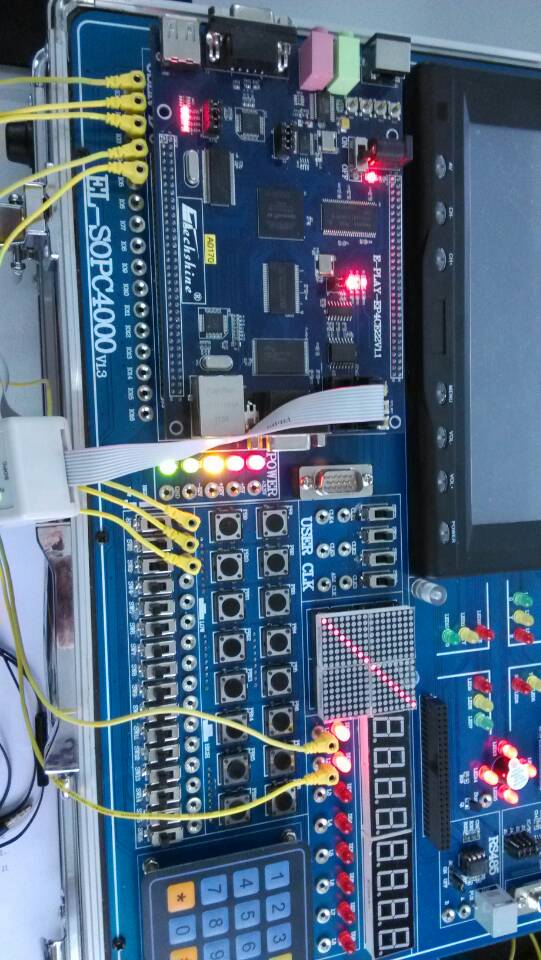

(11)、添加管脚信息。选择Assignments/Assignment Editor在Edit中选择Node Fider,在Node Fider中选择List显示所有节点信息,然后全部选中。为每个节点分配引脚。

(12)、下载。下载可以选择JTAG方式,选择Tool/Programmer,选择JTAG下载方式,选择Add File,添加.sof文件,并选中Program/Configure, 点击“Start”后开始下载。第一次使用下载时,首先点击“Hardware Setup...”,打开Hardware Setup对话框,然后点击Add Hardware,选择USB—方式。

七、实验连线

-

一位全加器实验报告

计算机组成原理课程实验实验题目实验报告正文一律使用A4打印纸打印或手写页眉上标明XXXX课程实验字样页面设置上边距25cm下边距2…

-

一位全加器的实验报告

专业班级20xx级电子2班学号1020xx07姓名周娟EDA技术实验报告实验项目名称在QuartusII中用原理图输入法设计1位加…

-

1位全加器实验报告

浙江万里学院实验报告课程名称可编程逻辑器件应用实验名称全加器的设计专业班级通信姓名黄文龙学号20xx014139实验日期20xx3…

-

计算机实验报告---一位全加器

计算机实验报告一位全加器系别烟大软件工程专业班级学生姓名学生学号20xx25503223指导教师潘庆先一位全加器一实验目的用门电路…

-

全加器实验报告

数电实验报告二组合逻辑电路(半加器、全加器及逻辑运算)一、实验目的1、掌握组合逻辑电路的功能测试。2、验证半加器和全加器的逻辑功能…

-

一位全加器的实验报告

专业班级20xx级电子2班学号1020xx07姓名周娟EDA技术实验报告实验项目名称在QuartusII中用原理图输入法设计1位加…

- EDA实验报告4位全加器

-

全加器实验报告

4位全加器的设计实验报告班级通信122班学号120xx216姓名韦建萍一实验目的熟悉利用QuartusII的原理图输入方法设计简单…

-

EDA全加器实验报告

1位全加器设计实验报告实验目的:用原理图输入法完成半加器和全加器的设计,熟悉和练习QuartusⅡ的应用。实验原理:1位全加器可以…

- EDA实验报告1_8位全加器

-

EDA实验报告(四选一、四位比较器、加法器、计数器、巴克码发生器)

EDA实验报告姓名学号班级实验14选1数据选择器的设计一实验目的1学习EDA软件的基本操作2学习使用原理图进行设计输入3初步掌握器…