数电实验报告(13)

数字电路技术

实验报告

实验十三 乘法器的设计

13.1 实验目的

掌握LPM_ROM的使用;

掌握存储器内容编译器的使用。

13.2 实验任务

利用适当规格的LPM_ROM设计一个九九乘法运算电路,并利用存储器内容编辑器编辑ROM数据。

13.3 实验设备

数字电路与系统实验箱 1台

计算机 1台

Quartus || 软件 一套

13.4实验设计说明

LPM是参数可设置模块库的英文缩写,这些可以图形或硬件描述语言模块形式方便调用的宏模块,使得基于EDA计数的电子设计的效率和可靠性有了很大的提高。本设计中首要的问题是确定LPM_ROM的地址和数据位数以及正确编写.mif文件。假设A和B代表地址端,则A和B分别代表乘数与被乘数,他们的位数直接决定了LPM_ROM的地址和数据位数,若A和B都为0~9位,则其地址和数据都为8位即可。存储器内容编辑器可用于对ROM以及RAM中数据进行读、写,通过该工具可方便地观察存储器数据的变化。

13.5实验原理

首先我们要知道LPM_ROM的逻辑功能:LPM_ROM是可编程的逻辑器件,当用户需要实现特定的逻辑功能时(比如实现九九乘法表),可以事先在LPM_ROM中存入数据,当地址端输入地址时,可以自动查找该地址端所对应的数据,并在CP信号到来时输出该数据。因此,我们可以事先在LPM_ROM中存入九九乘法表,用A和B分别代表加数与被加数,C代表输出,在CP信号到来的时候,输出A与B乘积的结果。

13.6实验过程

首先编写九九乘法表,并保存;

画图,并且把管脚分别定义为地址端和输出端;

管脚分配,并编译;

下载到实验箱,并调试功能;

13.7、实验现象

在输入乘数与被乘数后,当CP信号到来时,输出为十六进制数,并且与九九乘法存入的数据对应。

13.8实验结论

利用LPM_ROM可以实现九九乘法表的功能,不仅如此,还可以实现更多位数的乘法运算。

第二篇:数电实验报告(一)

数字电路实验设计报告

实验名称:组合逻辑研究(一)——QuartusⅡ软件的使用

实验目的:

1. 学会使用QuartusⅡ软件,运用该软件设计电路原理图。

2. 学会用语言设计电路原理图,并会对设计图进行功能和时序仿真。

3. 学会从QuartusⅡ软件中下载原理图到FPGA,测试电路功能。

实验仪器:

1.计算机 1台

2.数字电路实验板 1块

实验内容:

1. 利用软件,用原理图输入的方法实现三变量多数表决器电路,进行功能和时序仿真,记录仿真波形。

2. 利用QuartusⅡ软件,用VHDL文本输入的方法实现一位全加器电路,进行功能和时序仿真,并下载入FPGA,在试验箱上测试其电路功能。

设计过程及仿真结果:

1. 三变量多数表决器原理图

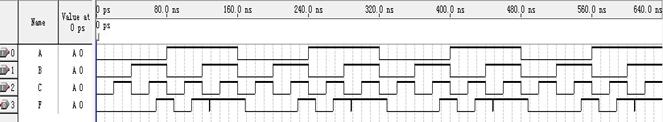

功能仿真波形

时序仿真波形

2. 一位全加器的VHDL语言描述

entity add1 is

port(

A,B,C: in bit;

D,S: out bit

);

end add1;

architecture one of add1 is

begin

S<=A XOR B XOR C;

D<=((A XOR B) AND C) OR (A AND B);

end one;

一位全加器功能真值表

验证其功能

功能仿真波形

时序仿真波形

实验结果分析:

(1)由仿真结果可以看出,三变量多数表决器电路原理图及一位全加器的VHDL语言描述正确。

(2)由仿真结果可知,功能仿真时对信号的输入没有延迟,而时序仿真时,当多个输入信号在同一时刻处同时发生变化时,此时电路存在竞争,会有冒险,故从仿真图上可以看到毛刺。

-

数电实验报告

数电实验报告姓名所在学院专业班级学号日期目录一实验目的2二电路设计与验证2一用加法器实现2位乘法电路21任务分析22方案及结构设计…

-

数电实验报告

数电实验报告班级学号姓名班内序号20xx年5月30日一实验内容及要求一Quartus原理图输入法设计1用逻辑门设计实现一个半加器仿…

-

数电实验报告1

实验一门电路逻辑功能及测试一实验目的1熟悉门电路逻辑功能2熟悉数字电路学习机及示波器使用方法二实验仪器及材料1双踪示波器2器件74…

-

数电课程设计实验报告

目录汽车尾灯控制电路设计第一章设计指标3设计指标3第二章系统概述321设计思想322可行性论证523各功能的组成524总体工作过程…

-

数电实验报告

北京邮电大学数字电路与逻辑设计实验实验名称学班姓学实验报告QuartusII原理图输入法设计与实现院级名号一实验名称Quartus…

-

数电实验报告

北京邮电大学数字电路与逻辑设计实验实验名称学班姓学实验报告QuartusII原理图输入法设计与实现院级名号一实验名称Quartus…

-

数字电路实验报告3

暨南大学本科实验报告专用纸课程名称数字逻辑电路实验成绩评定实验项目名称三态门特性研究和典型应用指导教师实验项目编号08060038…

-

数电实验报告

数电实验报告一实验要求实验目的1熟悉用QuartusII原理图输入法进行电路设计和仿真2掌握QuartusII图形模块单元的生成与…

-

北京邮电大学数电实验一实验报告

北京邮电大学信息与通信工程学院北京邮电大学数字电路与逻辑设计实验学院信息与通信工程学院班级作者学号北京邮电大学信息与通信工程学院实…

-

数字电视基础与检测第五次实验实验报告(含图片、数据)

实验报告课程名称:_数字电视基础与检测____________指导老师:__陈鹏飞_____成绩:________________…

-

数电实验总结心得

数字电子技术实验总结心得数字电子技术是一门理论与实践密切相关的学科,如果光靠理论,我们就会学的头疼,如果借助实验,效果就不一样了,…