电子秒表实训报告

《电子技术》

课程设计报告

摘 要

秒表应用于我们生活、工作、运动等需要精确计时的方面。它由刚开始的机械式秒表发展到今天所常用的数字式秒表。秒表的计时精度越来越高,功能越来越多,构造也日益复杂。

本次数字电路课程设计的数字式秒表的要求为:显示分辨率为1s/100,外接系统时钟频率为100KHz;计时最长时间为1h,六位显示器,显示时间最长为59m59.99s;系统设置启/停键和复位键。复位键用来消零,做好计时准备、启/停键是控制秒表起停的功能键。

针对上述设计要求,我们先前往校图书馆借阅了大量的数字电路设计方面的书籍,以及一本电子元件方面的工具书,以待查阅各种设 计中所需要的元件。其次安装并学习了数字电路设计中所常用的Multisim仿真软件,在课程设计过程的电路图设计与电路的仿真方面 帮助我们发现了设计电路方面的不足与错误之处。

工作安排方面:我们首先在课程设计的要求下设计出了数字式秒表的整体电路框图。其次我们对每个单元电路进行设计分析,对其工作原理进行介绍,最后使用Multisim软件画出单元电路,并在可能情况下对其进行仿真实验。完成了单元电路设计分析之后,进行总电路的拼接与调试,最后对总电路图进行分析,写出结论。完成总电路的设计与分析之后,对资料与设计电路进行整理、排版,完成课程设计报告。

关键字:555定时器 十进制计数器 六进制计数器 多谐振荡器

Abstract

A stopwatch used in our life, work, requires precise timing of movement and so on. Mechanical stopwatch to it by the beginning of the digital stopwatch in common use today. Stopwatch timing accuracy is higher and higher, more and more, the structure is increasingly complex.

The digital circuit course design of digital stopwatch for: according to a resolution of 1 s / 100, the external system clock frequency of 100 KHZ. Timing the longest time of 1 h, six display, display the longest time of 59 m59. 99 s; System setup and reset button to start/stop key. Reset button is used to zero suppression, prepared to timing, start/stop key is to control the stopwatch start-stop function keys.

According to the above design requirements, let's go to the school library borrowing books, a large number of digital circuit design and an electronic component reference books, for access to a variety of needs in the design of components. Second setup and learning Multisim simulation software commonly used in digital circuit design, circuit diagram in the process of course design of design and circuit simulation to help us find the deficiency of the design circuit and error.

Work schedule: we first at the request of the course design of design out of the overall circuit diagram of the digital stopwatch. Secondly we design analysis of each unit circuit, its working principle were introduced, finally using the Multisim software to draw the unit circuit, and where possible on the simulation experiment. After completed the unit circuit design and analysis, splicing and commissioning of total circuit, finally analyze the total circuit diagram, write a conclusion. After finished the total circuit design and analysis, materials and design circuit for sorting, layout, complete curriculum design report.

Key words: 555 timer decimal counter six hexadecimal multivibrator

目 录

第一章 总电路工作原理............................................6

第二章 方案设计与论证............................................7

第三章 单元电路设计与参数计算...................................8

3.1 时钟脉冲发生和控制电路...................................8

3.2 设计十进制加法计数器......................................9

3.3 设计六进制加法计数器.....................................10

3.4 启动和停止电路...........................................11

3.5 清零电路设计.............................................12

第四章 Multisim软件仿真结果.......................................13

第五章 心得体会..................................................14

参考文献..........................................................15.

附录...............................................................15

附录一 总电路......................................................15

附录二 元器件清单..................................................16

任务书

第一章总电路工作原理

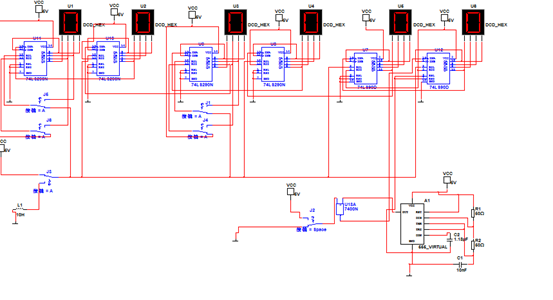

电路通过555多谐振荡器产生的100Hz时钟脉冲与启动与暂停电路与非后输入到第一个计数器即0.01s位的74LS90十进制计数器使其进行频率为100Hz的十进制加法运算。并进位至下一位0.1s位的十进制加法计数器,频率缩减为10Hz。以此类推依次进位至最高位,并以6个LED数码管将计数器输出的信号显示出来。当“启动/停止”开关处于低电平时计数器处于保持状态,即暂停;当开关处于高电平时,计数器继续正常工作。而清零开关为高电平时,所有计数器清零;处于低电平时所有计数器可正常工作。

第二章 方案设计与论证

总体分析:

图1-1 方案设计图

如图1-1所示,该电路需要2个六进制和4个十进制的加计数器,一个555定时器组成的多谐振荡器,RS触发器启动停止电路。由555多谐振荡器产生100Hz的时钟脉冲作为脉冲源(即0.01s为周期),通过与启动停止电路的输出与非后作为信号源输入至第一个十进制计数器即0.01s位的计数器。然后进位至0.1s位的十进制加计数器,以此类推逐个进位。以此实现显示分辨率为1s/100,计时最长时间为1h,六位显示器,显示时间最长为59m59.99s,最后通过6个译码显示LED数码管输出。

第三章 单元电路设计与参数计算

3.1时钟脉冲发生和控制信号

由集成电路定时器555与RC组成的多谐振荡器产生矩形脉冲:

暂稳状态的脉冲宽度tp1,即uc从(1/3)Ucc充电上升到(2/3)Ucc所需的时间:

tp1≈(R1+R2)Cln2=0.7(R1+R2)C

脉冲宽度tp2,即uc从(2/3)Ucc放电下降到(1/3)Ucc所需的时间:

tp2≈R2Cln2=0.7R2C

振荡周期: T=tp1+tp2=0.7(R1+2R2)C

因此,令R1=2KΩ,R2=5KΩ,输出频率为100Hz即T=0.01s,则可求出C=1.19μF。得下图2-1中100Hz的555定时器构成的多谐振荡器:

图3-1

从3脚(OUT)输出脉冲信号。

3.2设计十进制加法计数器

使用74LS90芯片实现十进制加法计数器。

74LS90 是异步二—五—十进制加法计数器,它既可以作二进制加法计数器,又可以作五进制和十进制加法计数器。通过不同的连接方式,74LS90可以实现四种不同的逻辑功能;而且还可借助R0(1)、R0(2)对计数器清零,借助S9(1)、S9(2)将计数器置9。其具体功能详述如下:

(1)计数脉冲从CP1输入,QA作为输出端,为二进制计数器。

(2)计数脉冲从CP2输入,QDQCQB作为输出端,为异步五进制加法计数器。

(3)若将CP2和QA相连,计数脉冲由CP1输入,QD、QC、QB、QA作为输出端,

则构成异步8421码十进制加法计数器。

(4)若将CP1与QD相连,计数脉冲由CP2输入,QA、QD、QC、QB作为输出端,

则构成异步5421码十进制加法计数器。

(5)清零、置9功能。

a) 异步清零

当R0(1)、R0(2)均为“1”;S9(1)、S9(2)中有“0”时,实现异步清零功能,即QDQCQBQA=0000。

b) 置9功能

当S9(1)、S9(2)均为“1”;R0(1)、R0(2)中有“0”时,实现置9功能,即QDQCQBQA=1001。

在这里我们用到的是将CP2和QA相连,计数脉冲由CP1输入,QD、QC、QB、QA作为输出端,构成的异步8421码十进制加法计数器。如下图2-2:

图3-2

3.3设计六进制加法计数器

常用异步集成计数器74LS290。其中,S9(1)、S9(2)称为置“9”端,R0(1)、R0(2)称为置“0”端;CP0、CP1端为计数时钟输入端,Q3Q2Q1Q0为输出端,NC表示空脚。

74LS290具有以下功能:

置“9”功能:当S9(1)=S9(2)=1时,不论其他输入端状态如何,计数器输出Q3 Q2 Q1 Q0=1001,而(1001)2=(9)10,故又称为异步置数功能。

置“0”功能:当S9(1)和S9(2)不全为1,并且R0(1)=R0(2)=1时,不论其他输入端状态如何,计数器输出Q3 Q2 Q1 Q0=0000,故又称为异步清零功能或复位功能。

计数功能:当S9(1)和S9(2)不全为1,并且R0(1)和R0(2)不全为1时,输入计数脉冲CP,计数器开始计数。计数脉冲由CP0输入,从Q0输出时,则构成二进制计数器;计数脉冲由CP1输入,输出为Q2Q1Q0时,则构成五进制计数器;若将Q0和CP1相连,计数脉冲由CP0输入,输出为Q3Q2Q1Q0时,则构成十进制(8421码)计数器;若将Q3和CP0相连,计数脉冲由CP1输入,输出为Q3Q2Q1Q0时,则构成十进制(5421码)计数器。因此,74LS290又称为“二—五—十进制型集成计数器”。

图3-3

3.4启动与停止电路

如图:

图3-4

当开关接低电平即接地时,通过与时钟脉冲与非,使计时器处于暂停状态;当开关接高电平即VCC时,通过与时钟脉冲与非,使计时器处于启动状态。因此这个开关为“启动/暂停”按键。

3.5清零电路设计

如图:

图3-5

当开关接高电平时,所有计数器清零;当开关接低电平时,所有计数器正常工作。

第四章 Multisim软件仿真结果

仿真结果如图4-1:

图4-1仿真

图 4-2 暂停

图4-3 清零

第五章 心得体会

在设计实践的过程中,我深深的体会到必须要有扎实的知识基础,要熟练地掌握课本上的知识,这样才能对试验中出现的问题进行分析解决。在整个电路的设计过程中,花费时间最多的是利用Multisim 仿真,因为以前没有学过这个软件,所以我们要从头学起,自行摸索的学习。我们在各个单元电路的连接上花费了大量时间。我们在设计时曾做出了两套方案以及仿真电路,我们仔细比较分析其原理以及可行的原因,这才确定了我们的电路。实习过程中,我深刻的体会到在设计过程中,要考虑到各个元器件的功能和特性,要翻阅大量资料,参考别人的经验,只有这样才能把自己的电路设计的成功。

通过这次对数字式秒表的设计与制作,让我了解了设计电路的程序,也让我了解了关于数字秒表的原理与设计理念。在此次的数字秒表设计过程中,我更进一步地熟悉了芯片的结构、管脚图、功能表及掌握了各芯片的工作原理和其具体的使用方法。而且这些知识是对我们大学生来说十分宝贵的实践经验,是无法在课堂上获得的,是现今社会最重视的同时也是我们最需要提高的部分。

在设计电路中,完成电路图只是完成了设计的一小部分,更加困难的是对电路的验证和纠错,在这过程中我接触到了很多未接触过的检查方法和思想。在电路的仿真过程中出错的主要原因都主要是接线的错误所引起的。接线的时候一定要细心,不要接错,同时也要学会如何判别芯片的功能,要是芯片不具备要求的功能,或者,不匹配,即使接线再正确也出不来结果。对自己的设计要仔细考虑,是否可行,尤其是进位输出,着重看看进位的CP脉冲是否正确等。

总体来说,通过这次课程设计学习,我越发感觉电子设计不是死板的东西,是有很大科学性与艺术性的。不同芯片的使用,不同的接线方法,不同的变量,不同的实现思路,经过组合后几乎可以称之为艺术。这次课程设计使我对各种电路都有了大概的了解,也学会了常用EDA软件的使用,在平时的理论学习中遇到的问题都一一解决,加深了我对专业的了解,培养了我对学习的兴趣,为以后的学习打下了好的开端,我受益匪浅。同时,让我明白:电子设计容不得纸上谈兵,只有自己动手实际操作才会有深刻理解,才会有收获,所谓“千里之行,始于足下”,这次课程设计最大的意义在于让我们迈出了通往工程师的第一步。再次感谢课设指导老师的指导和帮助过我的同学们。

参考文献

[1]《实用电子电路手册(数字电路分册)》.北京:高等教育出版社,1991

[2]郁汉琪.数字电子技术实验及课题设计. 北京:高等教育出版社,1995

[3]康华光.电子技术基础:模拟部分. 北京:高等教育出版社,1988

[4]彭介华.电子技术课程设计指导[M].北京:高等教育出版社

[5]孙梅生,李美莺,徐振英. 电子技术基础课程设计[M]. 北京:高等教育出版社

[6]梁宗善. 电子技术基础课程设计[M]. 武汉:华中理工大学出版社

[7]张玉璞,李庆常. 电子技术课程设计[M]. 北京:北京理工大学出版社

[8]谢自美.电子线路设计·实验·测试(第二版)[M].武汉:华中科技大学出版社

[9]http://www.icbase.com

[10]魏立君,韩华琦.COMS4000系列60种常用集成电路的应用.北京:人民邮电出版社,1993

附录

附录一:电子秒表总电路

附录二:元件清单

-

电子实习报告范文

电子实习报告范文实习目的与要求读了三年的大学,然而大多数人对本专业的认识还是寥寥无几,在通信原理与仪器周围缠绕不定。由于社会经验的…

-

电工电子实习报告范文

电工电子实习报告学院环境与化学工程学院专业班级测仪121姓名胡兴学号58012120xx指导老师江媛实验名称收音机的组装与焊接实习…

-

电子信息工程专业实习报告范文

20xx年x月,学校组织的实习学习虽然只有短短的一个多月时间,但是我以100%的工作态度来对待,同时由于学习的心态来面对,而经历了…

-

电工电子实习报告范文

编辑点评:电工电子实习不仅能锻炼自己动手实践能力和技巧,而且还可以提高解决问题的能力。下面是沪江网小编收集的有关电工电子实习报告,…

-

电子厂实习报告范文

实习报告学院班级姓名学号日期20xx227一实习时间20xx11820xx225二实习地点嘉联益昆山有限公司三实习目的1锻炼自己的…

-

电子秒表实验报告

电子技术设计性实训报告学号211002146姓名邱富烨同组人夏文彬班级指导老师林雪健日期20xx0907目录一实训目的3二设计功能…

-

电子秒表设计实验报告

淮阴工学院数字电子技术课程实验期末考核20xx20xx学年第2学期实验名称电子秒表电路的设计班级学号姓名学院专业系别指导教师成绩2…

-

电子秒表实验报告

课程设计综合实验报告20xx20xx年度第1学期名称VHDL语言与系统设计题院系电气与电子工程学院班级信息10011002班学号学…

-

60s电子秒表综合性实验报告

重庆交通大学信息科学与工程学院综合性实验报告姓名XX学号XXXXXXXXXX班级实验项目名称60s电子秒表实验项目性质设计性实验实…

-

数字电路 电子秒表实验报告

实验二电子秒表一、实验目的1、学习数字电路中基本RS触发器、单稳态触发器、时钟发生器及计数、译码显示等单元电路的综合应用。2、掌握…

-

电子秒表课程设计报告

电子秒表1设计课题任务及指标1通过本设计的选题方案论证设计计算安装调试资料整理撰写设计报告等环节初步掌握电子工程设计方法和组织实施…