计算机组成原理实验报告3

实验报告

实验报告

学院(系)名称:计算机与通信工程学院

第二篇:计算机组成原理实验4.3_实验报告

学生实验报告

学 院:软 件 学 院

专 业:软 件 工 程

年 级:2010级

学 号: 24320102202460

学生 姓名:高伟

同组学生姓名:何建明

实验课程名称:计算机组成原理实验

实验 名称:具有DMA控制功能的总线接口实验

指导 教师:曾文华、蔡艺军、廖凌宇

实验 时间: 2012.4.9 19:00---21:00

实验 地点:漳州校区生化楼603

20##年4 月18日

一、 实验目的与要求[ZWH1]

1.掌握 DMA 控制信号线的功能和应用.

2.掌握在系统总线上设计 DMA 控制信号线的方法.

二、 实验设备

1、TD-CMA教学实验系统1台(通过USB串行接口与PC微机相连)

2、PC微机1台

三、 实验原理[a2]

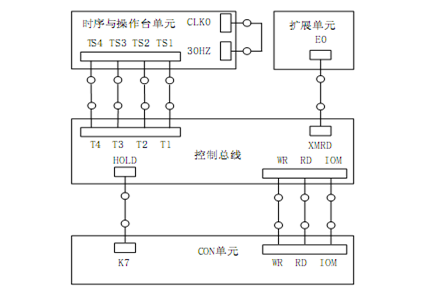

有一类外设在使用时需要占用总线,其中的典型代表是 DMA 控制机.在使用这类外设时, 总线的控制权要在 CPU 和外设之间进行切换,这就需要总线具有相应的信号来实现这种切换, 避免总线竞争,使 CPU 和外设能够正常工作.下面以 DMA 操作为例,设计相应的总线控制信 号线.实验原理图如图 4-3-1 所示

图 1 实验原理图

进行 DMA 操作时,外设向 DMAC(DMA 控制机)发出 DMA 传送请求,DMAC 通过总线 上的 HOLD 信号向 CPU 提出 DMA 请求.CPU 在完成当前总线周期后对 DMA 请求做出响应. CPU 的响应包括两个方面,一方面让出总线控制权,一方面将有效的 HALD 信号加到 DMAC 上,通知 DMAC 可以使用总线进行数据传输.此时 DMAC 进行 DMA 传输,传输完成后,停 止向 CPU 发 HOLD 信号,撤消总线请求,交还总线控制权.CPU 在收到无效的 HOLD 信号后, 一方面使 HALD 无效,另一方面又重新开始控制总线,实现正常的运行.

如图 4-3-1 所示,在每个机器周期的 T4 时刻根据 HOLD 信号来判断是否有 DMA 请求,如 果有,则产生有效的 HALD 信号,HALD 信号一方面锁死 CPU 的时钟信号,使 CPU 保持当前 状态,等待 DMA 操作的结束.另一方面使控制缓冲,数据缓冲,地址缓冲都处于高阻状态, 隔断 CPU 与外总线的联系, 将外总线交由 DMAC 控制. DMA 操作结束后, 当 DMAC 将 HOLD 信号置为无效,DMA 控制逻辑在 T4 时刻将 HALD 信号置为无效,HALD 信号一方面打开 CPU 的时钟信号,使 CPU 开始正常运行.另一方面把控制缓冲,数据缓冲和地址缓冲交由 CPU 控 制,恢复 CPU 对总线的控制权.

数据缓冲和地址缓冲由数据总 在本实验中, 控制缓冲由写在 16V8 芯片中的组合逻辑实现, 线和地址总线左侧的 74LS245 实现. 以存储器读信号为例, 体现 HALD 信号对控制总线的控制.

首先模拟 CPU 给出存储器读信号(置 WR,RD,IOM 分别为 0,1,0) ,当 HALD 信号无效时, 总线上输出的存储器读信号 XMRD 为有效态"0" ,当 HALD 信号有效时,总线上输出的存储器 读信号 XMRD 为高阻态.可以自行设计其余的控制信号验证实验.

四、 实验步骤[ZWH3]

1、实验接线:

图2 实验接线图

2、实验步骤:

① 将时序与操作台单元的开关 KK1,KK3 置为'运行'档,开关 KK2 置为'单拍'档, 按动 CON 单元的总清按钮 CLR,将 CON 单元的 WR,RD,IOM 分别置为"0""1""0" , , , 此时 XMRD 为低,相应的指示灯 E0 灭.使用电压表测量数据总线和地址总线左侧的芯片 74LS245 的使能控制信号(第 19 脚) ,发现电压为低,说明数据总线和地址总线与 CPU 连通.

② 然后将 CON 单元的 K7 置为 1,连续按动时序与操作台单元的开关 ST,T4 时刻控制总 线的指示灯 HALD 为亮,继续按动开关 ST,发现控制总线单元的时钟信号指示灯 T1——T4 保 持不变,说明 CPU 的时钟被锁死.此时 XMRD 为高阻态,相应的指示灯 E0 亮.使用万用表测 量数据总线和地址总线左侧的芯片 74LS245 的使能控制信号(第 19 脚) ,发现电压为高,说明 总线和 CPU 的连接被阻断.

③将 CON 单元的 K7 置为 0,按动时序与操作台单元的开关 ST,当时序信号走到 T4 时刻 时,控制总线的指示灯 HALD 为灭,继续按动开关 ST,发现控制总线单元的时钟信号指示灯 T1——T4 开始变化,说明 CPU 的时钟被接通.此时 XMRD 受 CPU 控制,恢复有效为低,相 应的指示灯 E0 灭. 使用万用表测量数据总线和地址总线左侧的芯片 74LS245 的使能控制信号 (第 19 脚) ,发现电压为低,说明总线和 CPU 恢复连通.

五、 实验结果[ZWH4] 与讨论

实验结果符合预期。

主要说明本实验要达到的目的和具体的要求(实验将实现的功能)

描述本实验的基本原理

给出实验过程中的详细步骤,其中实验接线请列出本实验所接的所有线

给出本实验得到的有关结果和结论,并对有关实验现象进行讨论

-

计算机组成原理实验报告

计算机组成原理实验报告软件学院计算机组成原理实验报告专业班级学号日期学生姓名指导教师计算机组成原理实验报告运算器组成实验一实验目的…

-

计算机组成原理 电子科大技大学 实验报告

课程名称计算机组成原理学院计算机科学与工程专业计算机科学与技术指导教师王学生姓名郭学号实验成绩日期实验报告勇小明20xx06010…

- 计算机组成原理实验报告-存储器

-

计算机组成原理实验报告1

计算机组成原理实验报告1姓名学号教师时间地点机位实验名称数据传送实验一实验目的1理解自然语言形式命令的人工译码过程2学习系统部件和…

-

《计算机组成原理》运算器实验报告

《计算机组成原理》实验报告学院:专业:班级学号:AP0804114学生姓名:实验日期:指导老师:成绩评定:五邑大学信息学院计算机组…

-

计算机组成原理课程设计心得

计算机组成原理课程设计心得计科1004计算机组成原理课程设计是在我们上完计算机组成原理课之后的硬件实践课程,是把组成原理课上的理论…

-

农林大学计算机组成原理课程实习报告模板(新)

福建农林大学金山学院课程名称实习题目姓名系专业年级学号指导教师职称课程实习报告计算机组成原理普通的加减法指令柳继曾机电与信息工程系…

-

计算机组成原理课程设计报告

计算机组成原理课程设计报告课程设计题目计算机组成原理专业名称计算机科学与技术班级20xx240202关童20xx24020xx7张…

-

计算机组成原理课程设计实验报告

计算机组成原理课程设计实验报告学院专业班级学号姓名评分20xx年6月8日实验一一实验名称验证74LS181运算和逻辑功能二实验目的…

-

计算机组成原理课程设计报告

西安科技大学课程设计报告课程名称计算机组成原理课题名称复杂模型计算机的设计专业计算机科学与技术班级计科1001班姓名李用维念文洪吴…

-

《计算机组成原理》运算器实验报告

《计算机组成原理》实验报告学院:专业:班级学号:AP0804114学生姓名:实验日期:指导老师:成绩评定:五邑大学信息学院计算机组…