数字实验四 组合逻辑电路的设计与测试 实验报告

学生实验报告

第二篇:实验三 组合逻辑电路的设计与测试

注:本实验为设计性实验,没有预先设计好实验方案和实验电路的一律不准来做实验。实验前要先检查预习报告。注意划下线部分。

实验三 组合逻辑电路的设计与测试

一、实验目的

掌握组合逻辑电路的设计与测试方法

二、实验原理

1、使用中、小规模集成电路来设计组合电路是最常见的逻辑电路。设计

组合电路的一般步骤如图5-1所示。

图5-1 组合逻辑电路设计流程图

2、 组合逻辑电路设计举例

用“与非”门设计一个表决电路。当四个输入端中有三个或四个为“1”时,输出端才为“1”。

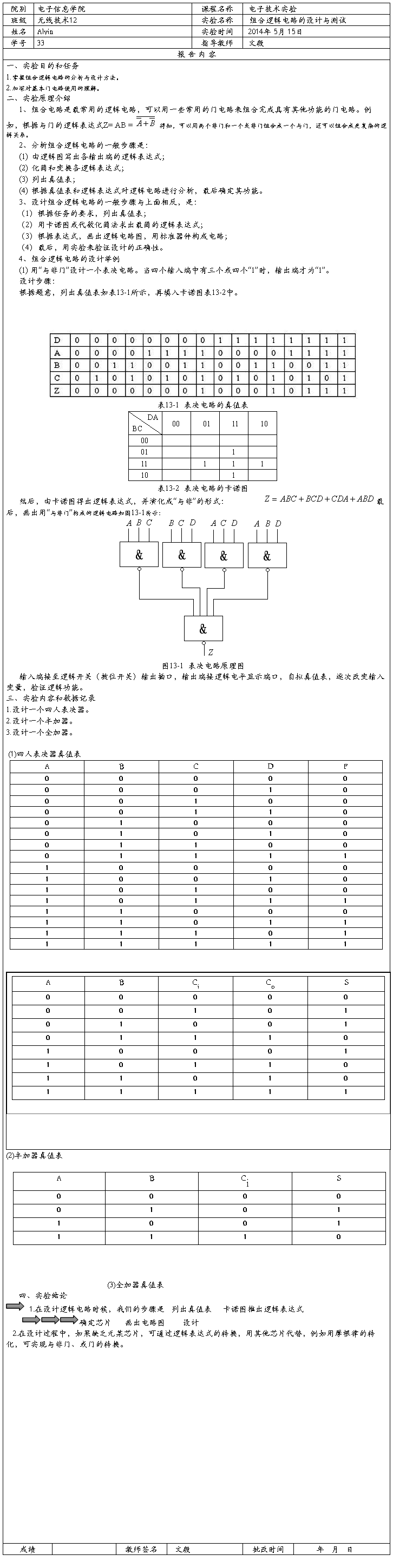

设计步骤:根据题意列出真值表如表5-1所示,再填入卡诺图表5-2中。

表5-1

表5-2

由卡诺图得出逻辑表达式,并演化成“与非”的形式

Z=ABC+BCD+ACD+ABD

=

根据逻辑表达式画出用“与非门”构成的逻辑电路如图5-2所示。

图5-2 表决电路逻辑图

用实验验证逻辑功能

在实验装置适当位置选定三个14P插座,按照集成块定位标记插好集成块CC4012。

按图5-2接线,输入端A、B、C、D接至逻辑开关输出插口,输出端Z接逻辑电平显示输入插口,按真值表(自拟)要求,逐次改变输入变量,测量相应的输出值,验证逻辑功能,与表5-1进行比较,验证所设计的逻辑电路是否符合要求。

三、实验设备与器件

1、 +5V直流电源 2、 逻辑电平开关

3、 逻辑电平显示器 4、 直流数字电压表

3、 CC4011×2(74LS00)共有4个与非门、 CC4012×3(74LS20)4脚与非门、 CC4030(74LS86)共有4个异或门、 CC4081(74LS08)共有4个与门、 74LS54×2(CC4085)与或非门(下图)、 CC4001 (74LS02) 共有4个或非门。

四、实验内容

1、设计一个一位全加器,要求用异或门、与门、或门组成。

2、设计一位全加器,要求用与或非门实现。

从1和2中任选一个来做。要求按本文所述的设计步骤进行,直到测试电路逻辑功能符合设计要求为止。

五、实验预习要求

1、根据实验任务要求设计组合电路,选择好所需要的门电路,并根据所给的标准器件画出逻辑(可参照课本的“全加器”部分的表达式)。

图。

2、画好实验要填写的表格。

3、如何用最简单的方法验证“与或非”门的逻辑功能是否完好?

4、“与或非”门中,当某一组与端不用时,应作如何处理?

六、实验报告

1、列写实验任务的设计过程,画出设计的电路图。

2、对所设计的电路进行实验测试,记录测试结果。

3、组合电路设计体会。

注:四路2-3-3-2输入与或非门74LS54

引脚排列 逻辑图

逻辑表达式

- 电子技术实验报告4—组合逻辑电路的设计与测试

-

组合逻辑电路的设计实验报告

广西大学实验报告纸实验内容指导老师实验名称组合逻辑电路的设计实验目的学习组合逻辑电路的设计与测试方法设计任务用四二输入与非门设计一…

-

实验二 组合逻辑电路分析与设计实验报告

实验二组合逻辑电路分析与设计实验报告姓名李凌峰班级13级电子1班学号13348060一实验数据与相应原理图1复习组合逻辑电路的分析…

-

数电实验报告 实验二 组合逻辑电路的设计

实验二组合逻辑电路的设计一实验目的1掌握组合逻辑电路的设计方法及功能测试方法2熟悉组合电路的特点二实验仪器及材料aTDS4数电实验…

-

组合逻辑电路的设计实验报告

基本知识数字电路根据逻辑功能的不同特点可以分成两大类一类叫组合逻辑电路简称组合电路另一类叫做时序逻辑电路简称时序电路组合逻辑电路在…

-

组合逻辑电路实验报告

实验报告课程名称:数字电子技术基础实验指导老师:樊**成绩:实验名称:组合逻辑电路实验实验类型:设计类同组学生姓名:一、实验目的和…

-

实验二 组合逻辑电路分析与设计.

实验一实验目的组合逻辑电路分析与设计1掌握组合逻辑电路的分析方法与测试方法2掌握组合逻辑电路的设计方法二实验预习要求1熟悉门电路工…

- 电子技术实验报告4—组合逻辑电路的设计与测试

-

数字实验二 组合逻辑电路的分析及设计

实验二组合逻辑电路的分析与设计一、实验目的1、掌握组合逻辑电路的分析与设计方法。2、加深对基本门电路使用的理解。二、实验设备与器件…

-

组合逻辑电路的分析与设计-实验报告

组合逻辑电路的分析与设计实验报告院系电子与信息工程学院班级电信132班组员姓名盖兵134xxxxxxxx邢帅成134xxxxxxx…

-

西工大数电实验报告_实验一TTL集成逻辑门电路参数测试2

实验一TTL集成逻辑门电路参数测试姓名同组一实验目的1加深了解TTL逻辑门的参数意义2掌握TTL逻辑门电路的主要参数及测量方法3认…