Ъ§зжжгЩшМЦБЈИц

ЮяРэгыЕчЦјЙЄГЬбЇдКПЮГЬЪЕМљБЈИц

Ъ§зжжг

ае УћЃК

бЇ КХЃК111102051

зЈ вЕЃКЕчаХ

жИЕМРЯЪІЃК

ГЩ МЈЃК

Ше ЦкЃК

Лљгк51ЕЅЦЌЛњЕФЪ§зжжг

вЛЁЂЧАбд

Ъ§зжжгЪЧВЩгУЪ§зжЕчТЗЪЕЯжЖдЪБЁЂЗжЁЂУыЃЌЪ§зжЯдЪОЕФМЦЪБзАжУЁЃдчвбГЩЮЊШЫУЧШеГЃЩњЛюжаВЛПЩЩйЕФБиашЦЗЃЌИјШЫУЧЕФЩњЛюЁЂбЇЯАЁЂЙЄзїЁЂгщРжДјРДМЋДѓЕФЗНБуЁЃгЩгкЪ§зжМЏГЩЕчТЗММЪѕЕФЗЂеЙЃЌЪ§зжжгЕФЩшМЦвбОЪЧИіПЮГЬЕФЛљДЁЁЃгЩЕчзгЕчТЗЪЕЯжвЛИіздЖЏЪ§зжжгЃЌЭъГЩУыЗжЪБздЖЏЕїНкМАЦфЯрЙиЙІФмЃЌМгЧПбЇЩњЪжЖЏЪЕМљФмСІГЩЮЊКЯЪЪЪзбЁЕФЗНАИжЎвЛЁЃ

Ъ§зжжгЪЧЯжДњМЦЪБЦїЃЌвВПЩгУзїЪБМфПижЦЕФЪБжгдДЁЃЪ§зжжггЩгкЦфОпгазпЪБзМЃЌЯдЪОжБЙлЃЌПюЪНаТгБЃЌИНМгЙІФмЖрЕШгХЕуЖјЪмЕНШЫУЧЕФЛЖгЁЃЩшМЦвЛИіОпгаећЕуБЈЪБЃЌПЩЖдЪБЕФЪ§зжжг ЁЃгЩгкЪ§зжМЏГЩЕчТЗЕФЗЂеЙКЭЪЏгЂОЇЬхеёЕДЦїЕФЙуЗКгІгУ,ЪЙЕУЪ§зжжгЕФОЋЖШ,дЖдЖГЌЙ§РЯЪНжгБэ, жгБэЕФЪ§зжЛЏИјШЫУЧЩњВњЩњЛюДјРДСЫМЋДѓЕФЗНБуЃЌЖјЧвДѓДѓЕиРЉеЙСЫжгБэдЯШЕФБЈЪБЙІФмЁЃШчФжСхЁЂАДЪБздЖЏДђСхЁЂЕШЃЌЫљгаетаЉЃЌЖМЪЧвджгБэЪ§зжЛЏЮЊЛљДЁЕФЁЃвђДЫЃЌбаОПЪ§зжжгМАРЉДѓЦфгІгУЃЌгазХЗЧГЃЯжЪЕЕФвтвхЁЃ

вдЪ§зжЕчзгЮЊЛљДЁЃЌЗжБ№Жд1SЪБжгаХКХЪфГіЁЂУыМЦЪБЯдЪОЁЂЗжМЦЪБЯдЪОЁЂаЁЪБМЦЪБЯдЪОЃЌШЛКѓНЋЫќУЧзщКЯЃЌРДЭъГЩЙІФмЁЃ

ВЂЭЈЙ§БОДЮЩшМЦМгЩюЖдЕЅЦЌЛњжЊЪЖЕФРэНтЁЃ

ЖўЁЂЕчТЗдРэЭМ

гУ51ЕЅЦЌЛњЭЈЙ§74LS138выТыЦїЪЕЯжЖдСљЮЛЙВвѕЦпЖЮЪ§ТыЙмЕФПижЦЃЌШчЯТЭМЃК

Ш§ЁЂдДГЬађ

ГЬађжагУЕНСЫT0ЃЌINT0,INT1Ш§ИіжаЖЯЃЌЦфжаT0гУРДМЧУыЃЌINT0гУРДЕїЗжИіЮЛЃЌINT1гУРДЕїЪБИіЮЛЁЃЖјЯдЪОгУЕФЪЧСљЮЛЪ§ТыЙмЖЏЬЌЯдЪОЃЌГѕЪМЪ§ОнДцдк30H--35HЕЅдЊЃЌЛКГхЧјЮЊ40H--46HЕЅдЊЃЌОпЬхГЬађШчЯТЃК

ORG 0000H

LJMP START

ORG 0003H

LJMP TIME1

ORG 0013H

LJMP TIME2

ORG 000BH

LJMP TO

ORG 0030H

START: MOV TMOD,#01H

MOV TH0,#3CH

MOV TL0,#0B0H

SETB ET0

SETB EA

SETB TR0

SETB EX0

SETB EX1

SETB IT0

SETB IT1

MOV 30H,#4

MOV 31H,#5

MOV 32H,#9

MOV 33H,#5

MOV 34H,#3

MOV 35H,#2

MOV R0,#30H

MOV R1,#40H

MOV R7,#6

MOV R5,#20

CLR F0

LOOP: ACALL LOAD

ACALL DSPY

JNB F0,LOOP

CLR F0

INC 30H

MOV R2,30H

CJNE R2,#10,LOOP ;УыИіЮЛЪЧЗёЕН10

MOV 30H,#0

INC 31H

MOV R2,31H

CJNE R2,#6,LOOP ;УыЪЎЮЛЪЧЗёЕН6

MOV 31H,#0

INC 32H

MOV R2,32H

CJNE R2,#10,LOOP ;ЗжИіЮЛЪЧЗёЕН10

MOV 32H,#0

INC 33H

MOV R2,33H

CJNE R2,#6,LOOP ;ЗжЪЎЮЛЪЧЗёЕН6

MOV 33H,#0

INC 34H ;вђаЁЪБЕН24вЊЧхСуЃЌУЛгаАьЗЈгУЩЯЪіЗНЗЈЪЕЯжЃЌдкДЫВ№ЗжЃЌаЁЪБЕФЪ§ОнШЋДцдкR4

ACALL DAA

MOV B,35H

MOV A,#10

MUL AB

ADD A,34H

MOV R4,A

CJNE R4,#24,LOOP

MOV 34H,#0

MOV 35H,#0

LJMP LOOP

LOAD: MOV A,@R0 ;зАдиД§ЯдЪ§Он

MOV DPTR,#ABC

MOVC A,@A+DPTR

MOV @R1,A

INC R0

INC R1

DJNZ R7,LOAD

MOV R0,#30H

MOV R1,#40H

MOV R7,#6

RET

DSPY: MOV R7,#6 ;ЯдЪОзгГЬађ

MOV R6,#0F8H

LOOP1: MOV P2,R6

MOV P0,@R1

INC R6

INC R1

DJNZ R7,LOOP1

MOV R7,#6

MOV R1,#40H

RET

DAA: MOV A,34H ;ЪЎНјжЦЕїећзгГЬађ

CJNE A,#10,DD2

MOV 34H,#0

INC 35H

DD2: RET

TO: DJNZ R5,SS ;T0жаЖЯГЬађ

MOV R5,#20

SETB F0

SS: MOV TH0,#3CH

MOV TL0,#0B0H

RETI

TIME1: INC 32H ;INT0жаЖЯГЬађ

MOV R2,32H

CJNE R2,#10,DD0

MOV 32H,#0

INC 33H

MOV R2,33H

CJNE R2,#6,DD0

MOV 33H,#0

INC 34H

ACALL DAA

MOV B,35H

MOV A,#10

MUL AB

ADD A,34H

MOV R4,A

CJNE R4,#24,DD0

MOV 34H,#0

MOV 35H,#0

DD0: RETI

TIME2: INC 34H ;INT1жаЖЯГЬађ

ACALL DAA

MOV B,35H

MOV A,#10

MUL AB

ADD A,34H

MOV R4,A

CJNE R4,#24,DD1

MOV 34H,#0

MOV 35H,#0

DD1: RETI

ABC: DB 3FH,06H,5BH,4FH,66H,6DH,7DH,07H,7FH,6FH

END

ЫФЁЂЕїЪд

ЕїЪдЛЈСЫМИИіаЁЪБЃЌвђЮЊздМКЖдDAAжИСюЕФРэНтВЛЙЛЩюЖјГіЯжСЫДэЮѓЃЌзюКѓгУИіDAAзгГЬађДњЬцСЫгУжИСюзЊЛЛBCDТыЃК

ЮхЁЂдЫааНсЙћ

ШчЯТЭМЃЌЪЧИеПЊЪМГЬађдЫааЕФНсЙћЃК

СљЁЂзмНс

БОДЮЪЕМљжаШУЮвИќМгРэНтСЫжаЖЯвдМАбЛЗжИСюЕФдЫгУЃЌПЩгжЗЂЯжСЫздМКЖдЭтРЉаОЦЌеЦЮеЕФВЛЙЛЃЌПЊЪМзіЕФЪЧЭтРЉ5255ЃЌПЩУЛгаГЩЙІЁЃзюКѓбЁдёСЫгУЖЏЬЌЯдЪОзіЪ§зжжгЃЌБОвдЮЊКмШнвзЃЌПЩЛЙЪЧзіСЫКмГЄЪБМфЕФГЬађЁЃЕЅЦЌЛњЪЧвЛИіЮвКмИааЫШЄЕФПЮЃЌдквдКѓЮвЛЙвЊИќМгЩюПЬЕФбЇЯАЃЌЖЭСЖздМКЕФЖЏЪжФмСІЃЌЯраХЦОзХздМКЕФжДзХЃЌвЛЖЈФмбЇКУЕЅЦЌЛњЁЃ

ВЮПМзЪСЯЃКЁЖЕЅЦЌЛњдРэгыНгПкММЪѕЁЗИпЕШНЬг§ГіАцЩчРюШЋРћБр

ЕкЖўЦЊЃКVHDLЪ§зжжгЩшМЦБЈИц

VHDLЪ§зжжгЩшМЦБЈИц

вЛ. Ъ§зжжгзмЬхЩшМЦЗНАИЃК

1.1ЩшМЦФПЕФ

Ђйе§ШЗЯдЪОЪБЁЂЗжЁЂУыЃЛ

ЂкПЩЪжЖЏаЃЪБЃЌФмЗжБ№НјааЪБЁЂЗжЕФаЃе§ЃЛ

ЂлећЕуБЈЪБЙІФмЃЛ

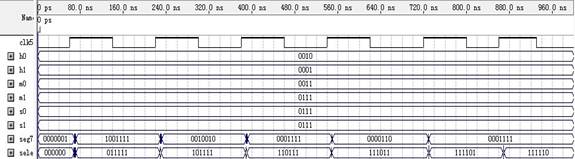

1.2ЩшМЦЫМТЗ

Ъ§зжжгЕФЩшМЦФЃПщАќРЈЃКЗжЦЕЦїЁЂШЅЖЖЖЏЕчТЗЁЂаЃЪБЕчТЗЁЂЁАЪБЁЂЗжЁЂУыЁБМЦЪ§ЦїЁЂаЃЪБЩСЫИЕчТЗЁЂећЕуБЈЪБКЭвыТыЯдЪОЕчТЗЁЃ

УПвЛИіЙІФмФЃПщзїЮЊвЛИіЪЕЬхЕЅЖРНјааЩшМЦЃЌзюКѓдйгУVHDLЕФР§ЛЏгяОфНЋИїИіФЃПщНјааећКЯЃЌЩњГЩЖЅВуЪЕЬхtopЁЃ

ИУЪ§зжжгПЩвдЪЕЯж3ИіЙІФмЃКМЦЪБЙІФмЁЂЩшжУЪБМфЙІФмКЭБЈЪБЙІФмЁЃ

ЖўЃЎЪ§зжжгФЃПщЯИНк

2.1 ЗжЦЕЦїЃЈfenpinЃЉ

БОЯЕЭГЙВаш3жжЦЕТЪЪБжгаХКХЃЈ1024HzЁЂ512HzЁЂ1HzЃЉЁЃЮЊМѕЩйЪфШыв§НХЃЌБОЯЕЭГВЩгУЗжЦЕФЃПщЃЌжЛашгЩЭтВПЬсЙЉ1024HzЛљзМЪБжгаХКХЃЌЦфгрШ§жжЦЕТЪЪБжгаХКХгЩЗжЦЕФЃПщЕУЕНЁЃ

ЗжЦЕдРэЃКЮЊвд1024HzЛљзМЪБжгО1024ЗжЦЕЕУЕН512Hz,1HzЦЕТЪЪБжгаХКХЁЃ

ЗжЦЕЦїЙмНХ

ДњТыЃК

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity fenpin is

port(clk1024:in std_logic;

clk1,clk512:out std_logic

);

end fenpin ;

architecture cml of fenpin is

begin

process (clk1024)

variable count1: integer range 0 to 512;

variable q1: std_logic;

begin

if clk1024' event and clk1024='1' then

if count1=512 then

q1:=not q1;

count1:=0;

else

count1:=count1+1;

end if;

end if;

clk1<=q1;

end process;

process(clk1024)

variable count512: integer range 0 to 1;

variable q512: std_logic;

begin

if clk1024' event and clk1024='1' then

if count512=1 then

q512:=not q512;

count512:=0;

else

count512:=count512+1;

end if;

end if;

clk512<=q512;

end process;

end cml;

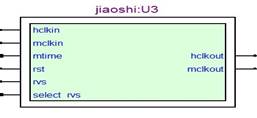

2ЃЎ2 аЃЪБЕчТЗЃЈjiaoshiЃЉ

БОФЃПщвЊЪЕЯжЕФЙІФмЪЧЃКе§ГЃМЦЪБЁЂаЃЪБЁЂаЃЗждкУПИізДЬЌЯТЖМЛсВњЩњВЛЭЌПижЦаХКХЪЕЯжЯргІЕФЙІФмЁЃ

аЃЪБЙмНХЭМ

ДњТыЃК

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity jiaoshi is

port(rst,rvs,select_rvs,mtime,mclkin,hclkin:in std_logic;

hclkout,mclkout:out std_logic

);

end jiaoshi;

architecture cml of jiaoshi is

signal h_m:std_logic;

begin

p1:process(rst,rvs,hclkin,mclkin,h_m,mtime)

begin

if rst='0' then

null;

elsif rvs='1' then

hclkout<=hclkin;

mclkout<=mCLKin;

elsif h_m='0' then

hclkout<=hclkin;

mclkout<=mtime;

else

hclkout<=mtime;mclkout<=mclkin;

end if;

end process;

p2:process(select_rvs)

begin

if select_rvs'event and select_rvs='1' then

h_m<=not h_m;

end if;

end process ;

end cml;

ЙмНХЭМ

ЗТецЭМ

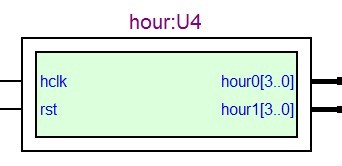

2.3 ЪБМЦЪ§ЦїЃЈhourЃЉЗжМЦЪ§Цї(mine)УыМЦЪ§Цї(second)

ЪБМЦЪ§ЦїЙмНХЭМ

ЪБДњТыЃК

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity hour is

port(rst,hclk:in std_logic;

hour0,hour1:buffer std_logic_vector(3 downto 0 )

);

end hour;

architecture cml of hour is

begin

process(rst,hclk,hour0,hour1)

begin

if rst='0' then

hour0<="0000";

hour1<="0000";

elsif hclk'event and hclk='1' then

if hour0="0011" and hour1="0010" then

hour0<="0000";

hour1<="0000";

elsif hour0="1001" then

hour0<="0000";

hour1<=hour1+1;

else

hour0<=hour0+1;

end if;

end if;

end process ;

end cml;

ЗжМЦЪ§ЦїЙмНХЭМ

ЗжДњТыЃК

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity mine is

port(rst,mclk:in std_logic;

mco:out std_logic;

min0,min1:buffer std_logic_vector(3 downto 0 )

);

end mine;

architecture cml of mine is

signal min0_t,min1_t:std_logic_vector(3 downto 0 );

begin

process(rst,mclk,min0,min1)

begin

if rst='0' then

min0<="0000";

min1<="0000";

elsif mclk'event and mclk='1' then

if min0="0101" and min1="1001" then

min0<="0000";

min1<="0000";

mco<='1';

elsif min0="0010" and min0="1001" then

min1<="0011";

min0<="0000";

mco<='0';

elsif min0="1001" then

min1<=min1+1;

min0<="0000";

else

min0<=min0+1;

end if;

end if;

end process ;

end cml;

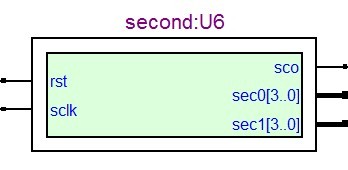

УыМЦЪ§ЦїЙмНХЭМ

УыДњТыЃК

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity second is

port(rst,sclk:in std_logic;

sco:out std_logic;

sec0,sec1:buffer std_logic_vector(3 downto 0 )

);

end second;

architecture cml of second is

signal sec0_t,sec1_t:std_logic_vector(3 downto 0 );

begin

process(rst,sclk,sec0,sec1)

begin

if rst='0' then

sec0<="0000";

sec1<="0000";

elsif sclk'event and sclk='1' then

if sec0="0101" and sec1="1001" then

sec0<="0000";

sec1<="0000";

sco<='1';

elsif sec0="0010" and sec0="1001" then

sec1<="0011";

sec0<="0000";

sco<='0';

elsif sec0="1001" then

sec1<=sec1+1;

sec0<="0000";

else

sec0<=sec0+1;

end if;

end if;

end process ;

end cml;

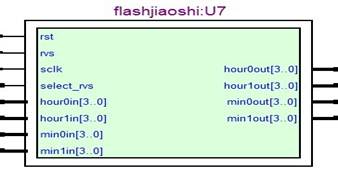

2.4 аЃЪБЩСЫИЕчТЗЃЈflashnjiaoshiЃЉ

ШчЙће§дкНјаааЃЪБЃЌflashjiaoshiНЋЪЕЯжЪЙЕБЧАе§дкаЃЪБЯюЃЈаЁЪБЛђЗжжгЃЉвд1HzЕФЦЕТЪЩСЫИЃЌвдБугкВйжЊЕРе§дкБЛаЃе§ЁЃ

аЃЪБЩСЫИЕчТЗЙмНХЭМ

ДњТыЃК

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity flashjiaoshi is

port(rst,sclk,rvs,select_rvs:in std_logic;

hour0in,hour1in,min0in,min1in:in std_logic_vector(3 downto 0 );

hour0out,hour1out,min0out,min1out :out std_logic_vector(3 downto 0 )

);

end flashjiaoshi;

architecture cml of flashjiaoshi is

signal h_m:std_logic;

begin

p1:process(rst,sclk,rvs,hour0in,hour1in,min0in,min1in,h_m)

begin

if rst='0' then

null;

elsif rvs='1' then

hour0out<=hour0in;

hour1out<=hour1in;

min0out<=min0in;

min1out<=min1in;

elsif h_m='0' then

hour0out<=hour0in;

hour1out<=hour1in;

if sclk='1' then

min0out<=min0in;

min1out<=min1in;

else

min0out<="1111";

min1out<="1111";

end if;

else

min0out<=min0in;

min1out<=min1in;

IF sCLK='1' then

hour0out<=hour0in;

hour1out<=hour1in;

else

hour0out<="1111";

hour1out<="1111";

end if;

end if;

end process p1;

p2:process(select_rvs)

begin

if select_rvs'event and select_rvs='1' then

h_m<=not h_m;

end if;

end process p2;

end cml;

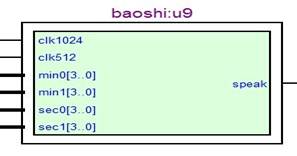

2.5 ећЕуБЈЪБЕчТЗ

ећЕуБЈЪБЙмНХЭМ

ДњТыЃК

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity baoshi is

port( clk1024,clk512 : in std_logic;

min0,min1 , sec0,sec1 : in std_logic_vector (3 downto 0);

speak : out std_logic);

end baoshi;

architecture cml of baoshi is

begin

speak<=clk512

when (min1="0101" and min0="1001" and sec1="0101") and (sec0="0011" or sec0="0101" or sec0="0111") else

clk1024

when( min1="0101" and min0="1001" and sec1="0101" and sec0="1001") else

'0';

end cml;

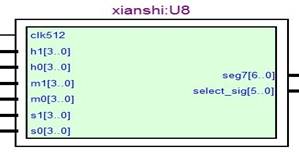

2.6 выТыЯдЪОЕчТЗ

ИУЯдЪОгУЕФЪЧЖЏЬЌЩЈУшЕчТЗ

выТыЯдЪОЙмНХЭМ

ВЈаЮЭМ

ДњТыЃК

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity xianshi is

port(clk512:in std_logic;

h1,h0,m1,m0,s1,s0:in std_logic_vector(3 downto 0 );

seg7:out std_logic_vector(6 downto 0 );

select_sig:out std_logic_vector(5 downto 0 )

);

end xianshi;

architecture cml of xianshi is

signal data:std_logic_vector(3 downto 0 );

signal order:std_logic_vector(2 downto 0 );

begin

process(clk512)

begin

if clk512' event and clk512='1' then

case order is

when "000"=>data<=h1;select_sig<="011111";

when "001"=>data<=h0;select_sig<="101111";

when "010"=>data<=m1;select_sig<="110111";

when "011"=>data<=m0;select_sig<="111011";

when "100"=>data<=s1;select_sig<="111101";

when "101"=>data<=s0;select_sig<="111110";

when others=>data<="1000";select_sig<="111111";

end case;

if order="101" then order<="000";

else order<=order+1;

end if;

end if;

end process ;

process(data)

begin

case data is

when "0000" =>seg7 <= "0000001";

when "0001" =>seg7 <= "1001111";

when "0010" =>seg7 <= "0010010";

when "0011" =>seg7 <= "0000110";

when "0100" =>seg7 <= "1001100";

when "0101" =>seg7 <= "0100100";

when "0110" =>seg7 <= "0100000";

when "0111" =>seg7 <= "0001111";

when "1000" =>seg7 <= "0000000";

when "1001" =>seg7 <= "0000100";

when others =>seg7 <= "1111111";

end case;

end process ;

end cml ;

2.7 Ъ§зжжгећЬхЩшМЦ ЃЈtopЃЉ

БОЪ§зжжгЕФЩшМЦАќРЈЗжЦЕЦїЁЂШЅЖЖЖЏЕчТЗЁЂаЃЪБЕчТЗЁЂЁАЪБЁЂЗжЁЂУыЁБМЦЪ§ЦїЁЂаЃЪБЩСЫИЕчТЗКЭвыТыЯдЪОЕчТЗЁЃвдЩЯвбОгаСЫИїИіЙІФмФЃПщЕФЪЕЯжЗНЗЈЃЌЯждкНЋИїИіФЃПщзлКЯдквЛЦ№ЃЌЙЙГЩвЛИіЭъећЕФЪ§зжжгЁЃ

ДњТыЃК

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity top is

port(clk1024,key,reset:in std_logic;

keyin:in std_logic_vector(1 downto 0 );

select_sigout:out std_logic_vector(5 downto 0 );

seg7out:out std_logic_vector(6 downto 0 );

speak:out std_logic

);

end top;

architecture cml of top is

component fenpin is

port(clk1024:in std_logic;

clk1,clk512:out std_logic

);

end component fenpin ;

component jiaoshi is

port(rst,rvs,select_rvs,mtime,mclkin,hclkin:in std_logic;

hclkout,mclkout:out std_logic

);

end component jiaoshi;

component hour is

port(rst,hclk:in std_logic;

hour0,hour1:buffer std_logic_vector(3 downto 0 )

);

end component hour;

component minute is

port(rst,mclk:in std_logic;

mco:out std_logic;

min0,min1:buffer std_logic_vector(3 downto 0 )

);

end component minute;

component second is

port(rst,sclk:in std_logic;

sco:out std_logic;

sec0,sec1:buffer std_logic_vector(3 downto 0 )

);

end component second;

component flashjiaoshi is

port(rst,sclk,rvs,select_rvs:in std_logic;

hour0in,hour1in,min0in,min1in:in std_logic_vector(3 downto 0 );

hour0out,hour1out,min0out,min1out :out std_logic_vector(3 downto 0 )

);

end component flashjiaoshi;

component xianshi is

port(clk512:in std_logic;

h1,h0,m1,m0,s1,s0:in std_logic_vector(3 downto 0 );

seg7:out std_logic_vector(6 downto 0 );

select_sig:out std_logic_vector(5 downto 0 )

);

end component xianshi;

component baoshi is

port( clk1024,clk512 : in std_logic;

min0,min1 , sec0,sec1 : in std_logic_vector (3 downto 0);

speak : out std_logic);

end component baoshi;

signal scanCLKSig : std_logic;

signal secCLKSig : std_logic;

signal hCLKSig0,hCLKSig1 : std_logic;

signal mCLKSig0,mCLKSig1 : std_logic;

signal sec1Sig,sec0Sig : std_logic_vector(3 downto 0);

signal min1Sig0,min0Sig0 : std_logic_vector(3 downto 0);

signal min1Sig1,min0Sig1 : std_logic_vector(3 downto 0);

signal hour1Sig0,hour0Sig0 : std_logic_vector(3 downto 0);

signal hour1Sig1,hour0Sig1 : std_logic_vector(3 downto 0);

begin

U1: fenpin PORT MAP(clk1024=>clk1024,clk512=>scanCLKSig,clk1=>secCLKSig);

U2: jiaoshi PORT MAP(rst=>reset, rvs=>key, select_rvs=>keyin(0),

mtime=>keyin(1),

hclkin=>hCLKSig0,mclkin=>mCLKSig0,hclkout=>hCLKSig1,mclkout=>mCLKSig1);

U3:hour PORT MAP(rst=>reset, hCLK=>hCLKSig1, hour1=>hour1Sig0,

hour0=>hour0Sig0);

U4: minute PORT MAP(rst=>reset, mclk=>mCLKSig1, mco=>hCLKSig0,

min1=>min1Sig0, min0=>min0Sig0);

U5: second PORT MAP(rst=>reset, sCLK=>secCLKSig, sco=>mCLKSig0, sec1=>sec1Sig,

sec0=>sec0Sig);

U6: flashjiaoshi PORT MAP(rst=>reset, sclk=>secCLKSig, rvs=>key,

select_rvs=>keyin(0), hour1in=>hour1Sig0, hour0in=>hour0Sig0, min1in=>min1Sig0,

min0in=>min0Sig0, hour1out=>hour1Sig1, hour0out=>hour0Sig1, min1out=>min1Sig1,

min0out=>min0Sig1);

U7: xianshi PORT MAP(clk512=>scanCLKSig, h1=>hour1Sig1, h0=>hour0Sig1, m1=>min1Sig1,

m0=>min0Sig1, s1=>sec1Sig, s0=>sec0Sig, seg7=>seg7out, select_sig=>select_sigout);

u8:baoshi PORT MAP(clk1024=>clk1024,clk512=>scanCLKSig,sec1=>sec1Sig,sec0=>sec0Sig,

min1=>min1Sig0,min0=>min0Sig0,speak=>speak);

END cml;