VHDL数字钟设计报告

VHDL数字钟设计报告

一. 数字钟总体设计方案:

1.1设计目的

①正确显示时、分、秒;

②可手动校时,能分别进行时、分的校正;

③整点报时功能;

1.2设计思路

数字钟的设计模块包括:分频器、去抖动电路、校时电路、“时、分、秒”计数器、校时闪烁电路、整点报时和译码显示电路。

每一个功能模块作为一个实体单独进行设计,最后再用VHDL的例化语句将各个模块进行整合,生成顶层实体top。

该数字钟可以实现3个功能:计时功能、设置时间功能和报时功能。

二.数字钟模块细节

2.1 分频器(fenpin)

本系统共需3种频率时钟信号(1024Hz、512Hz、1Hz)。为减少输入引脚,本系统采用分频模块,只需由外部提供1024Hz基准时钟信号,其余三种频率时钟信号由分频模块得到。

分频原理:为以1024Hz基准时钟经1024分频得到512Hz,1Hz频率时钟信号。

分频器管脚

代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity fenpin is

port(clk1024:in std_logic;

clk1,clk512:out std_logic

);

end fenpin ;

architecture cml of fenpin is

begin

process (clk1024)

variable count1: integer range 0 to 512;

variable q1: std_logic;

begin

if clk1024' event and clk1024='1' then

if count1=512 then

q1:=not q1;

count1:=0;

else

count1:=count1+1;

end if;

end if;

clk1<=q1;

end process;

process(clk1024)

variable count512: integer range 0 to 1;

variable q512: std_logic;

begin

if clk1024' event and clk1024='1' then

if count512=1 then

q512:=not q512;

count512:=0;

else

count512:=count512+1;

end if;

end if;

clk512<=q512;

end process;

end cml;

2.2 校时电路(jiaoshi)

本模块要实现的功能是:正常计时、校时、校分在每个状态下都会产生不同控制信号实现相应的功能。

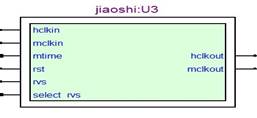

校时管脚图

代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity jiaoshi is

port(rst,rvs,select_rvs,mtime,mclkin,hclkin:in std_logic;

hclkout,mclkout:out std_logic

);

end jiaoshi;

architecture cml of jiaoshi is

signal h_m:std_logic;

begin

p1:process(rst,rvs,hclkin,mclkin,h_m,mtime)

begin

if rst='0' then

null;

elsif rvs='1' then

hclkout<=hclkin;

mclkout<=mCLKin;

elsif h_m='0' then

hclkout<=hclkin;

mclkout<=mtime;

else

hclkout<=mtime;mclkout<=mclkin;

end if;

end process;

p2:process(select_rvs)

begin

if select_rvs'event and select_rvs='1' then

h_m<=not h_m;

end if;

end process ;

end cml;

管脚图

仿真图

2.3 时计数器(hour)分计数器(mine)秒计数器(second)

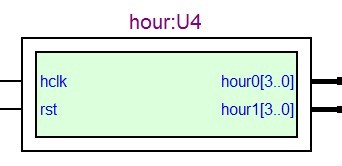

时计数器管脚图

时代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity hour is

port(rst,hclk:in std_logic;

hour0,hour1:buffer std_logic_vector(3 downto 0 )

);

end hour;

architecture cml of hour is

begin

process(rst,hclk,hour0,hour1)

begin

if rst='0' then

hour0<="0000";

hour1<="0000";

elsif hclk'event and hclk='1' then

if hour0="0011" and hour1="0010" then

hour0<="0000";

hour1<="0000";

elsif hour0="1001" then

hour0<="0000";

hour1<=hour1+1;

else

hour0<=hour0+1;

end if;

end if;

end process ;

end cml;

分计数器管脚图

分代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity mine is

port(rst,mclk:in std_logic;

mco:out std_logic;

min0,min1:buffer std_logic_vector(3 downto 0 )

);

end mine;

architecture cml of mine is

signal min0_t,min1_t:std_logic_vector(3 downto 0 );

begin

process(rst,mclk,min0,min1)

begin

if rst='0' then

min0<="0000";

min1<="0000";

elsif mclk'event and mclk='1' then

if min0="0101" and min1="1001" then

min0<="0000";

min1<="0000";

mco<='1';

elsif min0="0010" and min0="1001" then

min1<="0011";

min0<="0000";

mco<='0';

elsif min0="1001" then

min1<=min1+1;

min0<="0000";

else

min0<=min0+1;

end if;

end if;

end process ;

end cml;

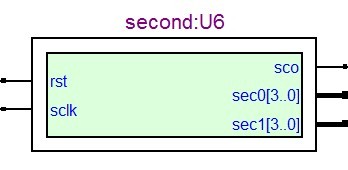

秒计数器管脚图

秒代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity second is

port(rst,sclk:in std_logic;

sco:out std_logic;

sec0,sec1:buffer std_logic_vector(3 downto 0 )

);

end second;

architecture cml of second is

signal sec0_t,sec1_t:std_logic_vector(3 downto 0 );

begin

process(rst,sclk,sec0,sec1)

begin

if rst='0' then

sec0<="0000";

sec1<="0000";

elsif sclk'event and sclk='1' then

if sec0="0101" and sec1="1001" then

sec0<="0000";

sec1<="0000";

sco<='1';

elsif sec0="0010" and sec0="1001" then

sec1<="0011";

sec0<="0000";

sco<='0';

elsif sec0="1001" then

sec1<=sec1+1;

sec0<="0000";

else

sec0<=sec0+1;

end if;

end if;

end process ;

end cml;

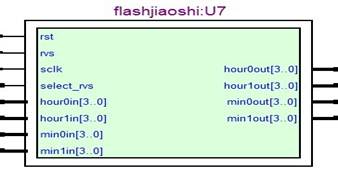

2.4 校时闪烁电路(flashnjiaoshi)

如果正在进行校时,flashjiaoshi将实现使当前正在校时项(小时或分钟)以1Hz的频率闪烁,以便于操知道正在被校正。

校时闪烁电路管脚图

代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity flashjiaoshi is

port(rst,sclk,rvs,select_rvs:in std_logic;

hour0in,hour1in,min0in,min1in:in std_logic_vector(3 downto 0 );

hour0out,hour1out,min0out,min1out :out std_logic_vector(3 downto 0 )

);

end flashjiaoshi;

architecture cml of flashjiaoshi is

signal h_m:std_logic;

begin

p1:process(rst,sclk,rvs,hour0in,hour1in,min0in,min1in,h_m)

begin

if rst='0' then

null;

elsif rvs='1' then

hour0out<=hour0in;

hour1out<=hour1in;

min0out<=min0in;

min1out<=min1in;

elsif h_m='0' then

hour0out<=hour0in;

hour1out<=hour1in;

if sclk='1' then

min0out<=min0in;

min1out<=min1in;

else

min0out<="1111";

min1out<="1111";

end if;

else

min0out<=min0in;

min1out<=min1in;

IF sCLK='1' then

hour0out<=hour0in;

hour1out<=hour1in;

else

hour0out<="1111";

hour1out<="1111";

end if;

end if;

end process p1;

p2:process(select_rvs)

begin

if select_rvs'event and select_rvs='1' then

h_m<=not h_m;

end if;

end process p2;

end cml;

2.5 整点报时电路

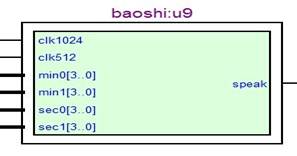

整点报时管脚图

代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity baoshi is

port( clk1024,clk512 : in std_logic;

min0,min1 , sec0,sec1 : in std_logic_vector (3 downto 0);

speak : out std_logic);

end baoshi;

architecture cml of baoshi is

begin

speak<=clk512

when (min1="0101" and min0="1001" and sec1="0101") and (sec0="0011" or sec0="0101" or sec0="0111") else

clk1024

when( min1="0101" and min0="1001" and sec1="0101" and sec0="1001") else

'0';

end cml;

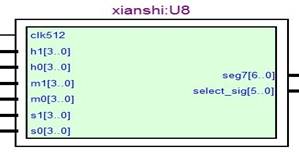

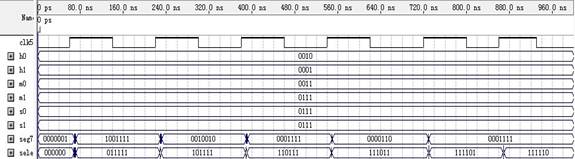

2.6 译码显示电路

该显示用的是动态扫描电路

译码显示管脚图

波形图

代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity xianshi is

port(clk512:in std_logic;

h1,h0,m1,m0,s1,s0:in std_logic_vector(3 downto 0 );

seg7:out std_logic_vector(6 downto 0 );

select_sig:out std_logic_vector(5 downto 0 )

);

end xianshi;

architecture cml of xianshi is

signal data:std_logic_vector(3 downto 0 );

signal order:std_logic_vector(2 downto 0 );

begin

process(clk512)

begin

if clk512' event and clk512='1' then

case order is

when "000"=>data<=h1;select_sig<="011111";

when "001"=>data<=h0;select_sig<="101111";

when "010"=>data<=m1;select_sig<="110111";

when "011"=>data<=m0;select_sig<="111011";

when "100"=>data<=s1;select_sig<="111101";

when "101"=>data<=s0;select_sig<="111110";

when others=>data<="1000";select_sig<="111111";

end case;

if order="101" then order<="000";

else order<=order+1;

end if;

end if;

end process ;

process(data)

begin

case data is

when "0000" =>seg7 <= "0000001";

when "0001" =>seg7 <= "1001111";

when "0010" =>seg7 <= "0010010";

when "0011" =>seg7 <= "0000110";

when "0100" =>seg7 <= "1001100";

when "0101" =>seg7 <= "0100100";

when "0110" =>seg7 <= "0100000";

when "0111" =>seg7 <= "0001111";

when "1000" =>seg7 <= "0000000";

when "1001" =>seg7 <= "0000100";

when others =>seg7 <= "1111111";

end case;

end process ;

end cml ;

2.7 数字钟整体设计 (top)

本数字钟的设计包括分频器、去抖动电路、校时电路、“时、分、秒”计数器、校时闪烁电路和译码显示电路。以上已经有了各个功能模块的实现方法,现在将各个模块综合在一起,构成一个完整的数字钟。

代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity top is

port(clk1024,key,reset:in std_logic;

keyin:in std_logic_vector(1 downto 0 );

select_sigout:out std_logic_vector(5 downto 0 );

seg7out:out std_logic_vector(6 downto 0 );

speak:out std_logic

);

end top;

architecture cml of top is

component fenpin is

port(clk1024:in std_logic;

clk1,clk512:out std_logic

);

end component fenpin ;

component jiaoshi is

port(rst,rvs,select_rvs,mtime,mclkin,hclkin:in std_logic;

hclkout,mclkout:out std_logic

);

end component jiaoshi;

component hour is

port(rst,hclk:in std_logic;

hour0,hour1:buffer std_logic_vector(3 downto 0 )

);

end component hour;

component minute is

port(rst,mclk:in std_logic;

mco:out std_logic;

min0,min1:buffer std_logic_vector(3 downto 0 )

);

end component minute;

component second is

port(rst,sclk:in std_logic;

sco:out std_logic;

sec0,sec1:buffer std_logic_vector(3 downto 0 )

);

end component second;

component flashjiaoshi is

port(rst,sclk,rvs,select_rvs:in std_logic;

hour0in,hour1in,min0in,min1in:in std_logic_vector(3 downto 0 );

hour0out,hour1out,min0out,min1out :out std_logic_vector(3 downto 0 )

);

end component flashjiaoshi;

component xianshi is

port(clk512:in std_logic;

h1,h0,m1,m0,s1,s0:in std_logic_vector(3 downto 0 );

seg7:out std_logic_vector(6 downto 0 );

select_sig:out std_logic_vector(5 downto 0 )

);

end component xianshi;

component baoshi is

port( clk1024,clk512 : in std_logic;

min0,min1 , sec0,sec1 : in std_logic_vector (3 downto 0);

speak : out std_logic);

end component baoshi;

signal scanCLKSig : std_logic;

signal secCLKSig : std_logic;

signal hCLKSig0,hCLKSig1 : std_logic;

signal mCLKSig0,mCLKSig1 : std_logic;

signal sec1Sig,sec0Sig : std_logic_vector(3 downto 0);

signal min1Sig0,min0Sig0 : std_logic_vector(3 downto 0);

signal min1Sig1,min0Sig1 : std_logic_vector(3 downto 0);

signal hour1Sig0,hour0Sig0 : std_logic_vector(3 downto 0);

signal hour1Sig1,hour0Sig1 : std_logic_vector(3 downto 0);

begin

U1: fenpin PORT MAP(clk1024=>clk1024,clk512=>scanCLKSig,clk1=>secCLKSig);

U2: jiaoshi PORT MAP(rst=>reset, rvs=>key, select_rvs=>keyin(0),

mtime=>keyin(1),

hclkin=>hCLKSig0,mclkin=>mCLKSig0,hclkout=>hCLKSig1,mclkout=>mCLKSig1);

U3:hour PORT MAP(rst=>reset, hCLK=>hCLKSig1, hour1=>hour1Sig0,

hour0=>hour0Sig0);

U4: minute PORT MAP(rst=>reset, mclk=>mCLKSig1, mco=>hCLKSig0,

min1=>min1Sig0, min0=>min0Sig0);

U5: second PORT MAP(rst=>reset, sCLK=>secCLKSig, sco=>mCLKSig0, sec1=>sec1Sig,

sec0=>sec0Sig);

U6: flashjiaoshi PORT MAP(rst=>reset, sclk=>secCLKSig, rvs=>key,

select_rvs=>keyin(0), hour1in=>hour1Sig0, hour0in=>hour0Sig0, min1in=>min1Sig0,

min0in=>min0Sig0, hour1out=>hour1Sig1, hour0out=>hour0Sig1, min1out=>min1Sig1,

min0out=>min0Sig1);

U7: xianshi PORT MAP(clk512=>scanCLKSig, h1=>hour1Sig1, h0=>hour0Sig1, m1=>min1Sig1,

m0=>min0Sig1, s1=>sec1Sig, s0=>sec0Sig, seg7=>seg7out, select_sig=>select_sigout);

u8:baoshi PORT MAP(clk1024=>clk1024,clk512=>scanCLKSig,sec1=>sec1Sig,sec0=>sec0Sig,

min1=>min1Sig0,min0=>min0Sig0,speak=>speak);

END cml;

-

数字钟设计报告_南昌大学

数字钟设计报告学生姓名:学号:专业班级:目录一、绪论1.1课程认知数字钟是采用数字电路实现对时、分、秒,数字显示的计时装置。早已成…

-

数字电子时钟课程设计报告

数字电子钟课程设计报告题目:数字电子钟的设计与仿真专业:机械工程前言加入世贸组织以后,中国会面临激烈的竞争。这种竞争将是一场科技实…

-

数字钟设计报告——数字电路实验报告

数字钟设计实验报告专业工程技术系班级电信0901班姓名XX学号XXXXXX数字钟的设计目录一前言3二设计目的3三设计任务3四设计方…

-

数字钟设计报告

目录1设计的任务与要求111数字钟的设计目的112数字钟的设计要求213数字电子钟的基本原理22实验器材和主要器件221主要器材2…

-

数字钟实验报告

数字钟实验报告课题名称:数字钟的设计与制作组员:姓名:班级:电气信息I类112班实验时间:实验地点:指导老师:一、实验目的:1.学…

-

数字时钟设计报告总结

数字时钟课程设计第1页共19页数字时钟课程设计目录一引言2二设计指标21指标要求22设计要求2三原理设计31总体方案设计32单元电…

-

南昌大学数字钟设计实验报告

数字电路与逻辑设计实验实验报告题目学院信息工程学院系电子信息工程专业班级学号学生姓名同组同学指导教师递交日期23页第1页共南昌大学…

-

数电课程实验报告——数字钟的设计

数字电子技术课程设设计题目班级学号学生姓名指导教师时间计报告数字钟的设计20xx年12月27日20xx年1月2日数字电子技术课程设…

-

数字时钟设计报告总结

数字时钟课程设计目录一引言2二设计指标21指标要求22设计要求2三原理设计31总体方案设计32单元电路设计41时间计数单元42时间…

-

数字钟VHDL设计报告

设计报告课程名称任课教师设计题目班级姓名学号日期在系统编程技术合肥学院课程设计报告目录摘要1关键词数字钟EDAVHDL语言1一设计…

-

数字电子钟设计实训报告

四川机电职业技术学院设计报告书数字电子钟的设计摘要本系统由晶体振荡器分频器计数器译码器七段译码显示器和校准报时电路组成采用了CMO…