8086简易计算器的设计 微机原理 计硬报告

计算机硬件技术实践报告

题目 简易计算器的设计

姓名

专业 自动化(电站方向)

班级

学号

上海电力学院自动化工程学院

实践报告内容(目录)

一. 设计题目

二. 开发目的

三. 小组成员分工及成果

四. 设计方案以及论证

五. 硬件原理图(包括芯片的选型介绍)

六. 程序流程图(包括各个子系统和子过程的程序流程)

七. 程序清单,要有适当的注释

八. 程序运行结果分析与预测

九. 结果评述或总结(对实验结果进行分析,对实验过程进行总结,系统改进升级建议或者提出新的方案等。)

一.设计题目:

用8086设计一个能实现0~9整数加法运算的计算器,并用2位LED数码显示. 键盘包括0-9,+ ,-,*,/,=,ON/C;共16个按键.能实现简单的清零操作,减法运算,乘法运算.

二.开发目的:

通过课程设计,熟悉和掌握微机系统的软件、硬件设计的方法、设计步骤,得到微机开发应用方面的初步训练。培养集体讨论设计题目的总体设计方案、编程、软件硬件调试、编写设计报告等问题,做到理论联系实际,提高动手能力和分析问题、解决问题的能力,实现由学习知识到应用知识的初步过渡。通过本次课程设计熟练运用程序对8255控制键盘和LED显示的控制,完成计算器加减法的应用,并熟练应用8086汇编语言编写应用程序和实际设计中的硬软件调试方法和步骤,熟悉微机系统的硬软件开发工具的使用方法。

三.小组成员分工及成果:

本组的三个成员一起讨论研究简易计算器设计的主要方案。

粗略设计程序流程图以确定简易计算器设计的大概框架。

明确目的后各自查询资料了解设计原理、逐步清晰设计思路。

以下为大体分工:主要负责:1、设计主要程序,编写;

2、查找资料验证修改;

主要负责:1、选择需要用的各个芯片;

2、设计硬件原理图;

主要负责:1、各个芯片功能的资料查找;

2、设计程序流程图

四.设计方案以及论证:

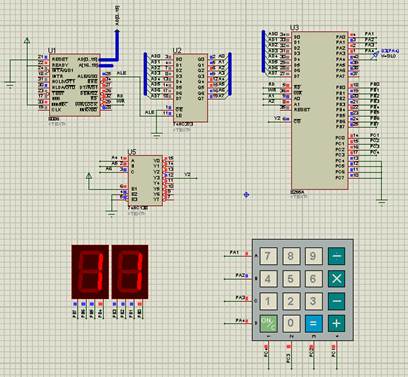

利用程序不断扫描所设的按钮键盘是不是有输入,如果没有就一直扫描,如果有就调用子程序进行判断,是数值则进行存储并同时进行显示,是运算符号等就调用相应的子程序进行操作,操作后则继续利用程序不断扫描键盘是不是有输入,从而实现部分十进制数的加、减、乘、除的运算。运算完成后根据程序将运算的结果储存到锁存器中并显示到LED显示器上。主要器件选择是采用8086CPU做主控制器,8255作为并行接口电路实现按键扫描以及数码管的显示。通过8255A的C口和A口实现键盘的接入,通过键盘的不断扫描,如果有键按下,通过查表法分别将输入的数据读到AL中并保存在第一个和第二个数里,将8255A的B端口接上共阴极LED灯,将输入的数据通过查表法,将四段码送共阴极LED灯显示,当按下‘=’时,通过判断字符,8086来实现不同的操作,并将结果在LED灯上显示,当按下“C”时,将数据先清零,同时LED灯上显示为“00”。

五.硬件原理图(包括芯片的选型介绍):

芯片选型及介绍:

(1)8086CPU:

8086通过数据总线、地址总线、控制总线完成对8253和8255的读写工作,与接口部件实现数据传送,让接口部件实现预计的功能.

8086CPU的40条引脚信号可按功能分可分为四类,它们是:地址总线,数据总线,控制总线,其它(时钟与电源)。

最小模式下一些引脚功能(MN/MX接+5V):

AD15~AD0,地址/数据总线

A19/S6~A16/S3,地址/状态总线

RD,读信号

WR,写信号

M/IO,存储器/输入输出控制信号

ALE,地址锁存允许信号

READY(Ready),准备就绪信号

INTR,可屏蔽中断请求信号

INTA,中断响应信号

NMI,非屏蔽中断请求信号

RESET,系统复位信号

DEN,数据允许信号

DT/R,数据发送/接收控制信号

HOLD,总线保持请求信号输入

HLDA,总线保持响应信号

TEST,测试信号

CLK,时钟输入信号

VCC(+5V),GND

(2)8255A可编程并行接口芯片:

Intel 8086/8088 系列的可编程外设接口电路(Programmable Peripheral Interface)简称 PPI,型号为8255(改进型为8255A及8255A-5),具有24条输入/输出引脚、可编程的通用并行输入/输出接口电路。它是一片使用单一+5V电源的40脚双列直插式大规模集成电路。8255A的通用性强,使用灵活,通过它CPU可直接与外设相连接。

8255A可为8086微处理器与外部设备之间提供并行输入/输出的通道。通过编程可以设置芯片的工作方式,并行接口是在多根数据线上,以数据字节/字与I/O设备交换信息。

8255A由数据总线缓冲器、读/写控制逻辑电路、A组和B组控制电路以及数据端口A、B和C组成。数据总线缓冲器是8255A与系统数据总线的接口,CPU输入输出的数据、CPU输出的控制字和外设的状态信息都是通过这个缓冲器传送的。读/写控制逻辑电路把CPU的控制命令或输出数据送至相应的端口,把外设的状态信息或输入数据通过相应的端口送至CPU。数据端口PA和PB都包含一个8位输出锁存器/缓冲器和一个8位输入锁存器,

(3)74HC373:

其中D0-D7为数据输入端,Q0-Q7为输出端。

当三态允许控制端OE为低电平时,Q0-Q7为正常逻辑状态,可用来驱动负载或总线,当OE为高电平时,Q0-Q7成高阻态,不驱动总线。

当锁存允许端LE为高电平时,Q随数据D而变,当LE为低电平D被锁存在已建立的数据电平。

(4)74HC138:

74HC138是一款高速CMOS器件,74HC138引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC138译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。74HC138特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高,74HC138为反相输出,它按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个 低电平输出。两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器。

六.程序流程图:

七.程序清单

DATA SEGMENT

NUM1 DB 03H DUP(0)

NUM DB 03H DUP(0)

DATA ENDS

STACK SEGMENT

DW 100 DUP(0)

STACK ENDS

CODE SEGMENT

ASSUME CS:CODE,DS:DATA,SS:STACK

PORTA EQU 30H

PORTB EQU 32H

PORTC EQU 34H

PORT8255 EQU 36H

MAIN PROC FAR

START: MOV AX,DATA

MOV DS,AX

MOV DX,PORT8255

MOV AL,81H

OUT DX,AL

LOPL: XOR AH,AH

CALL KEY

CMP AH,00H

JZ LOPL

CMP AL,0FH

JZ CCCL

CMP AL,0AH

JZ LOPL

JNC LOPL

OUT 32H,AL

LOPL2:

LEA SI,NUM

MOV [SI],AL

PUSH AX

LOPL1: XOR AH,AH

CALL KEY

CMP AH,00H

JZ LOPL1

CMP AL,0FH

JZ CCCL

CMP AL,0AH

JZ XX1

CMP AL,0BH

JZ XX2

CMP AL,0CH

JZ XX3D

CMP AL,0DH

JZ XX4D

JMP LOPL1

CCCL: MOV AL,00H

OUT 32H,AL

JMP LOPL

XX3D: CALL XX3

XX4D: CALL XX4

MAIN ENDP

XX1 PROC

NOP ;加

LOPL3: XOR AH,AH

CALL KEY

CMP AH,00H

JZ LOPL3

CMP AL,0FH

JZ CCCL

CMP AL,0AH

JZ LOPL3

JNC LOPL3

OUT 32H,AL

PUSH AX

LEA SI,NUM

MOV [SI+1],AL

LOPL4: XOR AH,AH

CALL KEY

CMP AH,00H

JZ LOPL4

CMP AL,0FH

JZ CCCL

CMP AL,0EH

JZ XXX1

JMP LOPL4

XXX1: LEA SI,NUM

MOV AL,[SI]

AND AL,0FH

MOV DL,[SI+1]

AND DL,0FH

ADD AL,DL

DAA

OUT 32H,AL

JMP LOPL

XX1 ENDP

XX2 PROC

NOP ;减

LOPL5: XOR AH,AH

CALL KEY

CMP AH,00H

JZ LOPL5

CMP AL,0FH

JZ CCCL

CMP AL,0AH

JZ LOPL5

JNC LOPL5

OUT 32H,AL

PUSH AX

LEA SI,NUM

MOV [SI+1],AL

LOPL6:

XOR AH,AH

CALL KEY

CMP AH,00H

JZ LOPL6

CMP AL,0FH

JZ CCCL7

CMP AL,0EH

JZ XXX2

JMP LOPL6

XXX2: LEA SI,NUM

MOV AL,[SI]

AND AL,0FH

MOV DL,[SI+1]

AND DL,0FH

SUB AL,DL

ADD AL,00H

DAA

OUT 32H,AL

JMP LOPL

CCCL7: MOV AL,00H

OUT 32H,AL

JMP LOPL

XX2 ENDP

XX3 PROC

LOPL7: XOR AH,AH

CALL KEY ;乘

CMP AH,00H

JZ LOPL7

CMP AL,0FH

JZ CCCL2

CMP AL,0AH

JZ LOPL7

JNC LOPL7

OUT 32H,AL

PUSH AX

LEA SI,NUM

MOV [SI+1],AL

LOPL8: XOR AH,AH

CALL KEY

CMP AH,00H

JZ LOPL8

CMP AL,0FH

JZ CCCL3

CMP AL,0EH

JZ XXX3

JMP LOPL8

XXX3: LEA SI,NUM

MOV AL,[SI]

AND AL,0FH

MOV DL,[SI+1]

AND DL,0FH

MUL DL

AAM

MOV CL,4

SAL AH,CL

OR AL,AH

OUT 32H,AL

JMP LOPL

CCCL2: MOV AL,00H

OUT 32H,AL

JMP LOPL

CCCL3: MOV AL,00H

OUT 32H,AL

JMP LOPL

XX3 ENDP

XX4 PROC ;除

LOPL9: XOR AH,AH

CALL KEY

CMP AH,00H

JZ LOPL9

CMP AL,0FH

JZ CCCL5

CMP AL,0AH

JZ LOPL9

JNC LOPL9

OUT 32H,AL

PUSH AX

LEA SI,NUM

MOV [SI+1],AL

LOPL10: XOR AH,AH

CALL KEY

CMP AH,00H

JZ LOPL10

CMP AL,0FH

JZ CCCL4

CMP AL,0EH

JZ XXX4

JMP LOPL10

XXX4: LEA SI,NUM

MOV AL,[SI]

AND AL,0FH

MOV BL,[SI+1]

AND BL,0FH

AND AX,000FH

DIV BL

OUT 32H,AL

JMP LOPL

CCCL4: MOV AL,00H

OUT 32H,AL

JMP LOPL

CCCL5: MOV AL,00H

OUT 32H,AL

JMP LOPL

XX4 ENDP

KEY PROC

NOP

LEA SI,NUM1

MOV AL,0EH

OUT 30H,AL

IN AL,34H

CMP AL,07H

JZ LL7

CMP AL,0BH

JZ LL8

CMP AL,0DH

JZ LL9

CMP AL,0EH

JZ LDIV

SS1: MOV AL,0DH

OUT 30H,AL

IN AL,34H

CMP AL,07H

JZ LL4

CMP AL,0BH

JZ LL5

CMP AL,0DH

JZ LL6

CMP AL,0EH

JZ LMUL

SS2: MOV AL,0BH

OUT 30H,AL

IN AL,34H

CMP AL,07H

JZ LL1

CMP AL,0BH

JZ LL2

CMP AL,0DH

JZ LL3

CMP AL,0EH

JZ LSUB

SS3: MOV AL,07H

OUT 30H,AL

IN AL,34H

CMP AL,07H

JZ SCLC

CMP AL,0BH

JZ LL0

CMP AL,0DH

JZ LEQU

CMP AL,0EH

JZ LADD

JMP KCLC

LDIV: MOV AL,0DH

JMP LCLC

LL0: MOV AL,00H

JMP LCLC

LL1: MOV AL,01H

JMP LCLC

LL2: MOV AL,02H

JMP LCLC

LL3: MOV AL,03H

JMP LCLC

LL4: MOV AL,04H

JMP LCLC

LL5: MOV AL,05H

JMP LCLC

LL6: MOV AL,06H

JMP LCLC

LL7: MOV AL,07H

JMP LCLC

LL8: MOV AL,08H

JMP LCLC

LL9: MOV AL,09H

JMP LCLC

LADD: MOV AL,0AH

JMP LCLC

LSUB: MOV AL,0BH

JMP LCLC

LMUL: MOV AL,0CH

JMP LCLC

LEQU: MOV AL,0EH

JMP LCLC

SCLC: MOV AL,0FH

LCLC: MOV [SI],AL

MOV AH,01H

KCLC:

RET

KEY ENDP

CODE ENDS

END START

八.程序运行结果分析与预测:

连接完线路图后把编好的程序关联到8086CPU中进行运行调试,肯定可以实现加减乘除运算,例如3+8=11,通过按键分别输入“3”, “+”,“8”, “=”后,LED灯上将显示出“11”.能实现清零操作,当按下“ON/C”时,LED上显示“00”。如图

3+8=11

当输入“3”, “*”,“8”, “=”后,LED灯上将显示出“24”.如图

3*8=24

十. 结果评述:

本期刚学过微机原理,学得不是很深入,仅限于课本知识的掌握,而此次 课程设计将会是一个很好的机会,来考察自己对课本知识的掌握以及应用情况。本次课程设计是二到三人人一组,并且自由选择设计课题,我们小组选择了简易计算器的课题,在做的过程中也遇到很多困难。

通过本次课程设计实验我们初步接触了较复杂程序的设计。在实验中用程序对8255进行控制键盘和LED显示的控制,完成计算器加减法的应用。在程序编写中,明白和掌握程序的原理和实现方式。学习和掌握计算机中常用接口电路的应用和设计技术,充分认识理论知识对应用技术的指导性作用,进一步加强理论知识与应用相结合的实践和锻炼。通过这次设计实践使我们的设计水平和对所学的知识的应用能力以及分析问题解决问题的能力得到了全面提高.

我对微机原理有了进一步的理解,对8086、8255A的工作原理、用途以及使用时的注意事项等都有了深刻的认识,对这类的课程设计也从毫无概念到了有清晰的认识的转变,相信再做这类的课程设计时不会再迷茫、不知从何入手。

总之,这次课程设计对于我们有很大的帮助,我更加深入地理解了,微机原理课程上讲到的各种芯片的功能,以及引脚的作用,同时加深了对于主要芯片的应用的认识,同时在试验室的环境里熟悉了汇编程序的编写过程和运行过程,最后还提高了自己的动手能力。感谢老师的悉心指导。

-

简易计算器设计实验报告

简易计算器设计实验报告一设计任务及要求11实验任务根据计算器的原理设计一个具有加减乘除功能的简易计算器如5348412实验基本要求…

-

简单的计算器实验报告

HUNANUNIVERSITY程序设计训练简单的计算器报告学生姓名田博鑫学生学号专业班级指导老师20xx年6月16日至20xx年7…

-

简易计算器VB课程设计报告

简易计算器要求用VB做类似于windows自带的计算器程序绪论VisualBasicVB是一种由微软公司开发的包含协助开发环境的事…

-

简易计算器的设计报告

陕西理工学院课程设计引言当今时代是一个新技术层出不穷的时代在电子领域尤其是自动化智能控制领域传统的分立元件或数字逻辑电路构成的控制…

-

C++简单计算器课程设计报告

武汉理工大学专业课程设计2课程设计说明书目录1基本功能描述12设计思路13软件设计431设计步骤44结论与心得体会127附设计中的…

-

单片机设计报告-基于51单片机的简易计算器设计

电子课程设计报告基于51单片机的简易计算器设计电子课程设计报告基于51单片机的简易计算器设计姓名朱启超专业电子信息科学与技术班级学…

-

C++简单计算器课程设计报告

武汉理工大学专业课程设计2课程设计说明书目录1基本功能描述12设计思路13软件设计431设计步骤44结论与心得体会127附设计中的…

-

C++简单计算器课程设计报告

武汉理工大学专业课程设计2课程设计说明书目录1基本功能描述12设计思路13软件设计431设计步骤432界面设计533关键功能的实现…

-

设计一个简单计算器的C语言课程设计报告

C语言课程设计报告题目设计一个简单计算器目录1设计目的2内容3总体设计有流程图4源程序编写附上了运行图5执行结果6心得体会一设计目…

-

关于计算器软件综合设计报告模板

武汉工程大学计算机科学与工程学院综合设计报告设计题目学生学号0905090106专业班级学生姓名洪腾学生成绩指导教师职称课题工作时…