《基于VHDL数字频率计的设计》开题报告+(1) (2)

商洛学院

本科毕业设计(论文)开题报告

题 目 基于VHDL数字频率计的设计

题 目 基于VHDL数字频率计的设计

学 院 名 称 物理与电子信息工程系

专业班级 电子信息工程10级2班

学生姓名 吕超

学 号 10037318

指 导 教 师 刘萌

填表时间: 2014 年 3 月 10日

填表说明

1.开题报告作为毕业设计(论文)答辩委员会对学生答辩资格审查的依据材料之一。

2.此报告应在指导教师指导下,由学生在毕业设计(论文)工作前期完成,经指导教师签署意见、相关系主任审查后生效。

3.学生应按照学校统一设计的电子文档标准格式,用A4纸打印。

4.参考文献不少于8篇,其中应有适当的外文资料(一般不少于2篇)。

5.开题报告作为毕业设计(论文)资料,与毕业设计(论文)一同存档。

第二篇:数字频率计设计VHDL

实验十八 数字频率计

实验目的

在 MagicSOPC 实验箱上实现8位十进制频率计的设计。被测信号从 CLOCK0(数字信号时钟源)输入,经过检测后测得的频率值用数码管 1~8显示。

实验器材

1、SOPC实验箱

2、计算机(装有Quartus II 7.0软件)

实验预习

1、了解数字频率计设计原理各主要模块的设计方法。 2、提前预习,编写好主模块的VHDL程序。

实验原理

频率即信号1s内振动次数,因此测定信号的频率必须有一个脉宽为1秒的输入信号作为计数允许的信号;1 秒计数结束后,计数值锁入锁存器,并为下一测频计数周期作准备的计数器清零。

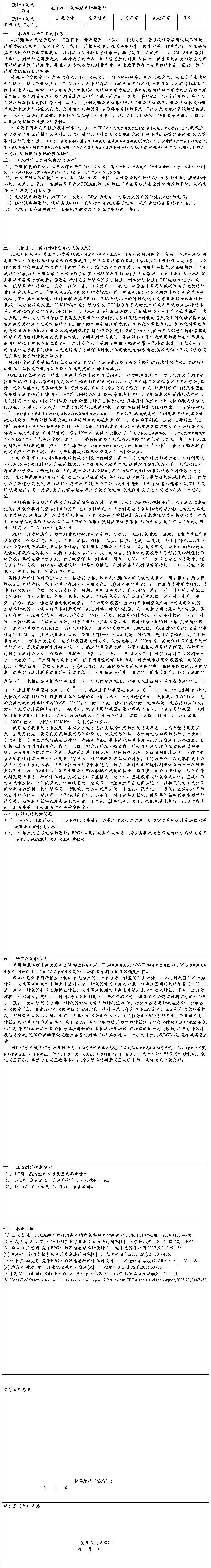

数字频率计框图如图18.1所示。由控制、计数、锁存、译码显示四部分组成。工作原理为:控制信号产生电路对系统时钟分频后产生0.5Hz的门控信号gate,锁存允许信号LE,清零信号MR。当gate为高电平时,计数器对被测信号cin进行计数;1s后gate变为低电平,计数器停止计数;当gate为低电平、LE上升沿这两个条件同时满足时,锁存电路将32位计数结果锁存送译码显示电路;当gate为低电平、MR上升沿这两个条件同时满足时,计数器清零,为下一次计数做准备。各信号之间的时序关系见图18.2所示。

图18.1 数字频率计框图

1、控制信号产生电路:根据选定的输入时钟信号设定分频系数,要求输出0.5Hz门控信号gate、1Hz锁存允许信号LE和1Hz清零信号MR。这几个信号控制整个系统的工作,非常关键,要求先锁存后清零,否则计数结果可能丢失,参考时序图18.2所示。

2、计数模块:定义十进制计数器元件,有cp(时钟输入)、MR(清零输入,上升沿有效)、gate(门控信号)三个个输入引脚,Q0~Q3、co(进位)5个输出引脚。功能定义为gate为高电平时在cp上升沿计数;gate为低MR为高时清零。利用元件调用的方法组成8位十进制计数器

3、锁存电路:设计一32位锁存器,定义gate(门控信号)、LE(锁存允许,上升沿有效)d0~d31共34个输入引脚;Q0~Q31共32个输出引脚。功能定义为gate为低时在LE上升沿锁存。

4、译码显示模块:参考数字钟。

1s

gate(0.5Hz)

Cin

LE(1Hz)

MR(1Hz)

计数锁存清零

图18.2 各信号之间的时序关系

程序模块设计

十进制模块

Library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

Entity counter10 IS

PORT(clk,rst:in std_logic;

bcd:out std_logic_vector(3 downto 0);

up:out std_logic);

END entity counter10;

Architecture bhv of counter10 IS

signal bcd_r:std_logic_vector(3 downto 0);

signal up_r:std_logic;

Begin

Process(clk,rst)

Begin

IF rst='1' THEN

bcd_r<=(others=>'0');

up_r<='0';

ELSIF clk'EVENT AND clk='1' THEN

IF bcd_r="1001" THEN

bcd_r<=(others=>'0');up_r<='1';

ELSE bcd_r<=bcd_r+1;

up_r<='0';

END IF;

END IF;

END PROCESS;

bcd<=bcd_r;

up<=up_r;

END bhv;

信号控制模块

Library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

ENTITY kongzhi IS

PORT(rst_in,sys_clk:in std_logic;

gate,lock,rst:out std_logic);

END ENTITY;

Architecture one of kongzhi IS

signal count:std_logic_vector(25 downto 0);

Begin

PROCESS(sys_clk,rst_in)

Begin

IF rst_in='0' THEN

count<=(others=>'0');gate<='0';lock<='0';rst<='0'; ELSIF sys_clk'EVENT AND sys_clk='1' THEN

IF count="1011xxxxxxxxxxxx000000011"THEN count<="00000000000000000000000000"; gate<='1';lock<='0';rst<='0';

ELSIF count="1011xxxxxxxxxxxx000000010"THEN gate<='0';lock<='0';rst<='1';

count<=count+1;

ELSIF count="1011xxxxxxxxxxxx000000001"THEN gate<='0';lock<='1';rst<='0';

count<=count+1;

ELSIF count="1011xxxxxxxxxxxx000000000"THEN gate<='0';lock<='0';rst<='0';

count<=count+1;

ELSE count<=count+1;

gate<='1';lock<='0';rst<='0';

END IF;

END IF;

END PROCESS;

END one;

锁存模块

Library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

ENTITY suocun IS

Port(lock:in std_logic;

data_in:in std_logic_vector(31 downto 0);

data_out:out std_logic_vector(31 downto 0));

END entity suocun;

Architecture one of suocun IS

signal data_out_r:std_logic_vector(31 downto 0);

Begin

Process(lock)

Begin

IF lock='1' THEN

data_out_r<=data_in;

END IF;

END PROCESS;

data_out<=data_out_r;

END one;

数码管显示译码模块

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_Arith.ALL;

USE IEEE.STD_LOGIC_Unsigned.ALL;

ENTITY xianshi IS

PORT(

clk:IN STD_LOGIC; datain:IN STD_LOGIC_VECTOR(31 DOWNTO 0); dig,seg:OUT STD_LOGIC_VECTOR(7 DOWNTO 0) );

END ENTITY;

ARCHITECTURE one OF xianshi IS

SIGNAL counter: std_logic_vector(2 DOWNTO 0); SIGNAL display: std_logic_vector(3 DOWNTO 0); SIGNAL seg_r: std_logic_vector(7 DOWNTO 0); SIGNAL dig_r: std_logic_vector(7 DOWNTO 0);

BEGIN

AAA:PROCESS(clk)

BEGIN

IF clk'EVENT AND clk='1' THEN

counter<=counter+1;

END IF;

END PROCESS AAA;

BBB:PROCESS(counter)

BEGIN

CASE counter IS

WHEN "000" => dig_r<="01111111";

WHEN "001" => dig_r<="10111111";

WHEN "010" => dig_r<="11011111";

WHEN "011" => dig_r<="11101111";

WHEN "100" => dig_r<="11110111";

WHEN "101" => dig_r<="11111011";

WHEN "110" => dig_r<="11111101";

WHEN "111" => dig_r<="11111110";

WHEN OTHERS =>NULL;

END CASE;

END PROCESS BBB;

CCC:PROCESS(counter,datain)

BEGIN

CASE counter IS

WHEN "000" => display<=datain(31 DOWNTO 28);

WHEN "001" => display<=datain(27 DOWNTO 24);

WHEN "010" => display<=datain(23 DOWNTO 20);

WHEN "011" => display<=datain(19 DOWNTO 16);

WHEN "100" => display<=datain(15 DOWNTO 12);

WHEN "101" => display<=datain(11 DOWNTO 8);

WHEN "110" => display<=datain(7 DOWNTO 4);

WHEN "111" => display<=datain(3 DOWNTO 0);

WHEN OTHERS =>NULL;

END CASE;

END PROCESS CCC;

DDD:PROCESS(display)

BEGIN

CASE display IS WHEN X"0"=> seg_r<=X"c0";

WHEN X"1"=> seg_r<=X"f9";

WHEN X"2"=> seg_r<=X"a4";

WHEN X"3"=> seg_r<=X"b0";

WHEN X"4"=> seg_r<=X"99";

WHEN X"5"=> seg_r<=X"92"; WHEN X"6"=> seg_r<=X"82"; WHEN X"7"=> seg_r<=X"f8"; WHEN X"8"=> seg_r<=X"80"; WHEN X"9"=> seg_r<=X"90"; WHEN X"a"=> seg_r<=X"88"; WHEN X"b"=> seg_r<=X"83"; WHEN X"c"=> seg_r<=X"c6"; WHEN X"d"=> seg_r<=X"a1"; WHEN X"e"=> seg_r<=X"86"; WHEN X"f"=> seg_r<=X"8e"; WHEN OTHERS =>NULL; END CASE;

END PROCESS DDD;

seg<=seg_r;

dig<=dig_r;

END ARCHITECTURE;

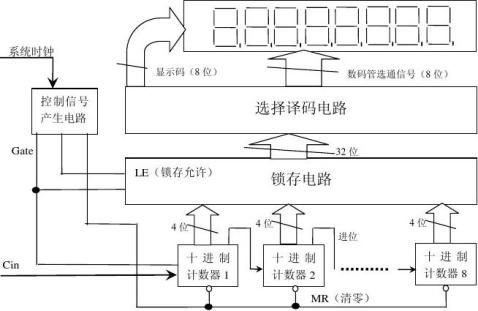

原理图

-

数字频率计开题报告

武汉大学珞珈学院本科生毕业论文设计开题报告毕业论文设计题目数字频率计系统设计系电子信息科学系学号20xx05060姓名一论文选题的…

-

开题报告数字频率计

杭州电子科技大学毕业设计论文开题报告题目学院专业姓名班级学号指导教师数字频率计的设计与实现通信工程学院通信工程孔冬滨120xx41…

- 数字频率计毕业设计开题报告

-

数字频率计开题报告

本科学生毕业设计论文开题报告系分院课题名称数字频率计的设计专业电子信息工程班级电信学生姓名指导教师李宇春日期20xx年12月23日…

-

数字频率计开题报告

本科生毕业设计论文开题报告院系信息工程学院专业电子信息班级D0842姓名赵培指导教师李悦研究方向单片机技术题目基于单片机的数字频率…

-

《EDA技术》数字频率计课程设计报告报

EDA技术课程设计报告题目数字频率计专业电子信息工程班级0702姓名指导教师高金定二0一0年6月24日020xx32820xx32…

-

基于51单片机的数字频率计设计报告

目录摘要.3关键词.3正文.41概述.42总体设计方案.52.1软件.52.2设计思路.53系统软件设计.53.1主板说明.53.…

-

数字频率计课程设计报告

赣南师院物理与电子信息学院数字电路课程设计报告书姓名班级学号时间数字频率计的设计一设计任务和要求1能够测量正弦波三角波锯齿波矩形波…

-

简易数字频率计设计实验报告 季克宇

电子线路课程设计报告第1页共14页电子线路课程设计报告姓名季克宇学号110404130专业通信工程日期20xx1010南京理工大学…

-

基于EDA与VHDL语言的8位数字频率计的课程设计报告

数字频率计的设计频率计测量频率的原理图如下图1频率计测量频率的原理图32频率计测量周期的原理321频率计测量周期的原理频率计测量周…

- 基于单片机的频率计设计开题报告