EDA数字秒表课程设计报告

课程设计任务书

学生姓名: 专业班级: 电子科学与技术电子00901班

指导教师: 工作单位: 武汉理工大学信息工程学院

题 目: 数字秒表

一、设计目的

①根据设计要求,完成对数字秒表的设计。

②进一步加强对QuartusⅡ的应用和对VHDL语言的使用。

二、设计内容和要求

①计时精度应大于1/100S,计时器能显示1/100S的时间,提供给计时器内部定时的时钟频率应大于100Hz,这里选用1KHz。

②计时器的最大计时时间为1小时,为此需要6位的显示器,显示的最长时间为59分59.99秒。

③设置有复位和起/停开关,复位开关用来使计数器清零,做好计时准备。起停开关的使用方法与传统的机械式计数器相同,即按一下,启动计时器开始计时,再按一下计时终止。

三、 初始条件

CPLD,按键,时钟信号等。

四、时间安排:

EDA课程设计布置工作 6.11

设计 6.12~6.15

硬件调试 6.17~6.19

撰写设计报告 6.20~6.21

检查硬件、答辩、提交设计报告 6.22

指导教师签名: 年 月 日

系主任(或责任教师)签名 年 月 日

目录

摘 要... I

Abstract II

绪 论... III

一 系统设计方案... 1

二 底层模块设计... 2

2.1 计时电路... 2

2.1.1 时基分频器... 2

2.1.2 100进制计数器... 3

2.1.3 60进制计数器... 3

2.2 计时控制电路... 4

2.3 显示电路... 4

2.3.1 七段译码器... 4

2.3.2 扫描模块... 4

三 顶层原理图... 5

四 系统仿真... 6

4.1计时电路的仿真... 6

4.2计时控制电路的仿真... 8

4.3 显示电路的仿真... 8

五 器件编程与硬件下载... 9

六 心得体会... 10

七 参考文献... 11

附录... 12

摘 要

随着人们生活水平的日益提高,社会体系的日益完善,人们对于各种应用器件的要求也越来越高。秒表作为日常生活中,特别是体育运动中应用的特别广泛,所以精确且方便使用的秒表就被越来越多的人所选择。本秒表计时器用于体育竞赛及各种要求有较精确时的各领域,往常利用中小规模集成电路实现,但一般体积大,使用携带不方便。利用VHDL在FPGA或CPLD上实现1/100秒计时控制器,能充分发挥VHDL与可编程逻辑器件灵活、高效、集成度高的特点。

利用VHDL语言设计基于计算机电路中时钟脉冲原理的数字秒表。该秒表能对0秒~59分59.59秒范围进行计时,显示最长时间是59分59秒。计时精度达到10ms。设计了复位开关和启停开关。复位开关可以在任何情况下使用,使用以后计时器清零,并做好下一次计时的准备。

关键词:EDA技术、VHDL语言、计时器、数码管

Abstract

As people living standard rise increasingly, of the social system is increasingly perfect, for all sorts of people the requirements of the application devices more and more is also high. Stopwatch as daily life, especially sports of the applications of the special extensive, so precise and convenient use a stopwatch is more and more people choose. This stopwatch timer used for sports competition and various requirements have a precise of every field, usual medium scale integrated circuit of realization, but generally is big, the use of portability. Use of VHDL FPGA or CPLD 1/100 of a second time on its controller, can give full play to VHDL and programmable logic devices flexible, efficient, and integration high characteristic.

Use of VHDL language design based on the computer in the circuit principle of the clock pulse digital stopwatch. The stopwatch to 0 SEC-59 points and 59.59 seconds time range, show the longest time is 59 points 59 seconds. Time precision of the 10 ms. The design of the replacement switch and rev. Stop switch. Reset switch can be in any case use, after use timer reset, and do the next time to prepare.

Keywords: EDA technology, VHDL language, timers, digital tube

绪 论

在科技高度发展的今天,集成电路和计算机应用得到了告诉发展,尤其是计算机应用的发展,它在人们日常生活已逐渐崭露头角。大多数电子产品多是由计算机电路组成,如:手机、Mp3等。而在将来的不就他们的身影将会更频繁的出现在我们身边呢。各种家用电器多会实现微电脑技术。电脑各部分在工作时多是以时间为基准的。本文就是基于计算机电路的时钟脉冲信号、状态控制等原理设计出的数字秒表。秒表在很多领域充当中一个重要的角色。在各类比赛中对秒表的精度要求很高,尤其是一些科学实验,他们对时间的精度达到几纳米级别。

VHDL是一种全方位的硬件描述语言,包括系统行为级、寄存器传输级和逻辑门级多个设计层次,支持结构、数据流和行为3种描述形式的混合描述,因此VHDL几乎覆盖了以往各种硬件描述语言的功能,整个自顶向下或自底向上的电路设计过程都可以用VHDL来完成。另外,VHDL还有以下优点:VHDL的宽范围描述能力使它成为高层次设计的核心,将设计人员的工作重心转移到了系统功能的实现和调试上,只需要花较少的精力用于物理实现;VHDL可以用简洁明确的代码描述来进行复杂控制逻辑的设计,灵活且方便,而且也便于设计结果的交流、保存和重用;VHDL的设计不依赖于特定的器件,方便了工艺的转换。

本次设计的目的就是在掌握EDA实验开发系统的初步使用基础上,了解EDA技术,对计算机系统中时钟控制系统进一步了解,掌握状态机工作原理,同时了解计算机时钟卖场是怎么产生和工作的。在掌握所学的计算机组成与结构课程理论知识时,通过对数字秒表的设计,进行理论与实际的结合,提供与计算机有关的设计能力,提高分析、解决计算机技术实际问题的能力。通过课程设计深入了解计算机结构与控制实现的技术,达到课程设计的目标。

一 系统设计方案

根据系统设计要求,系统的组成框图如图1所示。

图1 系统组成框图

系统设计采用自顶向下的设计方法,它主要是由控制模块、时基分频模块、计时模块和显示模块四部分组成。

(1)控制模块

计时控制模块的作用是对计时过程进行控制。计时控制模块可用两个按钮开关来完成秒表的启动、停止和复位。

(2)计时模块

计时模块执行计时功能,计时的方法是对标准时钟脉冲计数。由于计时范围是0秒~59分59.59秒,所以计时器可以由两个60进制计数器和一个100进制计数器构成,其中分和秒采用60进制计数器,毫秒采用100进制计数器。

(3)显示模块

计时显示电路的作用是将计时值在LED七段译码数码管上显示出来。计时电路产生的计时值经过BCD七段译码后,驱动LED数码管。计时显示电路的实现方案采用扫描显示,即每次只驱动一位数码管,各位数码管轮流驱动对应的数码管进行显示。

二 底层模块设计

底层单元模块共有七个,全部用VHDL语言描述。它主要是由计时电路、计时控制电路及显示电路组成。

2.1 计时电路

计时电路执行计时功能,主要是由时基分频器、计数器组成。计时方法是对标准时钟脉冲计数,计数器是由一个100进制计数器和两个60进制计数器构成,其中毫秒位采用100进制计数器,秒位和分位采用60进制计数器。

2.1.1 时基分频器

时基分频器的作用是把输入的时钟信号变为分频输出信号,课设要求提供给计时器内部定时的时钟频率应大于100Hz,这里选用1KHz,即需将试验箱上20MHz时钟信号变频为1KHz,产生0.001秒时钟信号,使该秒表的计时精度达到要求。

分频器实际上就是计数器,假若输入端的时钟频率是f,每当输入N个时钟脉冲时,令输出端反向一次,则输出端对应的时钟频率就是f/(2N),任意改变数值N,就可以得到对应频率的输出脉冲。生成元件如图2.1.1所示:

图2.1.1 时基分频器

2.1.2 100进制计数器

时基分频器的输出端输出频率为1KHz的时钟信号,输入到100进制计数器毫秒模块的时钟端CLK,产生的进位信号CO输入到下一级60进制计数器秒模块中。

2.1.3 60进制计数器

100进制计数器的输出端CO输出频率为1Hz的时钟信号,输入到60进制秒模块的时钟端CLK,产生的进位信号CO(1/60Hz)输入到60进制分模块的时钟输入端。同时,将毫秒、秒、分产生的计数值通过启动/暂停开关、清零开关控制,再通过显示模块实时显示,若清零开关Clear=‘1’,则各位输出均为0,反之正常显示;同时,若启动/暂停开关CS=‘1’,则正常按脉冲计数显示,反之,输出各位输出显示值暂停。生成元件连接图如图2.1.2所示:

图2.1.2 计数器模块

2.2 计时控制电路

此模块实现的功能是:在数码管位选信号Choose的控制下,将毫秒、秒、分位对应输出到译码电路输入端。其元件如图2.2所示:

图2.2 计时控制模块

2.3 显示电路

2.3.1 七段译码器

该模块实现将四位二进制码转换成十进制数字输出,使之在数码管上显示出0、1、2、3、4、5、6、7、8、9十种数字。生成元件如图2.3.1所示:

图2.3.1 七段译码器

2.3.2 扫描模块

此模块实现6位数码管的位选操作功能,其实质就是计数器,输出端接实验箱上的3/8译码器。当扫描频率大于24Hz时,由于发光管的余辉和人眼视觉暂留的作用,使人感觉好像各位数码管同时都在显示,二实际上多位数码管是一位一位轮流显示的,只是轮流的速度非常快,人眼已经无法分辨。其元件如图2.3.2所示:

图2.3.2 扫描模块

三 顶层原理图

以上所描述的模块的程序编写均在同一工程下,由程序生成的元件也在该工程下,所以可以在该工程下再建一原理图作为顶层,将所需要的元件按照要求进行连线,加入输入输出处端口并改名。包层原理图,并将原理图置为顶层文件。

本设计的整体原理图如图3所示:

图3 整体原理图

四 系统仿真

4.1计时电路的仿真

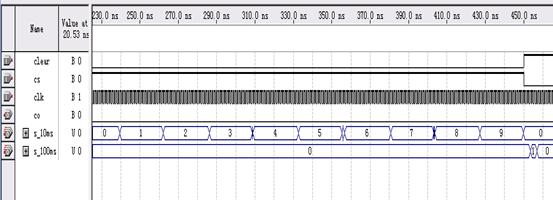

4.1.1 100进制计数器的仿真

图4.1.1 100进制计数器的仿真

分析:clk为时钟脉冲信号,clear是清零信号,cs是启/停信号,s-10ms是十毫秒输出信号,s-100ms是百毫秒输出信号,co是进位信号。当clear=‘0’,cs=‘1’时,每经过十次时钟脉冲,s-10ms加一,当s-10ms满十时,s-100ms加一,以此类推。

4.1.2 60进制计数器秒模块的仿真

图4.1.2 60进制计数器秒模块的仿真

分析:clk为时钟脉冲信号,clear是清零信号,s-1s是秒输出信号,s-10s是十秒输出信号,co是进位信号。当clear=‘0’时,每经过一次时钟脉冲,s-1s加一,当s-1s满十次时,s-10s加一,且co输出一次高电平,以此类推。

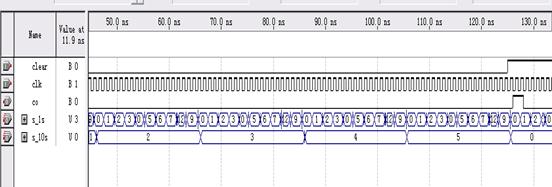

4.1.3 60进制计数器分模块的仿真

图4.1.3 60进制计数器分模块的仿真

分析:clk为时钟脉冲信号,clear是清零信号,s-1min是分输出信号,s-10min是十分输出信号。当clear=‘0’时,每经过一次时钟脉冲,s-1min加一,当s-1min满十次时,s-10min加一,以此类推。

4.2 计时控制电路的仿真

图4.2 控制模块的仿真

分析:在数码管位选信号choose的控制下,分别选择对应的输入端传递给输出端y,当choose=0时,将s-10ms的内容输出,当choose=1时,将s-100ms的内容输出,以此类推。

4.3 显示电路的仿真

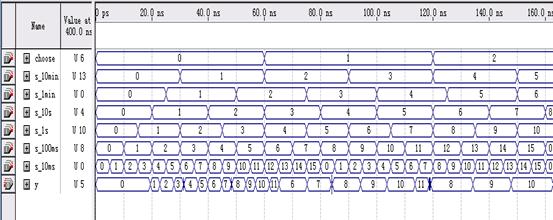

4.3.1扫描电路的仿真

图4.3.1 扫描电路的仿真

分析:clk是时钟信号,count是数码管位选信号,一次轮流扫描第0~5位数码管。

4.3.2 七段译码器的仿真

图4.3.2 七段译码器的仿真

分析:BCD为时钟脉冲输入信号,LED是输出信号。当输入为“0000”,输出为“1111110”, 当输入为“0001”,输出为“0110000”, 当输入为“0010”,输出为“1101101”等等来实现译码功能。

五 器件编程与硬件下载

(1)在Quartus软件中为顶层文件选择好芯片类型,选择引脚后进行编译。

(2)将实验箱端口与计算机相应端口连接,检测试验箱是否可以使用,经检测无误后,关闭试验箱,将主芯片标号对应顶层文件相应引脚标号连线到相应器件处。即输入时钟信号端接试验箱时钟发生电路CLK输出端(用20MHz信号),启动新号段与归零信号端分别接两个拨码开关,输出端count[2..0]分别接3/8译码器的SEL2—SEL0端,输出a,b,c,d,e,f,g,h端接显示译码器的相应输入端,连接好线后打开试验箱电源,将设计好的程序下载到试验箱的芯片上即可测试功能。

六 心得体会

通过本次课设,不仅学到了关于EDA的许多专业知识,同时也享受到了动手的乐趣,还认识到了QuartusⅡ软件的功能非常强大,对于很多关于电方面的元器件都可以用它来实现,这使得在使用的时候非常方便及多变。同时也熟悉了QuartusⅡ的工作环境,可以很熟练的对QuartusⅡ进行常规的操作,快速进行程序编辑和仿真。其实如何有效和快速的找到资料也是课设给与的启发,利用好图书馆和网络,是资源的到最好的利用。另外,与他人交流思想是取得成功的关键,在交流中,不仅强化了自己原有的知识体系也可以扩展自己的思维。通过思考、发问、自己解惑并动手、改进的过程,才能真正的完成课题。

另外,在应用VHDL的过程中,也真正切身领会到了其并行运行与其他软件顺序执行的差别及其在电路上的优越性。用VHDL硬件描述语言的形式来进行数字系统的设计方便灵活,利用EDA软件进行编译优化仿真极大地减少了电路设计时间和可能发生的错误,降低了生产成本。通过这次设计和设计中遇到的问题,也积累了一定的经验,对今后从事电路设计工作会有一定的帮助。

七 参考文献

[1] 潘松,黄继业.EDA技术与VHDL,第2版.北京:清华大学出版社,2007.

[2] 陈小毛,胡机秀.新编数字电路与EDA技术.北京:国防工业出版社,2008.

[3] 夏路易.基于EDA的电子技术课程设计.北京:电子工业出版社,2009.

[4] 宋嘉玉,孙丽霞.EDA实用技术.北京:人民邮电出版社,2006.

[5] 齐洪喜,陆颖.VHDL电路设计实用技术.北京:清华大学出版社,2004.

附录

(一)1KHZ分频

library ieee;

use ieee.std_logic_1164.all;

entity counter10000 is

port(clk:in std_logic;

q:out std_logic);

end counter10000;

architecture behave of counter10000 is

signal q0:std_logic;

begin

process(clk)

variable count:integer range 0 to 10000;

begin

if clk'event and clk='1' then

if count<10000 then count:=count+1;

else q0<=not q0; count:=0;

end if;

end if;

end process;

q<=q0;

end behave;

(二)100进制毫秒模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity cntm100 is

port(cs,clk:in std_logic;

co:buffer std_logic;

s_10ms,s_100ms:buffer std_logic_vector(3 downto 0);

clear:in std_logic);

end ;

architecture behave of cntm100 is

signal clock:std_logic;

begin

process(clk)

variable count1:integer range 0 to 5;

begin

if clk'event and clk='1' then

if count1<5 then count1:=count1+1;

else clock<=not clock; count1:=0;

end if;

end if;

end process;

process(clock,cs,clear)

begin

if clear='0' then

if cs='1' then

if clock'event and clock='1' then co<='0';

if s_10ms=9 then s_10ms<=(others=>'0');

if s_100ms=9 then s_100ms<=(others=>'0');co<=not co;

else s_100ms<=s_100ms+1;

end if;

else s_10ms<=s_10ms+1;

end if;

end if;

else s_10ms<=s_10ms;s_100ms<=s_100ms;

end if;

else s_10ms<=(others=>'0');s_100ms<=(others=>'0');

end if;

end process;

end behave;

(三)60进制秒模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity cntm60miao is

port(clk:in std_logic;

co:buffer std_logic;

s_1s,s_10s:buffer std_logic_vector(3 downto 0);

clear:in std_logic);

end ;

architecture behave of cntm60miao is

begin

process(clk)

begin

if clear='0' then

if clk'event and clk='1' then co<='0';

if s_1s=9 then s_1s<=(others=>'0');

if s_10s=5 then s_10s<=(others=>'0');co<=not co;

else s_10s<= s_10s+1;

end if;

else s_1s<= s_1s+1;

end if;

end if;

else s_1s<=(others=>'0');s_10s<=(others=>'0');

end if;

end process;

end behave;

(四)60进制分模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity cntm60fen is

port(clk:in std_logic;

s_1min,s_10min:buffer std_logic_vector(3 downto 0);

clear:in std_logic);

end ;

architecture behave of cntm60fen is

begin

process(clk)

begin

if clear='0' then

if clk'event and clk='1' then

if s_1min=9 then s_1min<=(others=>'0');

if s_10min=5 then s_10min<=(others=>'0');

else s_10min<= s_10min+1;

end if;

else s_1min<= s_1min+1;

end if;

end if;

else s_1min<=(others=>'0');s_10min<=(others=>'0');

end if;

end process;

end behave;

(五)控制模块

library ieee;

use ieee.std_logic_1164.all;

entity control is

port(s_10ms,s_100ms,s_1s,s_10s,s_1min,s_10min:in std_logic_vector(3 downto 0);

choose:in std_logic_vector(2 downto 0);

y:out std_logic_vector(3 downto 0));

end ;

architecture behave of control is

begin

process(choose)

begin

case choose is

when "000"=>y<=s_10ms;

when "001"=>y<=s_100ms;

when "010"=>y<=s_1s;

when "011"=>y<=s_10s;

when "100"=>y<=s_1min;

when "101"=>y<=s_1min;

when others=>null;

end case;

end process;

end behave;

(六)扫描模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity cntm8 is

port (clk:in std_logic;

count:out std_logic_vector(2 downto 0));

end;

architecture one of cntm8 is

signal q0:std_logic;

begin

process(clk)

variable count1:integer range 0 to 30000;

begin

if clk'event and clk='1' then

if count1<30000 then count1:=count1+1;

else q0<=not q0; count1:=0;

end if;

end if;

end process;

process(q0)

variable CQI:std_logic_vector(2 downto 0);

begin

if q0'event and q0='1' then

if CQI<5 then CQI:=CQI+1;

else CQI:=(others=>'0');

end if;

end if;

count<=CQI;

end process;

end one;

(七)译码器模块

library ieee;

use ieee.std_logic_1164.all;

entity seg7dec is

port(bcdin:in std_logic_vector(3 downto 0);

choose:in std_logic_vector(2 downto 0);

segout :out std_logic_vector (0 to 7));

end;

architecture bev of seg7dec is

begin

process (bcdin,choose)

begin

if choose="010" or choose="100" then

case bcdin is

when "0000" => segout<="11111101";

when "0001" => segout<="01100001";

when "0010" => segout<="11011011";

when "0011" => segout<="11110011";

when "0100" => segout<="01100111";

when "0101" => segout<="10110111";

when "0110" => segout<="10111111";

when "0111" => segout<="11100001";

when "1000" => segout<="11111111";

when "1001" => segout<="11110111";

when others=>null;

end case;

else

case bcdin is

when "0000" => segout<="11111100";

when "0001" => segout<="01100000";

when "0010" => segout<="11011010";

when "0011" => segout<="11110010";

when "0100" => segout<="01100110";

when "0101" => segout<="10110110";

when "0110" => segout<="10111110";

when "0111" => segout<="11100000";

when "1000" => segout<="11111110";

when "1001" => segout<="11110110";

when others=>null;

end case;

end if;

end process;

end ;

本科生课程设计成绩评定表

指导教师签字:

年 月 日

-

数字秒表课程设计报告

沈阳航空航天大学课程设计说明书数字秒表的设计班级学号学生姓名指导教师沈阳航空航天大学课程设计任务书课程名称电子技术综合课程设计院系…

-

数字秒表课程设计报告 -

湖北汽车工业学院课程设计说明书数字秒表的设计班级学号学生姓名指导教师一概述数字式秒表是一种常用的计时工具以其价格低廉走时准确使用方…

-

数字秒表课程设计报告

数字秒表课程设计目录数字秒表设计实验任务书1一设计实验目的1二设计实验说明及要求1三数字秒表组成及功能1四系统硬件要求1五设计内容…

-

课程设计报告数字秒表的设计

电子技术综合试验实验报告班级29021070学号2902107005姓名杨林指导老师刘曦122目录1引言111课程设计的目的112…

-

数字秒表课程设计报告

课程设计总结报告课程名称班级学号姓名指导教师20xx数字秒表陈光胜年7月4日目录1内容摘要22设计课题任务及指标23系统设计方案论…

-

数字秒表设计总结报告

数字秒表课程设计总结报告一课题名称数字秒表设计二内容摘要本实验要求设计一个计数范围在0099秒的数字秒表电路设计基本包括01秒脉冲…

-

电子秒表课程设计报告

电子秒表1设计课题任务及指标1通过本设计的选题方案论证设计计算安装调试资料整理撰写设计报告等环节初步掌握电子工程设计方法和组织实施…

-

微机原理课程设计报告(电子秒表)

微机原理课程设计报告一设计目的培养和锻炼在学习完本门课后综合应用所学理论知识解决实际工程设计和应用问题的能力通过课程设计要求熟悉和…

-

电子秒表课程设计报告

课程设计综合实验报告20xx20xx年度第一学期名称数字电路实验题目电子秒表设计院系电气与电子工程学院班级通信XXXX班学号XXX…

-

电子秒表课程设计报告

西安郵電學院控制系统课程设计报告书系部名称学生姓名专业名称班级时间信息与控制系XXX测控技术与仪器测控XXXX20xx年9月13日…