EDAПЮГЬЩшМЦБЈИц

EDAММЪѕПЮГЬЩшМЦШЮЮёЪщ

ЯЕЃЈВПЃЉЃКЕчзггыЭЈаХЙЄГЬЯЕ зЈвЕЃКЕчЦјЙЄГЬМАЦфздЖЏЛЏ жИЕМНЬЪІЃКаЛУїЛЊ

ГЄЩГбЇдКПЮГЬЩшМЦМјЖЈБэ

ФПТМ

еЊвЊ.................................................................................................................................................. 5

вЛЁЂ ПЮГЬЩшМЦФкШн............................................................................................................................ 6

ЖўЁЂЯЕЭГзмЬхЩшМЦ............................................................................................................................. 6

Ш§ЁЂЯЕЭГШэМўЩшМЦгыЪЕЯж................................................................................................................... 7

1. ИїФЃПщГЬађЫЕУї..................................................................................................................... 7

2.ИїФЃПщЪфШыЪфГіЖЫПкЫЕУїЃК................................................................................................... 18

2.в§НХЗжХфМАЯТдиЙ§ГЬЃК.......................................................................................................... 20

ЫФЁЂЯЕЭГВтЪдгыНсЙћЗжЮіЃК.............................................................................................................. 20

1. дДГЬађЗТецВЈаЮНсЙћ............................................................................................................. 20

2. ВЩбљБрТыФЃПщЗТецВЈаЮНсЙћ.................................................................................................. 21

3. ЗжЦЕФЃПщЗТецВЈаЮНсЙћ......................................................................................................... 21

4. ЪБжгбЁдёФЃПщЗТецВЈаЮНсЙћ.................................................................................................. 21

5. ЫцЛњЪ§ВњЩњФЃПщЗТецВЈаЮНсЙћ............................................................................................... 22

6. ЦЅХфФЃПщЗТецВЈаЮНсЙћ......................................................................................................... 22

ЮхЁЂаФЕУЬхЛс................................................................................................................................... 24

ВЮПМЮФЯз.......................................................................................................................................... 25

еЊвЊ

БОДЮАДМќгЮЯЗПЮГЬЩшМЦЮвУЧжївЊЪЧгІгУVHDLгябдГЬађЩшМЦЃЌгЮЯЗВЮгыепИљОнЯЕЭГжаЕФССЕЦЬсЪОПижЦЯргІАДМќЁЃЖдАДМќПижЦзМШЗЃЌЫЕУїВЮгыепЕФЩэЬхдНСщЛюЃЌЗДгІдНПьЁЃећИіЯЕЭГЛЎЗжЮЊЃКБрТыФЃПщЃЌЗжЦЕФЃПщЃЌЪБжгбЁдёФЃПщЃЈМДЫйЖШПижЦФЃПщЃЉЃЌЫцЛњЪ§ВњЩњФЃПщЃЌБШНЯЦЅХфФЃПщЃЈМДЕУЗжФЃПщЃЉЕШФЃПщЃЌЫљгаЫуЗЈгЩШэМўНсКЯгВМўЕчТЗРДЪЕЯжЃЌРћгУУшЪігябдVHDLЃЌВЂЭЈЙ§XilinxFPGA аОЦЌЪЕЯжЁЃ

вЛЁЂПЮГЬЩшМЦФкШн

гУ8ИіЕЦзїФПБъЃЌгыжЎЖдгІга8ИіАДМќНјааПижЦЁЃУПвЛДЮ8ИіЕЦжаЫцЛњГіЯжвЛИіЕЦДІгкЁАССЁБЕФзДЬЌЃЌдкЕЦССЕФЪБМфФквЊЧѓАДЕНЖдгІЕФАДМќЃЌШєАДЕНдђМг1ЗжЃЌЧвЕЦЯЈУ№ЃЛЗёдђЪЇАмПл1ЗжЁЃ гЮЯЗЗж1-4ЫФИіФбЖШМЖБ№ЃЌУПИіМЖБ№ЕЦЩСССЕФЫйЖШВЛЭЌЃЌМЖБ№дНИпЃЌЫйЖШдНПьЃЌЕЦССЕФЪБМфдНЖЬЁЃЩшЖЈГѕЪМЕШМЖЮЊ1ЃЌСЌајГЩЙІАДМќ5ДЮМг1ЕШМЖЃЌЗжЪ§ВЛЧх0ЃЌСЌајЪЇАм5ДЮМѕ1ЕШМЖЃЌ ЕШМЖЮЊ0ЪБгЮЯЗНсЪјЁЃЩшгаднЭЃ/МЬајКЭПЊЪМ/ЭЃжЙЙІФмЁЃ

ЖўЁЂЯЕЭГзмЬхЩшМЦ

ЯЕЭГПђЭМгыЫЕУї

ИїПђЭМЫЕУїЃК

ЂйЗжЦЕФЃПщЪЧНЋЪфШыЕФFPGA ЕФ50MHz ЕФЪБжгЗжЦЕЮЊИїжжашвЊЕФЪБжгЁЃ

ЂкЪБжгбЁдёФЃПщИљОнАДМќЦЅХфЕФНсЙћЃЌбЁдёЖдгІФбЖШЕФЪБжгЃЌМДбЁдёA,B,C,D ЦфжаЕФвЛИіЃЌ

ШЛКѓПижЦЦфЫћЕФФЃПщЁЃ

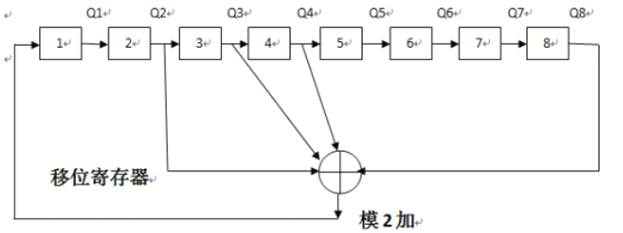

ЂлЫцЛњЪ§ВњЩњФЃПщЪЙгУЕФЪЧm ађСаЃЌЪЧЛљгкЯпадЗДРЁвЦЮЛМФДцЦїЕФдРэЪЕЯжЕФЁЃБОЪЕбщжа

ЪЙгУЕФЪЧ8 МЖm ађСаЗЂЩњЦїЃЌВњЩњвЛИіГЄЖШЮЊ255 ИіЪБжгТіГхжмЦкЕФЖўНјжЦЮБЫцЛњађСаЁЃ

ЦфТпМПђЭМШчЯТЃК

ШЁЦфжаЕФШ§ЮЛ(ШчКѓШ§ЮЛ)ЭЈЙ§3-8 выТыЦїРДЕуССLED ЕЦЁЃ

ЂмВЩбљБрТыФЃПщЃЌНЋ8 ИіЪфШыАДМќНјааВЩбљЃЌБрТыГЩ3 ЮЛЪ§ЁЃ

ЂнЦЅХфФЃПщЃЌЪЧАбгУЛЇЕФАДМќЪфШыжЕгыЖдгІгкССЕЦЕФЫцЛњЪ§НјааБШНЯЃЌШчЙћЯрЭЌдђдіМгЗжЪ§

жЕЃЌВЛЭЌдђМѕЩйЗжЪ§жЕЁЃ

Ш§ЁЂЯЕЭГШэМўЩшМЦгыЪЕЯж

1.ИїФЃПщГЬађЫЕУї

1ЃЉЖЅВуФЃПщ

entity game is

port(clk50m:in std_logic;

k1,k2,k3,k4,k5,k6,k7,k8:in std_logic;

start:in std_logic;

clear:in std_logic;

en:in STD_LOGIC;

win,lose:out std_logic;

led:out std_logic_vector(2 downto 0);

Sel_selout:out std_logic;

Sel7s:out std_logic_vector(6 downto 0);

sound:out std_logic;

LCD_RS : out STD_LOGIC;

LCD_RW : out STD_LOGIC;

LCD_EN : out STD_LOGIC;

data : out STD_LOGIC_VECTOR (3 downto 0));

end game;

architecture Behavioral of game is

signal A,B,C,D,clk,clkout,clk4,clk500,clk6m:std_logic;

signal key:STD_LOGIC_VECTOR (2 downto 0);

signal mwin,mlose:std_logic;

signal en_A,en_B,en_C,en_D: std_logic;

signal mled:std_logic_vector(2 downto 0);

signal score,highscore:STD_LOGIC_VECTOR(11 downto 0);

signal life:STD_LOGIC_VECTOR (7 downto 0);

--ВЩбљБрТыФЃПщЩљУї

component code

port(clk50m:in std_logic;

clk:in std_logic;

start:in std_logic;

k1,k2,k3,k4,k5,k6,k7,k8:in std_logic;

key:out std_logic_vector(2 downto 0));

end component;

--ЗжЦЕФЃПщЩљУї

component divider

Port ( clk50m : in STD_LOGIC;

start:in STD_LOGIC;

A : out STD_LOGIC;

B : out STD_LOGIC;

C: out STD_LOGIC;

D : out STD_LOGIC;

clk500:out STD_LOGIC;

clk4:out std_logic;

clk6m:out std_logic);

end component;

--ЪБжгбЁдёФЃПщЩљУї

component clk_sel

port(clk50m:in std_logic;

start:in std_logic;

A,B,C,D:in std_logic;

en_A,en_B,en_C,en_D:in std_logic;

leda,ledb,ledc,ledd:out std_logic;

clkout:out std_logic);

end component;

--ЫцЛњЪ§ВњЩњФЃПщЩљУї

component random

Port ( clk : in STD_LOGIC;

start:in STD_LOGIC;

en:in STD_LOGIC;

led : out STD_LOGIC_VECTOR (2 downto 0));

end component;

--ЦЅХфФЃПщЩљУї

component compare

port( start:in std_logic;

clear:in std_logic;

en:in std_logic;

clk : in STD_LOGIC;

key : in STD_LOGIC_VECTOR (2 downto 0);

led : in STD_LOGIC_VECTOR (2 downto 0);

win,lose:out STD_LOGIC;

en_A : out STD_LOGIC;

en_B : out STD_LOGIC;

en_C : out STD_LOGIC;

en_D : out STD_LOGIC;

highscore_out:out STD_LOGIC_VECTOR(11 downto 0);

score_out : out STD_LOGIC_VECTOR (11 downto 0);

life_out : out STD_LOGIC_VECTOR (7 downto 0));

end component;

begin

win<=mwin;

lose<=mlose;

led<=mled;

u0:code port map(clk50m,clkout,start,k1,k2,k3,k4,k5,k6,k7,k8,key);

u1:divider port map(clk50m,start,A,B,C,D,clk500,clk4,clk6m);

u2:clk_sel port map(clk50m,start,A,B,C,D,en_A,en_B,en_C,en_D,leda,ledb,ledc,ledd,clkout);

u3:random port map(clkout,start,en,mled);

u4:compare port

map(start,clear,en,clkout,key,mled,mwin,mlose,en_A,en_B,en_C,en_D,highscore,score,life);

u5:music port map(clk6m,clk4,en_A,en_B,en_C,en_D,sound);

u6:lcd port

map(clk500,start,mwin,mlose,highscore,score,life,LCD_RS,LCD_RW,LCD_EN,data);

end Behavioral;

2ЃЉВЩбљБрТыФЃПщ

ЃЈВЩбљБрТыФЃПщЃЌНЋ8 ИіЪфШыАДМќНјааВЩбљЃЌБрТыГЩ3 ЮЛЪ§ЁЃЃЉ

library ieee;

use ieee.std_logic_1164.all;

entity code is

port(clk50m:in std_logic; --50MHz ЕФЪфШыЪБжг

clk:in std_logic; --ЪБжгбЁдёКѓЕУЕНЕФЪБжгЃЌМДВЛЭЌФбЖШЖдгІЕФЪБжг

start:in std_logic; --ПЊЪМаХКХЃЌИпЕчЦНгааЇ

k1,k2,k3,k4,k5,k6,k7,k8:in std_logic; --8 ИіЪфШыАДМќ

key:out std_logic_vector(2 downto 0)); --АДМќБрТыКѓЕУЕНЕФБрТы

end code;

architecture Behavioral of code is

signal flag:std_logic; --БъжОЮЛ

begin

process(clk50m,clk,start)

begin

if start='0' then --ГѕЪМЪБСюflag=0

flag<='0';

elsif clk50m='1' then--гУ50MHz ЕФЪБжгНјааВЩбљБрТыЃЌЧвдквЛИіФбЖШЪБжгФкжЛВЩбљБрТывЛДЮ

if flag='0' then

if k8='1' then

key<="111";

flag<='1'; --flag=1 ЪББэУївбОВЩбљБрТыЭъБЯ

elsif k7='1' then

key<="110";

flag<='1';

elsif k6='1' then

key<="101";

flag<='1';

elsif k5='1' then

key<="100";

flag<='1';

elsif k4='1' then

key<="011";

flag<='1';

elsif k3='1' then

key<="010";

flag<='1';

elsif k2='1' then

key<="001";

flag<='1';

elsif k1='1' then

key<="000";

flag<='1';

end if;

end if;

elsif rising_edge(clk) then --дкФбЖШЪБжгЕФЩЯЩ§биНЋflag жУ0ЃЌБэУїПЩНјааВЩбљБрТы

if flag='1' then

flag<='0';

end if;

end if;

end process;

end Behavioral;

3ЃЉЗжЦЕФЃПщ

ЃЈЗжЦЕФЃПщЪЧНЋЪфШыЕФFPGA ЕФ50MHz ЕФЪБжгЗжЦЕЮЊИїжжашвЊЕФЪБжгЁЃЃЉ

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity game is

Port ( clk50m : in STD_LOGIC; --50MHz ЕФЪфШыЪБжг

start:in STD_LOGIC; --ПЊЪМаХКХЃЌИпЕчЦНгааЇ

A : out STD_LOGIC; --ФбЖШA ЕФжмЦкЮЊ2.5 Уы

B : out STD_LOGIC; --ФбЖШB ЕФжмЦкЮЊ2.0 Уы

C : out STD_LOGIC; --ФбЖШC ЕФжмЦкЮЊ1.5 Уы

D : out STD_LOGIC; --ФбЖШD ЕФжмЦкЮЊ1.0 Уы

clk500:out STD_LOGIC; --clk500=500Hz

clk4:out std_logic; --clk=4Hz

clk6m:out std_logic); --clk6m=6.25MHz

end game;

architecture Behavioral of game is

signal ma,mb,mc,md,m4,m500,m6m:std_logic:='0';

signal cnt1:integer range 1 to 50000;

signal cnt2:integer range 1 to 6250000;

signal cnt3:integer range 1 to 2;

signal cnt4:integer range 1 to 5;

signal cnt5:integer range 1 to 3;

begin

A<=ma;

B<=mb;

C<=mc;

D<=md;

clk500<=m500;

clk6m<=m6m;

clk4<=m4;

process(clk50m)

variable n:integer range 1 to 5:=1;

begin

if rising_edge(clk50m) then --50MHz8 ЗжЦЕКѓЕУЕН6.25MHz ЕФаХКХclk6m

n:=n+1;

if n=5 then

m6m<=not m6m;

n:=1;

end if;

if cnt1=50000 then --50MHz100000 ЗжЦЕКѓЕУЕН500Hz ЕФаХКХclk500

m500<=not m500;

cnt1<=1;

else

cnt1<=cnt1+1;

end if;

if cnt2=6250000 then ----50MHz12500000 ЗжЦЕКѓЕУЕН4Hz ЕФаХКХclk4

m4<=not m4;

cnt2<=1;

else

cnt2<=cnt2+1;

end if;

end if;

end process;

process(start,m4,md)

begin

if start='0' then --start=0 ЪБГѕЪМЛЏ

ma<='0';

mb<='0';

mc<='0';

md<='0';

cnt3<=1;

cnt5<=1;

else

if rising_edge(m4) then --4Hz ЪБжг4 ЗжЦЕКѓЕУЕН1Hz

if cnt3=2 then

cnt3<=1;

md<=not md;

else

cnt3<=cnt3+1;

end if;

if cnt4=5 then --4Hz ЪБжг10 ЗжЦЕКѓЕУЕН0.4Hz ЪБ

ma<=not ma;

cnt4<=1;

else

cnt4<=cnt4+1;

end if;

if cnt5=3 then --4Hz ЪБжг6 ЗжЦЕКѓЕУЕН0.67Hz ЪБ

mc<=not mc;

cnt5<=1;

else

cnt5<=cnt5+1;

end if;

end if;

if rising_edge(md) then --1Hz ЪБжг2 ЗжЦЕКѓЕУЕН0.5Hz ЕФЪБ

mb<=not mb;

end if;

end if;

end process;

end Behavioral;

4ЃЉЪБжгбЁдёФЃПщ

ЃЈЪБжгбЁдёФЃПщИљОнАДМќЦЅХфЕФНсЙћЃЌбЁдёЖдгІФбЖШЕФЪБжгЃЌМДбЁдёA,B,C,D Цф жаЕФвЛИіЃЌШЛКѓПи жЦ ЦфЫћЕФФЃПщЁЃЃЉ

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity clk_sel is

port(clk50m:in std_logic; --50MHz ЕФЪфШыЪБжг

start:in std_logic; --ПЊЪМаХКХЃЌИпЕчЦНгааЇ

A,B,C,D:in std_logic; --A,B,C,D ЗжБ№ЖдгІФбЖШAЃЌBЃЌCЃЌD ЕФЪБжг

en_A,en_B,en_C,en_D:in std_logic;--en_A,en_B,en_C,en_D ЗжБ№ЮЊAЃЌBЃЌCЃЌD ЕФЪЙФмаХКХ

led_selout:out std_logic;

led7s:out std_logic_vector(6 downto 0);--ВЛЭЌЕФФбЖШгУВЛЭЌЕФLED РДжИЪО

clkout:out std_logic); --ВЛЭЌЕФФбЖШЪфГіЖдгІЕФФбЖШЪБжг

end clk_sel;

architecture Behavioral of clk_sel is

signal m:std_logic_vector(3 downto 0);

signal clk:std_logic:='0';

Begin

led_selout<='1';

m<=en_A&en_B&en_C&en_D;

clkout<=clk;

process(clk50m)

begin

if start='0' then

clk<='0';

elsif rising_edge(clk50m) then

if m=8 then --ЕБen_A='1'ЪБЃЌЪБжгЖдгІЮЊФбЖШA ЕФЪБжгЃЌЧвжИЪОФбЖШA ЕФLEDСС

clk<=A;

led7s<="1111001";

elsif m=4 then --ЕБen_B='1'ЪБЃЌЪБжгЖдгІЮЊФбЖШB ЕФЪБжгЃЌЧвжИЪОФбЖШB ЕФLED СС

clk<=B;

led7s<="0100100";

elsif m=2 then --ЕБen_C='1'ЪБЃЌЪБжгЖдгІЮЊФбЖШC ЕФЪБжгЃЌЧвжИЪОФбЖШC ЕФLED СС

clk<=C;

led7s<="0110000";

elsif m=1 then --ЕБen_D='1'ЪБЃЌЪБжгЖдгІЮЊФбЖШD ЕФЪБжгЃЌЧвжИЪОФбЖШD ЕФLED СС

clk<=D;

led7s<="0011001";

else

clk<='0';

end if;

end if;

end process;

end Behavioral;

5ЃЉЫцЛњЪ§ВњЩњФЃПщ

ЃЈЫцЛњЪ§ВњЩњФЃПщЪЙгУЕФЪЧm ађСаЃЌЪЧЛљгкЯпадЗДРЁвЦЮЛМФДцЦїЕФдРэЪЕЯжЕФЁЃБОЪЕбщжаЪЙгУЕФЪЧ8 МЖ m ађСаЗЂЩњЦїЃЌВњЩњвЛИіГЄЖШЮЊ255 ИіЪБжгТіГхжмЦкЕФЖўНјжЦЮБЫцЛњађСаЁЃЃЉ

entity random is

Port ( clk : in STD_LOGIC; --ФбЖШЪБжг

start:in STD_LOGIC; --ПЊЪМаХКХЃЌИпЕчЦНгааЇ

en:in STD_LOGIC; --днЭЃаХКХЃЌen=0 ЪБднЭЃ

led : out STD_LOGIC_VECTOR (2 downto 0)); --ВњЩњЕФШ§ЮЛЫцЛњЪ§

end random;

architecture Behavioral of random is

signal m:std_logic_vector(7 downto 0):="10000000";

begin

led<=m(2 downto 0);

process(clk,en,start)

begin

if start='0' then

m<="11000011";

elsif en='0' then

m<=m;

elsif rising_edge(clk) then

m(7 downto 1)<=m(6 downto 0);

m(0)<=m(7) xor m(3) xor m(2) xor m(1);

end if;

end process;

end Behavioral;

6ЃЉЦЅХфФЃПщ

ЃЈЦЅХфФЃПщЃЌЪЧАбгУЛЇЕФАДМќЪфШыжЕгыЖдгІгкССЕЦЕФЫцЛњЪ§НјааБШНЯЃЌШчЙћЯрЭЌдђдіМгЗжЪ§жЕЃЌВЛЭЌдђ МѕЩйЗжЪ§жЕЁЃЃЉ

library ieee;

use ieee.std_logic_1164.all;

entity compare is

port( start:in std_logic; --ПЊЪМаХКХЃЌИпЕчЦНгааЇ

clear:in std_logic; --зюИпЗжЧхСуаХКХЃЌclear=1 ЪБЧхГ§зюИпЗжМЭТМ

en:in std_logic; --днЭЃаХКХЃЌen=0 ЪБднЭЃ

clk : in STD_LOGIC; --clk50m ЮЊ50MHz ЕФЪфШыЪБжгЃЌclk ЮЊФбЖШЪБжг

key : in STD_LOGIC_VECTOR (2 downto 0); --key ЮЊБрТыКѓЕУЕНЕФБрТыжЕ

led : in STD_LOGIC_VECTOR (2 downto 0);--led ЮЊВњЩњЕФШ§ЮЛЫцЛњЪ§

win,lose:out STD_LOGIC; --win=1 БэУїгЮЯЗЪЄРћЃЌlose=1 БэУїгЮЯЗЪЇАм

en_A : out STD_LOGIC; --ФбЖШA ЕФЪЙФмаХКХ

en_B : out STD_LOGIC; --ФбЖШB ЕФЪЙФмаХКХ

en_C : out STD_LOGIC; --ФбЖШC ЕФЪЙФмаХКХ

en_D : out STD_LOGIC; --ФбЖШD ЕФЪЙФмаХКХ

highscore_out:out STD_LOGIC_VECTOR(11 downto 0); --зюИпЗж

score_out : out STD_LOGIC_VECTOR (11 downto 0); --ЕБЧАЗжЪ§

end compare;

architecture Behavioral of compare is

signal mscore,mhighscore:integer range 0 to 999;

signal result,mwin,mlose:std_logic;

signal cnt1:integer range 0 to 4;

signal cnt2:integer range 0 to 1;

type state is(na,nb,nc,nd);

signal nandu:state;

begin

result<=mwin or mlose; --ЕБresult=1 ЪБгЮЯЗНсЪјЃЌLCD ЩЯЛсЯдЪОЪфЛђгЎ

win<=mwin;--ЕУ5 ЗжМгвЛЬѕУќЃЌЪЇЮѓвЛДЮПлвЛЗжЃЌЪЇЮѓДяЕН2 ДЮПлвЛЬѕУќЃЌЕБЗжЪ§ЮЊ0 ЪБЃЌЪЇЮѓвЛДЮВЛМѕЗжЃЌЕЋПлвЛЬѕУќ

process(clk,start,en,clear)

begin

if mscore>mhighscore then

mhighscore<=mscore;

else

mhighscore<=mhighscore;

end if;

if start='0' then

mscore<=0; --ГѕЪМЗжЪ§ЮЊ0

cnt1<=0;

mhighscore<=mhighscore;

cnt2<=0;

mwin<='0';

mlose<='0';

nandu<=na;

en_A<='1';

en_B<='0';

en_C<='0';

en_D<='0';

elsif clear='1' then

mhighscore<=0;

elsif en='0' then

mscore<=mscore;

mhighscore<=mhighscore;

elsif rising_edge(clk) then

if result='0' then

if led=key then

elsif mscore=999 then

mwin<='1';

elsif mscore<999 then

mscore<=mscore+1;

end if;

else

if mscore=0 and mlife=0 then

mscore<=0;

mlose<='1';

elsif mlife=0 then

mscore<=mscore;

mlose<='1';

elsif mscore=0 then

mscore<=0;

else

mscore<=mscore-1;

end if;

end if;

end if;

end if;

case nandu is

when na=> --ЕБЗжЪ§аЁгк5 ЗжЪБЃЌФбЖШЮЊA

en_A<='1';

en_B<='0';

en_C<='0';

en_D<='0';

if mscore>=5 and mscore<10 then

nandu<=nb;

else

nandu<=na;

end if;

when nb=> --ЕБЗжЪ§дк5-10 жЎМфЪБЃЌФбЖШЮЊB

en_A<='0';

en_B<='1';

en_C<='0';

en_D<='0';

if mscore>=10 and mscore<15 then

nandu<=nc;

else

nandu<=nb;

end if;

when nc=> --ЕБЗжЪ§дк10-15 жЎМфЪБЃЌФбЖШЮЊC

en_A<='0';

en_B<='0';

en_C<='1';

en_D<='0';

if mscore>=15 and mscore<20 then

nandu<=nd;

else

nandu<=nc;

end if;

when nd=> --ЕБЗжЪ§дк15 вдЩЯЪБЃЌФбЖШЮЊD

en_A<='0';

en_B<='0';

en_C<='0';

en_D<='1';

nandu<=nd;

when others=>

en_A<='1';

en_B<='0';

en_C<='0';

en_D<='0';

nandu<=na;

end case;

end if;

end process;

process(clk)

begin

if falling_edge(clk) then

if mscore>=900 then

score_out(11 downto 8)<=x"9";

if (mscore-900)>=90 then

score_out(7 downto 4)<=x"9";

score_out(3 downto 0)<=conv_std_logic_vector((mscore-990),4);

elsif (mscore-900)>=80 then

score_out(7 downto 4)<=x"8";

score_out(3 downto 0)<=conv_std_logic_vector((mscore-980),4);

elsif (mscore-900)>=70 then

score_out(7 downto 4)<=x"7";

score_out(3 downto 0)<=conv_std_logic_vector((mscore-970),4);

elsif (mscore-900)>=60 then

score_out(7 downto 4)<=x"6";

score_out(3 downto 0)<=conv_std_logic_vector((mscore-960),4);

elsif (mscore-900)>=50 then

score_out(7 downto 4)<=x"5";

score_out(3 downto 0)<=conv_std_logic_vector((mscore-950),4);

elsif (mscore-900)>=40 then

score_out(7 downto 4)<=x"4";

score_out(3 downto 0)<=conv_std_logic_vector((mscore-940),4);

elsif (mscore-900)>=30 then

score_out(7 downto 4)<=x"3";

score_out(3 downto 0)<=conv_std_logic_vector((mscore-930),4);

elsif (mscore-900)>=20 then

score_out(7 downto 4)<=x"2";

score_out(3 downto 0)<=conv_std_logic_vector((mscore-920),4);

elsif (mscore-900)>=10 then

score_out(7 downto 4)<=x"1";

score_out(3 downto 0)<=conv_std_logic_vector((mscore-910),4);

else

score_out(7 downto 4)<=x"0";

score_out(3 downto 0)<=conv_std_logic_vector((mscore-900),4);

end if;

if mhighscore>=900 then

highscore_out(11 downto 8)<=x"9";

if (mhighscore-900)>=90 then

highscore_out(7 downto 4)<=x"9";

highscore_out(3 downto 0)<=conv_std_logic_vector((mhighscore-990),4);

elsif (mhighscore-900)>=80 then

highscore_out(7 downto 4)<=x"8";

highscore_out(3 downto 0)<=conv_std_logic_vector((mhighscore-980),4);

elsif (mhighscore-900)>=70 then

highscore_out(7 downto 4)<=x"7";

highscore_out(3 downto 0)<=conv_std_logic_vector((mhighscore-970),4);

elsif (mhighscore-900)>=60 then

highscore_out(7 downto 4)<=x"6";

highscore_out(3 downto 0)<=conv_std_logic_vector((mhighscore-960),4);

elsif (mhighscore-900)>=50 then

highscore_out(7 downto 4)<=x"5";

highscore_out(3 downto 0)<=conv_std_logic_vector((mhighscore-950),4);

elsif (mhighscore-900)>=40 then

highscore_out(7 downto 4)<=x"4";

highscore_out(3 downto 0)<=conv_std_logic_vector((mhighscore-940),4);

elsif (mhighscore-900)>=30 then

highscore_out(7 downto 4)<=x"3";

highscore_out(3 downto 0)<=conv_std_logic_vector((mhighscore-930),4);

elsif (mhighscore-900)>=20 then

highscore_out(7 downto 4)<=x"2";

highscore_out(3 downto 0)<=conv_std_logic_vector((mhighscore-920),4);

elsif (mhighscore-900)>=10 then

highscore_out(7 downto 4)<=x"1";

highscore_out(3 downto 0)<=conv_std_logic_vector((mhighscore-910),4);

else

highscore_out(7 downto 4)<=x"0";

highscore_out(3 downto 0)<=conv_std_logic_vector((mhighscore-900),4);

end if;

end process;

end Behavioral;

2.ИїФЃПщЪфШыЪфГіЖЫПкЫЕУїЃК

1)ЖЅВуФЃПщgame

ЪфШыаХКХINЃК

clk50m:in std_logic; --50MHz ЕФЪфШыЪБжг

k1,k2,k3,k4,k5,k6,k7,k8:in std_logic; --8 ИіЪфШыАДМќ

start:in std_logic; --ПЊЪМаХКХЃЌИпЕчЦНгааЇ

clear:in std_logic; --зюИпЗжЧхСуаХКХЃЌclear=1 ЪБЧхГ§зюИпЗжМЭТМ

en:in STD_LOGIC; --днЭЃаХКХЃЌen=0 ЪБднЭЃ

ЪфГіаХКХOUTЃК

win,lose:out std_logic; --win=1 БэУїгЮЯЗЪЄРћЃЌlose=1 БэУїгЮЯЗЪЇАм

led:out std_logic_vector(2 downto 0); --ВњЩњЕФШ§ЮЛЫцЛњЪ§ЃЌЫЭЕН74LS138НјаавыТыЃЌДгЖјЕуССвЛИіLED

leda,ledb,ledc,ledd:out std_logic; --ВЛЭЌЕФФбЖШЗжБ№гУВЛЭЌЕФLED ЕЦРДжИЪО

sound:out std_logic; --ЮЊЪфГіЕФРЎАШаХКХ

LCD_RS : out STD_LOGIC;

LCD_RW : out STD_LOGIC;

LCD_EN : out STD_LOGIC;

data : out STD_LOGIC_VECTOR (3 downto 0)); --Ъ§ОнаХКХЪфГі

2)ВЩбљБрТыФЃПщcode

ЃЈЪфШыЮЊ50MHz ЕФЪБжгаХКХclk50mЃЌбЁдёЕФФбЖШаХКХclkЃЌ

ПЊЪМаХКХstartЃЌвдМААЫИіАДМќЃЛЪфГіЮЊБрТыжЕkeyЁЃЃЉ

ЪфШыаХКХINЃК

clk50m:in std_logic;

clk:in std_logic;

start:in std_logic;

k1,k2,k3,k4,k5,k6,k7,k8:in std_logic;

ЪфГіаХКХOUTЃК

key:out std_logic_vector(2 downto 0)

3)ЗжЦЕФЃПщdivider

ЃЈЪфШыЮЊ50MHz ЕФЪБжгаХКХЃЌПЊЪМаХКХstartЃЛ

ЪфГіЮЊA,B,C,D ЫФжжФбЖШЕФЪБжгЁЃЃЉ

ЪфШыаХКХINЃК

clk50m : in STD_LOGIC;

start:in STD_LOGIC;

ЪфГіаХКХOUTЃК

A : out STD_LOGIC;

B : out STD_LOGIC;

C: out STD_LOGIC;

D : out STD_LOGIC;

clk500:out STD_LOGIC;

clk4:out std_logic;

clk6m:out std_logic

4 )ЪБжгбЁдёФЃПщclk_sel

ЃЈЪфШыЮЊA,B,C,D ЫФжжФбЖШЕФЪБжгЃЌ50MHz ЕФЪБжгclk50mЃЌПЊЪМаХКХstartЃЌ

en_A,en_B,en_C,en_D ЫФжжЪБжгЕФбЁдёаХКХЃЛ

ЪфГіЮЊledaЃЌledbЃЌledcЃЌledd ЫФИіЖдгІВЛЭЌФбЖШЕФLEDЃЌбЁдёЕФA,B,C,D ФбЖШжаЕФвЛИіЪБжгЁЃЃЉ

ЪфШыаХКХINЃК

clk50m:in std_logic;

start:in std_logic;

A,B,C,D:in std_logic;

en_A,en_B,en_C,en_D:in std_logic;

ЪфГіаХКХOUTЃК

leda,ledb,ledc,ledd:out std_logic;

clkout:out std_logic

5)ЫцЛњЪ§ВњЩњФЃПщrandom

ЃЈЪфШыЮЊбЁдёЕФФбЖШЪБжгclkЃЌднЭЃаХКХenЃЌПЊЪМаХКХstartЃЛ

ЪфГіЮЊВњЩњЕФШ§ЮЛЫцЛњЪ§ЁЃЃЉ

ЪфШыаХКХINЃК

clk : in STD_LOGIC;

start:in STD_LOGIC;

en:in STD_LOGIC;

ЪфГіаХКХOUTЃК

led : out STD_LOGIC_VECTOR (2 downto 0)

6)ЦЅХфФЃПщcompare

ЃЈЪфШыбЁдёЕФФбЖШЪБжгclkЃЌзюИпЗжЧхСуаХКХclearЃЌднЭЃаХКХenЃЌПЊЪМаХКХstartЃЌБрТыkeyЃЌ

ЫцЛњЪ§ledЃЛ

ЪфГіЮЊзюИпЗжhighscore_out,ЕБЧАЗжЪ§score_outЃЌВЛЭЌФбЖШЕФбЁдёаХКХ en_A,en_B,en_C,en_D,ЪфаХКХloseЃЌгЎаХКХwinЁЃЃЉ

ЪфШыаХКХINЃК

start:in std_logic;

clear:in std_logic;

en:in std_logic;

clk : in STD_LOGIC;

key : in STD_LOGIC_VECTOR (2 downto 0);

led : in STD_LOGIC_VECTOR (2 downto 0);

ЪфГіаХКХOUTЃК

win,lose:out STD_LOGIC;

en_A : out STD_LOGIC;

en_B : out STD_LOGIC;

en_C : out STD_LOGIC;

en_D : out STD_LOGIC;

highscore_out:out STD_LOGIC_VECTOR(11 downto 0);

score_out : out STD_LOGIC_VECTOR (11 downto 0);

life_out : out STD_LOGIC_VECTOR (7 downto 0));

2.в§НХЗжХфМАЯТдиЙ§ГЬЃК

в§НХЗжЦЕЭМШчЯТЃК

ЫФЁЂЯЕЭГВтЪдгыНсЙћЗжЮіЃК

1.дДГЬађЗТецВЈаЮНсЙћ

2.ВЩбљБрТыФЃПщЗТецВЈаЮНсЙћ

гЩЗТецЭМПЩжЊЃЌдквЛИіclk жмЦкФкЫфШЛгаЖрДЮАДМќЪфШыЃЌЕЋжЛгаЕквЛДЮЕФАДМќгааЇЃЌМДдквЛ

Иіclk жмЦкФкжЛВЩбљБрТывЛДЮЁЃ

3.ЗжЦЕФЃПщЗТецВЈаЮНсЙћ

гЩгкA,B,C,D ЕФЦЕТЪНЯаЁЃЌЕУВЛЕНЗТецНсЙћЃЌЫљвдНЋДњТыЩеТМЕНАхзгЩЯЭЈЙ§LED ЕЦЕФССУ№РД

ЙлВьa,b,c,d ЕФЦЕТЪЃЌЙлВьНсЙћгыдЄЦкЯрЗћЁЃ

4.ЪБжгбЁдёФЃПщЗТецВЈаЮНсЙћ

5.ЫцЛњЪ§ВњЩњФЃПщЗТецВЈаЮНсЙћ

гЩЗТецЭМПЩжЊЃЌВњЩњЕФled ПЩШЯЮЊЪЧЫцЛњЪ§ЁЃ

6.ЦЅХфФЃПщЗТецВЈаЮНсЙћ

гЩвдЩЯВЈаЮПЩПДГіЃЌЦЅХфЪБЃЌЗжЪ§діМгвЛЗжЃЌСЌајЗжЪ§діМг5ЗжЃЌФбЖШдіМгвЛМЖЃЌЗжЪ§дк5

вдЯТЪБФбЖШЮЊAЃЌдк5-10 жЎМфЪБФбЖШЮЊB,дк10-15 жЎМфЪБФбЖШЮЊC,дк15 вдЩЯЪБФбЖШЮЊD,

ВЛЦЅХфЪБЃЌЗжЪ§МѕвЛЗжЃЌСЌајЗжЪ§Мѕ5ДЮМѕ1ЕШМЖЃЌЕШМЖЮЊ0ЪБгЮЯЗНсЪјЁЃзюИпЗжжЛЩ§ВЛНЕЁЃ

зюИпЗжБШЕБЧАЗжЪ§жЭКѓвЛИіжмЦкЁЃЕБЕШМЖЮЊ0 ЪБгЮЯЗНсЪјЁЃ

ЮхЁЂаФЕУЬхЛс

етДЮПЮГЬЩшМЦЖдгкУЛбЇКХEDAММЪѕЕФЭЌбЇРДЫЕЪЧРЇФбЕФЁЃдкЩшМЦГЬађЕФГѕЦкНзЖЮЮвЖдгкећИіVHDLГЬађЩшМЦСїГЬЕФЗНЯђадЕФАбЮеВЛЪЧКмзМШЗЃЌИеПЊЪМдкФЃПщЕФЩшМЦОЭГіЯжСЫКмДѓЕФЮЪЬтЃЌЖдгкИїИіФЃПщЙІФмЪЕЯжЕФОпЬхДњТыАбЮевВВЛЪЧКмУїШЗЃЌдкетаЉФЃПщжаЃЌБШНЯгаФбЖШЕФЪЧЗжЪ§гыАДМќЦЅХфЕФХаЖЈЃЌвдМАХаЖЈжЎКѓЕФМгЗжЩ§МЖЃЌЛЙгавЛИіЪЧLEDЕФЯдЪОЃЌдкВщСЫзЪСЯКѓВХжегкЕУГіСЫНсТлЁЃ

дкетРяЃЌЮвЯывЊжИГіЕФЪЧЦЅХфФЃПщЃЌзюЯШЪЧгУФбЖШЪБжгНјааЦЅХфМгМѕЗжЃЌЕЋЪЧЗТецЕУВЛЕНе§ШЗНсЙћЃЌгкЪЧОЭИФгУ50MHz ЕФЦЕТЪНјааЦЅХфМгМѕЗжЃЌашвЊЩшжУБъжОЮЛЃЌБЃжЄдквЛИіФбЖШЪБжгФкжЛЦЅХфвЛДЮЃЌСэЭташвЊНЋБрТыбгЪБвЛИіФбЖШжмЦкЃЌжЛгадкЧАКѓСНДЮАДМќВЛвЛбљЪБВХНјааЦЅХфЃЌетбљЕФКУДІОЭЪЧЗжЪ§ИќаТКмПьЃЌМИКѕУЛгабгЪБЃЌЕЋШБЕуОЭЪЧШчЙћЧАКѓСНДЮАДМќвЛбљЪБОЭВЛНјааЦЅХфЃЌМШВЛМгЗжвВВЛМѕЗжЃЌВЛТњзувЊЧѓЁЃзюКѓЮвУЧВЩгУЕФАьЗЈЪЧгУФбЖШЪБжгЕФЩЯЩ§биНјааЦЅХфЃЌдкФбЖШЪБжгЕФЯТНЕбиНјааМгМѕЗжЃЌетбљФмТњзувЊЧѓЃЌВЛЙ§МгМѕЗжШдгавЛЖЈЕФбгГйЁЃ

ВЮПМЮФЯз

ХЫЫЩЁЂЛЦМЬвЕжјЁЖEDAММЪѕЪЕгУНЬВФЁЗЁЊЁЊVHDLАцЃЈЕкЫФАцЃЉ ПЦбЇГіАцЩч