���ֵ�����EDAʵ�鱨��

�繤����ʵϰ

ʵ�鱨��

�� ��

�� �� �ƿ�0901

ѧ �� 200909010116

һ�� ʵ��Ŀ�ģ�

1�����ն�λ��������������Ʒ�����

2������ʮ���ơ���ʮ���ƺͶ�ʮ�Ľ��Ƽ���������Ʒ�����

3����������ܵ�����ԭ������̷�����

4������CPLD�����IJ�λ���Ʒ�����

���� ʵ��Ҫ��

����Ҫ����ʱ���֡��������ʾ���ܣ��Զ�ʮ��Сʱѭ����ʱ��

��չҪ���е���ʱ��Ĺ����Լ����㱨ʱ���ܡ�

���� ʵ��ԭ����

? �������֣����һ�����ֵ���ʱ�ӡ�

ͨ������ʵ��Ҫ��ó���ѡ��74LS163оƬ����6Ƭ������ͬ�������ķ����������ؼ�ʱ����ͬһԴ�����������CLK������ENTʹ�ܶ�ʵ�ּ���������λ��ʱ�����λ��ʱ����Ϊ60���ƣ�ʱλ��ʱ��Ϊ24���ơ�

? ѡ�����֣�������ʵ��Уʱ����������㱨ʱ���ܡ�

ͨ������ʵ��Ҫ��ó���1.�������ֵ����ӷֵ�λ��ʱ��λ��ʹ�ܶˣ�ENT�����루��ʹ�ܶ˵�����������֣�һ������Ȼ���룬һ����������Ӧ��ƽ�ź��ֶ�����ʹ���źţ�ʵ��Уʱ��2.������֤�����ֵ����ӵ����Ϊ59��50��ʱ����һ������·���õ�Դ���������źţ��������ŵ����������Ӧ�ĸߵ͵�ƽ��ͨ������ʵ�����㱨ʱ��

1. ��λ��ʱ��·��ƣ�60���ƣ�

���λ������ʮ���Ƽ�������74163��װ���������������źŴ���������9�루���λ���1001B��ʱ�����λ���㣻���λ�����������Ƽ�������74163��װ��������9��ʱ�����λоƬENT����ߵ�ƽ���ɴ˴���������59�루���λ���1001B�����λ���0101B��ʱ�����λ���㡣

2����λ��ʱ��·��ƣ�60���ƣ�

��λ��ʱ��·����λ��ʱ��·��ʱԭ���������ֻ�ڴ���������ʹ���ź�������һ�����졣�ֵ�λ������ʮ���Ƽ�������74163��װ��������59��ʱ����������9��59�루�ֵ�λ���Ϊ1001H�����λ���0101B�����λ���1001B��ʱ���ֵ�λ���㣻�ָ�λ�����������Ƽ�������74163��װ��������9��59��ʱ���ָ�λоƬENT����ߵ�ƽ���ɴ˴���������59��59�루�ָ�λ���Ϊ0101B���ֵ�λ���Ϊ1001B�����λ���0101B�����λ���1001B��ʱ���ָ�λ���㡣

3��ʱλ��ʱ��·��ƣ�24���ƣ�

ʱ��λ������ʮ�����ģ����Ƽ�������74163��װ��������59��59��ʱ����������9ʱ59��59�루ʱ��λ���Ϊ1001B���ָ�λ���Ϊ0101B���ֵ�λ���Ϊ1001B�����λ���0101B�����λ���1001B��������23ʱ59��59�루ʱ��λ���Ϊ0010B��ʱ��λ���Ϊ0011B���ָ�λ���Ϊ0101B���ֵ�λ���Ϊ1001B�����λ���0101B�����λ���1001B��ʱ��ʱ��λ���㣻ʱ��λ�����������Ƽ�������74163��װ��������9ʱ59��59��ʱ��ʱ��λоƬENT����ߵ�ƽ���ɴ˴���������23ʱ59��59��ʱ��ʱ��λ���㡣

1�� Уʱ��·

�������š����źͷ��ŵĻ������ԣ�ͨ������ʵ��Ҫ��ó����������ֵ����ӷֵ�λ��ʱ��λ��ʹ�ܶˣ�ENT�����루��ʹ�ܶ˵�����������֣�һ������Ȼ���룬һ����������Ӧ��ƽ�ź��ֶ�����ʹ���źţ�ʵ��Уʱ��

2�� ���㱨ʱ��·

������֤�����ֵ����ӵ����Ϊ59��50��ʱ����һ������·���õ�Դ���������źţ��������ŵ����������Ӧ�ĸߵ͵�ƽ��ͨ������ʵ�����㱨ʱ��

�ġ� ʵ��������·ͼ�����沨���Լ�˵������

![˵��: C:\Users\MD\Documents\Tencent Files\641743819\Image\BSZ(9(A`){%DT]D`X66R(PK.jpg](https://upload2.fanwen118.com/wk001/4075368/4075368_img_004.jpg)

˵����

����ʵ������ﵽԤ��Ŀ�ꡣͨ������ʵ�����ۺ�����ѧ�������ֵ��ӡ��ɱ���������Ȼ���֪ʶ���������Ҷ�����ƱȽϸ��ӵ���������������ͬʱ������Ϥ������������ʹ��EDA����������Զ�������������������ķ���������������롢���롢�������桢���غ�Ӳ�������ȫ���̡���ʵ��Ĺ����У�����˼ά���ޣ��Լ�������һϵ�����⣬�ҵø�λʵ��ָ����ʦ��Ϥ��ָ����ͬѧ�ǵ����İ�����ʵ�����˳�����С�

�����һ��ѭ���Ĺ��̡���·������У��Լ�������ᵽ�ˡ������֮����������Լ���δͳ��ȫ�֣�ȴ�ֻ���ģ����ƵĽϿ�������Եã�ȴ�������ۺϵ��Ż����ơ�һ�Σ���ʱ��·�ڱ��������ȴ����ʾ��ȷ�IJ��Σ���Ϊ�Լ���������Ҷ�ʱ�������ɻ�����ϸ�۲���ҷ�������Ƿȱ�������ʱ��·��ּ�ʱ��·�����Ӵ�����ע��˱����ֵ�ʹ�ܣ����������νӡ��ҳ��˴����Ҿ��������������ÿһ������ģ�飬���������棬����ÿ������ģ�飬��ʵ�ָ��ֹ���ģ��ľ��幦�ܣ��ٽ����ֹ���ģ�����������������ܵ�ϵͳ��������幦�ܵ�ʵ�֡�

��·�Ĵ�У���������ʶ�����ܼ�����ɡ���������Ƴ��Σ����·��Ҳ���������Լ�������ʹ�õIJ�̫���֣��Բ���������˵��ߡ��ص��˽ڵ㣬�ڱ���ʱ���ִ����Լ���ͼ������ʹ�÷��ֲ�����ʱ���������������⼫���ӻ���ʵ��Ľ��ȡ�

�ڽ�������Ӳ������ʱ���ź���������ʵ��嵼���������ޣ���ֻ����ͬѧһ����������Ӳ�����ߣ���Ӳ������ʱ�䲻����ԣ�����ǿ�ϲ������Ӳ������ʱ����֤�˻�����ʱ��·��Ƶ���ȷ�ԣ�ͬʱ�ַ�����һЩ���⣬���縨������Уλ��ʵ��ʱӰ�쵽�˽�λ��ͨ���������ģ���·���Բ������ơ�

ͨ������ʵ�飬�ұ�������Ƶ�·��Ȥζ����������ͬʱ��ʶ����֪�н�ϣ�����ʵ�����Ҫ�ԣ�����֪���˱����쳵�ıˣ�ʵ���У���������ʹ�õò�̫���֣������Ӱ����ʵ����ȣ��ҵ���ʦָ����������ʵ������ˣ����ǽ�֪ʶӦ����ʵ���ĽŲ��Dz���ͣЪ�ġ�

�ڶ�ƪ��EDA������ʵ�鱨��

����ˮ��ˮ��ѧԺ

EDA����(������)����

�� �ƣ� EDA�ۺ�ʵ�����

�� Ŀ�� ������

Ժ ϵ�� ��Ϣ����

�� ����

ѧ �ţ�

ѧ��������

ָ����ʦ��

20##�� 1�� 7��-----18��

һ���γ����(�ۺ�ʵ��)����

���һ���ۺ��Եļ�ʱϵͳ��Ҫ����ʵ��ʱ���֡���������ۺϼ�ʱ���ܣ�ͬʱ����ʱ���ͨ��6���߶��������ʾ���ܹ���ʱ�ͷֽ�������,����һ����λ,���¼�����

1�� �����·����ֱ��������ɷ�Ƶ����������������Ϊ�����·�ļ���ʱ���źţ���������60˲�䣬��λ���Ʒֵ�·��1���������·�����㲢���¼��롣

ע������ʵ�����õļ���ʱ������ʵ������1KHZ�źž���Ƶ�������ġ�

2�� �Ʒֵ�·����ʱ��·�������˼��������·���ơ���ʱ��·��24���Ƶģ�����24������λ��

3�� ʱ�����õ�·�������ʱ������е��������ܹ�������λ��

4�� ��ʾ���Ƶ�·����ƣ��������ʾ��Ҫʹ�õ���6���߶���ʾ����ܡ�

ע������ʵ����EDA6000������ʱ�����õ����ڲ�����4-16�������İ˶�����ܡ�

���� ����Ŀ��

1�� ����ʱʮ���ơ���ʮ���ƺͶ�ʮ�Ľ��Ƽ���������Ʒ�����

2�� ���ն�λ��������������Ʒ�����

3�� ���ն�λ������ɨ����ʾ����ܵ����������롣

����������Ʒ���

1�� ���������

1��1 ��ʱ����ʾ���ܣ���ʱģ��ʵ��Ϊ��һ����1Hzʱ��������м��������������60����ּ�������λ���ּ�������60��ʱ��������λ��ʱ������Ϊ24���ơ�6���߶���ʾ����ֱܷ���ʾʱ���֡����ʮλ��λ��

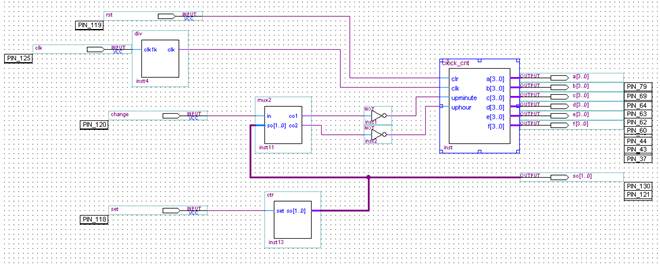

1��2 ʱ�����õ�·������ϵͳ�е�ʱ�������·������ͨ�������ⲿ����“set”��“chang”��“rst”����ɡ�

“rst“Ϊ��λ��������֮��ʱ�����㣬���¿�ʼ������

“set”Ϊʱ�����ÿ��Ƽ�������һ�¶Էֽ������ã���min�������������ʾ�������ڶ��¶�ʱ�������ã�����hour�������������ʾ�����������£����¿�ʼ������

“chang”��Ϊ��“set”�����¶�ʱ���������ʱ����ʱ��ֽ��м�1������ֱ����������ʱ�䡣

2�� ��λ���ƾ��巽����

2.1ʱ���������ģ��

�������ӵ�ʵ�ֿɷ�Ϊ���¼���ģ�飺

(1) Ƶ�ʲ���ģ�飺��EDA6000ʵ�������1kHz�ļ���Ƶ�� ��ͨ����Ƶ�õ�1Hz�źţ�

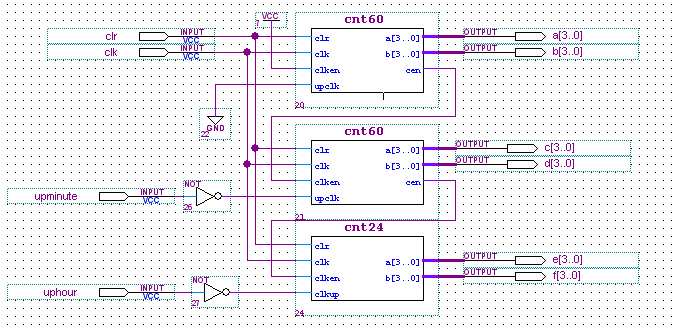

(2) �����ģ�飺���������Ƶ��Ϊ1Hz��ʱ������60��Ϊѭ����������������λ�ź�Ӱ��ּ�����

�� (3) �ּ���ģ�飺�ּ����������λ�ź�Ϊ�ߵ�ƽʱ������һ�Σ�ͬ����60��Ϊһ��ѭ��������ͬʱ�����ֽ�λ�ź�Ӱ��ʱ������

����(4) ʱ����ģ�飺ʱ�������ڷֽ�λ�ź�Ϊ�ߵ�ƽʱ������һ�Σ���24��Ϊһ��ѭ��������

����(5) ʱ����ʾģ�飺�����ͨ����̬��ʾ��ͬʱ����һ��Ƶ�ʵ�ɨ����ʾʱ���֣��롣

����(6) ʱ������ģ�飺���õ���ʹ�ܶˣ����Ե�ʱ���֡�������������ʹ�ܶ�changΪ�ߵ�ƽʱ������ʹʱ�ͷ�ѭ��������

2.2 ��·��ɣ�

һ�������������ӵ�·��Ҫ��������ʾ����“ʱ”��“��”��“��”��������ɡ��ɵ�·ϵͳ�����źŷ�����(��Ƶ��)��“ʱ”��“��”��“��”����������������ʾ����·��ɡ�

��Ƶ����·��ͨ���������ӵľ����������Ƶ�ʽϸߣ�Ϊ�˵õ�1Hz�����ź����룬��Ҫ������������źŽ��з�Ƶ��ͨ��ʵ�ַ�Ƶ���ĵ�·�Ǽ�������·����������ʱ�������Ӧ�����䣬�Ӷ��õ���Ҫ�ĵķ�Ƶ��Ƶ�ʡ�

ʱ�������Ԫ��ʱ�������Ԫ��ʱ�������ּ�����������ȼ������֡�ʱ������Ԫһ��Ϊ12���Ƽ�������24���Ƽ�������

������������ʾ��Ԫ��������ʵ���˶�ʱ����ۼ���8421BCD����ʽ�����Ϊ�˽������������8421BCD����ʾ���������������м���ģʽ�ɹ�ѡ��ѡ���Դ���4-16����������ʾ���������оͿ���ֱ������λbcd�����Ӧ�˿ھ��С�

����Ƶ��������ԭ���ṹ��ͼ���£�

�ģ�ʵ�����

����ģ���õ�ԭ��ͼ���뷨������ͼ����:

������ģ�����

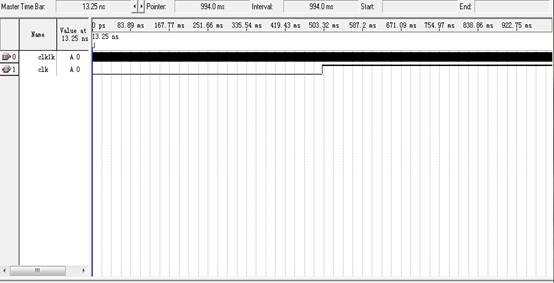

module div(clk1k,clk); //��Ƶģ�飬��1 kHZ���źŲ���1HZ�ļ������룩ʱ��

input clk1k;

output clk;

reg clk;

integer n;

always@(posedge clk1k)

if(n��500) //ÿ����500������ʱ��ʱ��clkȡ��һ�Σ�������1HZ���ź�

n��=n+1;

else

begin

clk��=~clk;

n��=0;

end

Endmodule

module ctr(set,so); //ʱ��������Ч�ź�“set”�IJ���ģ��

input set;

output [1:0]so;

reg [1:0]so;

always@(posedge set) //set������ֵ��1��2��setΪ1ʱ��“��”�������ã�Ϊ2ʱ��“ʱ”�������ã������ش���

if(so��2)

so��=so+1;

else

so��=0;

Endmodule

module mux2(in,so,co1,co2); //��ѡһģ�飬�������ֶ�“��”��“ʱ”������

input in;

input [1:0] so;

output co1,co2;

reg co1,co2;

always@(so)

case(so)

1:co1��=in; //��set���s0Ϊ1ʱ����in(chang����)��co1���Էֽ������ã�

2:co2��=in; //��set���s0Ϊ2ʱ����in��chang���룩��co2����ʱ�������ã�

default:begin

co1��=0;

co2��=0;

end

endcase

endmodule

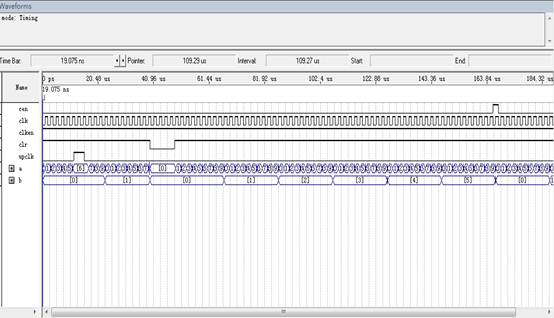

module cnt60(clr,clk,clken,upclk,a,b,cen); //�ֺ���ļ���ģ�飬60����

input clk,clr,clken,upclk; //clrΪ�����źţ��͵�ƽ��Ч��upclkΪ“��”��ʱ�������ź�

//clkenΪʹ���ź�

output [3:0]a,b; //aΪ��λ��bΪʮλ

output cen;

reg [3:0]a,b;

reg CenInside;

wire ClkInside,cen;

assign ClkInside = (clken & clk)|upclk; //��ʹ���ź���clkͬʱ��Ч����ʱ��������//����Чʱ��������������ʼ����

assign cen = CenInside & clken; //cenΪ��һ��������ʱ���źţ���CenInside����������//��������clken���ϼ�����������ͬʱ��Чʱ����

always @(posedge ClkInside or negedge clr) //�������飬ͬʱ����ʱ������ʱ��ʱ��Ӳ���

begin

if(!clr) begin a=0; b=0; end

else if(a==9)

begin

a=0;

if(b==5) b=0;

else b=b+1;

end

else

begin

a=a+1;

b=b;

end

end

always @(negedge clk or negedge clr) //�˳��������������������ź�CenInside

begin

if(!clr) CenInside=0;

else

if((a==9)&(b==5)) CenInside=1;

else CenInside=0;

end

endmodule

module cnt24(clr,clk,clken,clkup,a,b); //“ʱ”�ļ�ʱΪ24���ƣ�����24Сʱ��λΪ��

input clk,clr,clken,clkup;

output [3:0]a,b; //aΪ“ʱ”��ʾ�ĸ�λ��bΪ“ʱ”��ʾ��ʮλ

reg [3:0]a,b;

wire clkinside;

assign clkinside = (clken & clk) | clkup;

always @(posedge clkinside or negedge clr) //����24���Ƽ������

begin

if(!clr) begin a=0; b=0; end

else

begin

if(b��2)

if(a==9)

begin

a=0;b=b+1;

end

else

begin

a=a+1;

b=b;

end

else

if(a==3) begin a=0;b=0;end

else begin a=a+1; b=b;end

end

end

Endmodule

�塢Quartus���Է�����EDA6000����������

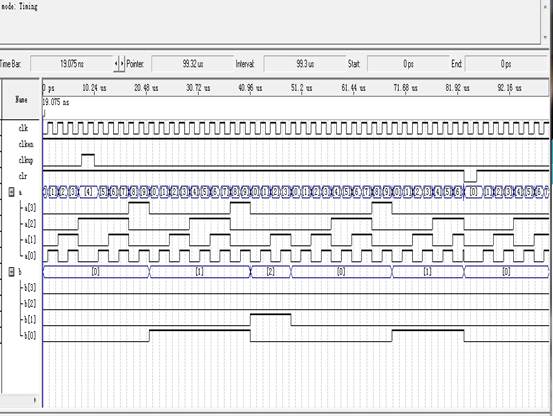

1��ʱ�����

1.1��ʱ�����õķ���

ԭ����“set”�ߵ�ƽ��Ч�����һ��������Чʱ��S0Ϊ1��ʼ��“��”�������ã�“chang”��ִ�з����õļ�1��������������Ч��ͬ����“set”�ĵڶ�����Ч��������֮��S0Ϊ2����ʼ��“ʱ”�������ã�“set”�ĵ��������嵽��֮��S0���㣬�˳�ʱ�����ÿ�ʼ����������

����ͼ�У�“set”��һ������֮����һ��“chang”��Ч����“��”��1���ĸ�“chang”����֮��“��”��������Ϊ4�֡������÷�����ȷ��“set”�ڶ�������֮����һ��“chang”��Ч����“ʱ”��1���ĸ�“chang”����֮��“��”��������Ϊ4ʱ��ʱ���÷�����ȷ��

1.2�Լ���ģ��ķ���

ԭ������һ����Ч��CLK1HZ���壨�ߵ�ƽ��Ч����“��”��1�������60��“��”��1��“��”����60��“ʱ”��1��

����ͼ�У�ʱ�������������Ϊ70S��������ǰ���õ���4ʱ4�֣�ʱ����ʾΪ4ʱ5��09�룬��ʾ��ȷ����ʱ�������ȷ

1.3�ܳ���RTLͼ

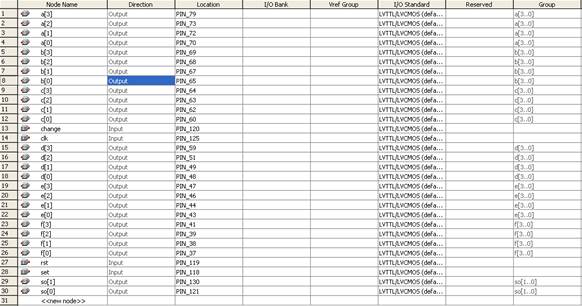

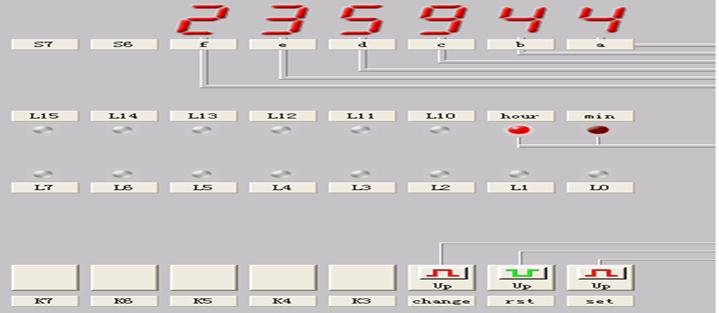

2.��EDA6000����������

2.1�ܽŷ���

2.2��.sof�ļ����ص�������

ע������ʵ���õ�Alter��˾��FPGAоƬ���ͺ�ΪACEX1P1K30TC144--3

2.3װ��ģʽ

2.4���������俪ʼ����

��“��”��������ʱ��“min”���������������һ��“chang”�ּ�1������60���Զ���λΪ�㣬Ȼ�����¼�����������ȷ��

��“ʱ”��������ʱ��“hour”���������������һ��“chang”�ּ�1������24���Զ���λΪ�㣬Ȼ�����¼�����������ȷ��

��������

ͨ����ογ���ƣ��Ҿ���ѧ���˺ܶණ������Quartus���˽�����ˣ���ΪEDA��ѧϰ�����ѧ�ڣ������ſ��е�ѹ�������Զ������IJ����ܲ���Ϥ���ܶණ������֪����ô������ογ���ƣ��Ҿ����Լ��Ľ����ô�֪����һ���IJ��裬Ҳѧ���˱�д�����ԣ��ۺϣ����η��棬��������ģ�飬��ͼ�ȵȡ��������ۿ����Լ����鱾��ѧ����֪ʶ�����õ��˾���������ϣ����ҽ����ͦ������EDA���Ҳ��һ��ʱ���ˣ��ö�֪ʶ���е������ˣ��õ��˵������ٿ��������Ļ��������д����ȥ��������Ҳ������֪ʶ��

�Ҿ���EDA���ſγ̺�ʵ�ã��Ժ�����ʱ���ô�Ҳ��ͦ��ģ��������Ժ��ʱ�����һ�ú�������������������Ҳ֪���˶���ʦ�����ǵ��ϸ�Ҫ���ˣ�������Ϊ����ʦ���ϸ�Ҫ��ͬѧ�Dzſ���������ô˳����������ʦ����ͽ��������ܸ�л����ʦ�������ĵ����ӵ���ƣ����ܲ���̫ȫ����ʦҪ��Ĺ���û�мӽ�ȥ�꣬�кܶ�����ĵط���Ҫ�Ľ������ܹ��ܲ�ȫ������ȷ��Ҳ�����˺ܳ�ʱ���Ŭ���������Լ��ij�����ʵ�������ʾ�����Ҿ��ú��гɾС���֪���һ��кܶ�ĵط���ҪŬ������Ҳ�����Ŭ����

�ο�������(��ţ�����Ӵ�)

��1�� ���ɣ���EDAʵ�ý̡̳�����ѧ�����磬20##��

-

���ֵ���ʱ��ʵ�鱨��

����ƿ�ѧԺ�������γ����˵������Ŀ�����������רҵ���������ѧ�뼼���༶�����繤��1��***ѧ�ţ�****������ڣ�20XX��

-

������ʵ�鱨��

������ʵ�鱨��������ƣ������ӵ������������Ա���������༶��������ϢI��112��ʵ��ʱ�䣺ʵ��ص㣺ָ����ʦ��һ��ʵ��Ŀ�ģ�1��ѧ��

-

���ֵ�����ʵ�鱨��

�б���ѧ20xx�챾�ƿγ����˵����Ŀ¼һ���Ŀ������1���������11������Ʒ������12��Ԫ��·���23�ܵ�·ͼ64������7����

-

���ֵ�·����ʱ�ӿγ�ʵ�鱨��

����ʱ�����ʵ�鱨��һ���Ҫ�����һ��24Сʱ�Ƶ�����ʱ��Ҫ���ʱ��ʾ���ȵ�����Уʱ���ܲ�����С��ģ���ɵ�·��Ʒ����������ӹ��ܶ���

-

���ֵ�����ʵ�鱨��

����ʦ��ѧԺ��������ӹ���ѧԺ�γ���Ʊ�����Ŀ�༶����ѧ��ָ����ʦ�ɼ������������1Ŀ¼��һ�¸���3�ڶ������ֵ����ӵĵ�·ԭ��4�ڡ�

-

EDA������ʵ�鱨��

����ˮ��ˮ��ѧԺEDA�γ����(������)�������ƣ�EDA�ۺ�ʵ�������Ŀ��������Ժϵ����Ϣ���̰༶��ѧ�ţ�ѧ��������ָ����ʦ��20��

-

eda������ʵ�鱨��

ʵ�������������һʵ��Ŀ��1��һ��ѧϰ�����ӵ�EDA������Ŀ��Ƹ�������VHDL�������2ѧϰ��̬����ܵ�VHDL���3���������ơ�

-

EDA������ʵ�鱨��

�繤����ʵϰʵ�鱨������ʦԪ���༶����09K2ѧ��0919xx030212һʵ��Ŀ��1���ն�λ��������������Ʒ���2����ʮ������ʮ��