EDA课程设计报告-彩灯控制器

《EDA技术》课程设计报告

学 院: 信息科学技术学院

专 业: 通信工程

班 级: 通信(2)班

姓 名: 肖 强

学 号: 20081604B064

20##年06月26日

目 录

摘 要. 1

一.设计目的. 1

二.设计题目描述及要求. 1

三.设计原理. 2

3.1 方案论证. 2

3.2 模块设计. 2

3.2.1集成分频器模块. 2

3.2.2 32进制计数器模块. 2

3.2.3 彩灯控制模块. 2

3.2.4 4选1选择器模块. 2

3.2.5 4进制计数器模块. 2

3.3 系统结构. 2

四.总结. 2

参考文献. 2

附录一.编译. 2

附录二.时序仿真. 2

附录三.程序. 9

摘 要

循环彩灯的电路很多,循环方式更是五花八门,而且有专门的可编程彩灯集成电路。绝大多数的彩灯控制电路都是用数字电路来实现的,例如,用中规模集成电路实现的彩灯控制电路主要用计数器,译码器,分配器和移位寄存器等集成。本次设计的循环彩灯控制器就是用计数器和译码器来实现,本彩灯控制器能实现四种不同的花型,在呈现出不同花型的同时发出四种不同的声音,数码管用以标记当前呈现的是哪种花型。

[关键词]:计数器,二极管, 数码管,分频器

一.设计目的

学习EDA开发软件和MAX+plus Ⅱ的使用方法,熟悉可编程逻辑器件的使用,通过制作来了解彩灯控制系统。

本次课程设计的主要目的是通过电子设计自动化的设计,掌握FPGA应用系统的开发过程,进一步理解FPGA应用系统的工作原理。本课程设计设计了一个多路彩灯控制器,四种彩灯能循环变化,有清零开关,可以变化彩灯闪动频率即可以选择不同的节拍。整个系统有三个输入信号,分别为音频输入脉冲信号clk2,复位清零信号CLR,彩灯输入控制脉冲clk1。最后按照FPGA的开发流程和VHDL语言建模、仿真、综合、下载、适配,用EDA6000实验箱上的FPGA系统实现了相应的功能。

通过这次课程设计更清楚的理解了VHDL程序的描述语言,能进行简单程序的编写和仿真。

二.设计题目描述和要求

1)设计一个彩灯控制器,使彩灯(LED管)能连续发出四种以上不同的显示形式;

2)随着彩灯显示图案的变化,发出不同的音响声。

3)扩充其它功能。

三.设计原理

3.1 方案论证

彩灯设计总体采用分模块的方法来完成,包括分频器、32进制计数器、4进制计数器、4选1选择器、彩灯控制器五大部分。其中彩灯控制器是用来控制8个LED,使其呈现出不同的花型,而彩灯控制器的输出则是由32进制计数器来控制。扬声器输出不同的响声是通过加不同频率的麻涌信号来实现,不同频率的信号送至扬声器会发出不同的声音。所以用了一个集成分频器来将输入的频率分成几种不同的频率。不同频率的选择性输出则是由一个4选一的选择器来实现。

在现实不同花形的同时,伴随有不同的声音发出,而且通过数码管现实1、2、3、4,标志出所显示的是哪一种花型。数码管的显示是由彩灯控制模块来控制。

3.2 模块设计

3.2.1集成分频器模块

设计要求显示不同的彩灯的时候要伴随不同的音乐,所以设计分频器来用不同的频率控制不同的音乐输出。

模块说明:

Rst:输入信号 复位信号 用来复位集成分频器的输出使输出为“0”,及没有音乐输出,输入此信号后,彩灯从第一种花型开始顺序循环。

Clk:输入信号 此信号即为分频输入的频率信号。

Clk_4、clk_6、clk_8、clk_10:输出信号 即为分频模块对输入信号clk的分频,分别为1/4分频输出、1/6分频输出、1/8分频输出、1/10分频输出。

图3-2-1 集成分频器

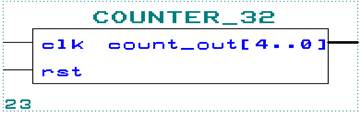

3.2.2 32进制计数器模块

32进制模块用来控制彩灯输出模块,即确定彩灯控制器的不同的输出。

Rst:输入信号 复位信号 用来复位32进制使其输出为“00000”。

Clk:输入信号 用来给模块提供工作频率。

Count_out[4..0]:输出信号 即为32进制计数器的输出。

图3-2-2 32进制计数器

3.2.3 彩灯控制模块

彩灯控制模块用来直接控制彩灯的输出,使彩灯表现出不同的花样。

Rst:输入信号 使彩灯控制模块的输出为“00000000”,即让彩灯无输出。

Input[4..0]:输入信号 不同的输入使彩灯控制模块有不同的输出即彩灯显示出不同的花样。

Output[7..0]:输出信号 直接与彩灯相连来控制彩灯。

Sm[3..0]:输出信号 用来控制数码管使其显示1、2、3、4,以此来标志出不同的花型。

图3-2-3 彩灯控制模块

3.2.4 4选1选择器模块

Rst:输入信号 复位信号 使选择器的输出为“0”。

In1、in2、in3、in4:输入信号 接分频器的输出。

Inp[1..0]:输入信号 接4进制计数器的输出用来控制选择器的选择不同的输入选择不同的输出。

Output:输出信号 直接接扬声器即输出的是不同的频率来控制扬声器播放音乐。

图3-2-4 4选1选择器

3.2.5 4进制计数器模块

4进制计数器作为选择器的输入来控制选择器选择不同的频率作为输出控制扬声器工作。

Clk:输入信号 来为计数器提供工作频率。

Rst:输入信号 复位信号 使计数器的输出为“00”。

图3-2-5 4进制计数器

3.3 系统结构

整个系统就是各个分模块组成来实现最后的彩灯控制功能,系统又两个时钟来控制一个是控制32进制计数器即控制彩灯控制模块来实现彩灯的不同输出,另一个时钟为分频器的输入来进行分频处理,最后用来控制扬声器发出不同的音乐,具体分频处理的时钟的频率比实现彩灯控制的时钟频率要高。

图 3-3-1 系统功能模块

四.总结

这次的EDA课程设计有一周的时间,在这一周的时间里我们充分合理的安排了自己的时间来使本次的课程设计能够顺利的完成,当然我们在本次的设计中并不是一帆风顺的,我们遇到了一些的问题,例如我们开始时用的文本的方式用一个总的程序来完成,可以在设计的过程中我们发现程序编到后面变量越到很容易搞混淆同时各个进程间的联系也越来越模糊以至于后面我们自己都不知道程序的整体框图是什么,导致后面不能够继续下去,后面我们再一次对我们这次的设计题目进行了分析和整理,最后我和我的同伴决定采用分模块的方式来完成本次的课题设计,当然最重要的是分析各个模块间的关系。最后我们采用上面分析的结构框图。最后我们的设计很成功,仿真和硬件测试都是正确的,实现了我们的设计要求和目的。

在这次设计中我们收获了很多,首先最直接的收获就是我们巩固了这门课程所学过的知识,把它运用到了实践当中,并且学到了很多在书本撒和那个所没有学到的知识,通过查阅相关资料进一步加深了对EDA的了。总的来说,通过这次课程设计不仅锻炼了我们的动手和动脑能力,也使我懂得了理论与实际相结合的重要性,只有理论知识是远远不够的,要把所学的理论知识与实践相结合起来,才能提高自己的实际动手能力和独立思考的能力。在我们的共同努力和指导老师的指引下我们圆满的完成了彩灯控制器的设计,实现了设计目的。

参考文献:

[1] 金西,《VHDL与复杂数字系统设计》,西安,西安电子科技大学出版社,2003

[2] 汉泽西,《EDA技术及其应用》,北京,北京航空航天大学出版社,2004

[3] 李广军 《可编程ASIC设计及应用》,电子科技大学出版社,2005

[4] 谢自美,《电子线路设计·实验·测试》,华中理工大学出版社,2004

[5] 谭会生,《EDA技术》,西安电子电子科技大学出版社,20##年

附录一. 编译

附录二. 时序仿真

附录三. 程序

-------------------------分频器模块-------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY fenpinqi IS

PORT

(

clk,rst : IN std_logic;

clk_10,clk_4,clk_6,clk_8 : OUT std_logic

);

END fenpinqi;

ARCHITECTURE cd OF fenpinqi IS

begin

p1:process(clk,rst)

variable a:integer range 0 to 20;

begin

if rst='1' then

clk_4<='0'; ----- 复位信号控制部分

else

if clk'event and clk='1'then

if a>=3 then

a:=0;

clk_4<='1';

else

a:=a+1;

clk_4<='0';

end if;

end if;

end if;

end process p1;

p2:process(clk,rst)

variable b:integer range 0 to 20;

begin

if rst='1' then

clk_6<='0'; ----- 复位信号控制部分

else

if clk'event and clk='1'then

if b>=5 then

b:=0;

clk_6<='1';

else

b:=b+1;

clk_6<='0';

end if;

end if;

end if;

end process p2;

p3:process(clk,rst)

variable c:integer range 0 to 20;

begin

if rst='1' then

clk_8<='0'; ----- 复位信号控制部分

else

if clk'event and clk='1'then

if c>=7 then

c:=0;

clk_8<='1';

else

c:=c+1;

clk_8<='0';

end if;

end if;

end if;

end process p3;

p4:process(clk,rst)

variable d:integer range 0 to 20;

begin

if rst='1' then

clk_10<='0'; ----- 复位信号控制部分

else

if clk'event and clk='1'then

if d>=9 then

d:=0;

clk_10<='1';

else

d:=d+1;

clk_10<='0';

end if;

end if;

end if;

end process p4;

end cd;

------------------4选1选择器--------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY xzq4_1 IS

PORT

(

rst:in std_logic;

inp:in integer range 0 to 3;

in1,in2,in3,in4 : In std_logic;

output : OUT std_logic

);

END xzq4_1;

ARCHITECTURE a OF xzq4_1 IS

BEGIN

PROCESS (rst,inp)

BEGIN

if(rst='1') then output<='0';

else

case inp is

when 0=>output<=in1;

when 1=>output<=in2;

when 2=>output<=in3;

when 3=>output<=in4;

when others=>null;

end case;

end if;

END PROCESS;

END a;

-----------------彩灯控制模块----------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY caideng IS

PORT

(

input : IN INTEGER RANGE 0 TO 31;

rst:in std_logic;

output : OUT std_logic_vector(7 downto 0);

sm :out std_logic_vector(6 downto 0)

);

END caideng;

ARCHITECTURE a OF caideng IS

BEGIN

PROCESS (input)

BEGIN

if rst='1' then output<="00000000";sm<="0000000";

else

case input is

when 0=>output<="10000000";sm<="0000110";

when 1=>output<="01000000";sm<="0000110";

when 2=>output<="00100000";sm<="0000110";

when 3=>output<="00010000";sm<="0000110";

when 4=>output<="00001000";sm<="0000110";

when 5=>output<="00000100";sm<="0000110";

when 6=>output<="00000010";sm<="0000110";

when 7=>output<="00000001";sm<="0000110";

when 8=>output<="00010000";sm<="0011011";

when 9=>output<="00110000";sm<="0011011";

when 10=>output<="00111000";sm<="0011011";

when 11=>output<="01111000";sm<="0011011";

when 12=>output<="01111100";sm<="0011011";

when 13=>output<="01111110";sm<="0011011";

when 14=>output<="11111110";sm<="0011011";

when 15=>output<="11111111";sm<="0011011";

when 16=>output<="10000001";sm<="1001111";

when 17=>output<="11000001";sm<="1001111";

when 18=>output<="11000011";sm<="1001111";

when 19=>output<="11100011";sm<="0011011";

when 20=>output<="11100111";sm<="1001111";

when 21=>output<="11110111";sm<="1001111";

when 22=>output<="11111111";sm<="1001111";

when 23=>output<="00001000";sm<="1001111";

when 24=>output<="00000001";sm<="0100110";

when 25=>output<="00000010";sm<="0100110";

when 26=>output<="00000100";sm<="0100110";

when 27=>output<="00001000";sm<="0100110";

when 28=>output<="00010000";sm<="0100110";

when 29=>output<="00100000";sm<="0100110";

when 30=>output<="01000000";sm<="0100110";

when 31=>output<="10000000";sm<="0100110";

when others=>null;

end case;

end if;

end process;

end a;

-----------------32进制计数器模块-----------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY counter_32 IS

PORT

(

clk,rst : IN std_logic;

count_out : OUT integer range 0 to 31 );

END counter_32;

ARCHITECTURE a OF counter_32 IS

BEGIN

PROCESS (rst,clk)

variable temp:integer range 0 to 32;

BEGIN

IF rst='1' THEN

temp:=0;

ELSIF (clk'event and clk='1') THEN

temp:=temp+1;

if(temp=32) then

temp:=0;

end if;

END IF;

count_out<=temp;

END PROCESS;

END a;

---------------4进制计数器模块-------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY counter_4 IS

PORT

(

clk,rst : IN std_logic;

count_out : OUT integer range 0 to 3 );

END counter_4;

ARCHITECTURE a OF counter_4 IS

BEGIN

PROCESS (rst,clk)

variable temp:integer range 0 to 32;

BEGIN

IF rst='1' THEN

temp:=0;

ELSIF (clk'event and clk='1') THEN

temp:=temp+1;

if(temp=4) then

temp:=0;

end if;

END IF;

count_out<=temp;

END PROCESS;

END a;

-

可编程控制器应用课程设计报告

青岛农业大学可编程控制器应用课程设计报告20xx20xx学年第1学期题目塔吊的PLC控制系统设计姓名学号专业班级指导老师20xx年…

-

可编程控制器技术课程设计报告

《可编程控制器技术》课程设计题目:交通信号灯控制设计学院:信息工程与自动化系:通信工程专业:通信工程年级:061班姓名:**学号:…

-

可编程控制器课程设计报告

可编程控制器课程设计报告题目:基于PLC的自动洗衣机控制系统设计年级:2009级班级:自动化1班姓名:王**学号:**指导教师:张…

-

可编程控制器课程设计

可编程控制器课程设计中央空调的设计一前言我国是一个人均能源相对贫乏的国家人均能源占有量不足世界水平的一半随着我国经济的快速发展我国…

-

电气控制及可编程控制器课程设计报告

扬州大学水利与能源动力工程学院本科生课程设计课程:电气控制及可编程控制器课程设计专业:建筑电气与智能化班级:建电1102班学号:姓…

-

循环彩灯课程设计报告

电子系统课程设计报告学号17姓名虞丽惠班级应电091班指导老师吴夏来时间20xx53020xx610课程设计报告目录一引言2二设计…

-

循环彩灯电路设计报告

数字电子技术基础课程设计报告设计题目彩灯循环控制器的设计专业班级姓名学号指导教师设计日期20xx年6月课程设计评审意见1设计阶段3…

-

循环彩灯课程设计

数字电路课程设计学年设计学年论文任务书数字电路设计说明书学院名称计算机与信息工程学院班级名称网络工程4班学生姓名学号题目循环彩灯控…

-

LED循环彩灯课程设计

学院模拟电子技术课程设计题目LED循环彩灯学生姓名专业班级电科3班学号20xx31000院系电气工程学院指导教师完成时间20xx年…

-

16路循环彩灯设计报告

循环彩灯控制电路的设计一课程设计的目的1巩固和加强数字电子技术课程的理论知识2掌握电子电路的一般设计方法了解电子产品研制开发过程3…

-

中断方式控制彩灯闪烁实验报告

中断方式控制彩灯闪亮报告实验题目中断方式控制彩灯闪亮专业计算机科学与技术学生姓名班级学号分组序号指导教师20xx年5月13日中断方…