数电秒表设计报告

目录

一、技术要求…………………………………………… 2

二、总体电路设计……………………………………… 3

三、模块电路设计……………………………………… 3

1.多谐震荡器电路……………………………… 4

2.计数器电路 ………………………………… 4

3.译码驱动显示电路………………………… 5

四、总电路原理图……………………………………… 6

五、元件清单…………………………………………… 7

六、电路板制作………………………………………… 7

1.电路板布局…………………………………… 7

2.电路板的焊接………………………………… 8

3.电路板的调试和检查………………………… 8

七、设计总结…………………………………………… 8

1.设计中遇到的问题及解决方法……………… 8

2.设计体会……………………………………… 9

八、参考资料…………………………………………… 9

一、技术要求

要求设计一个数字表,用于短时间测量,适用于计时使用。

(1)计时范围:0~59秒

(2)显示分辨率为1s。

(3)用按钮开关控制工作状态,即:暂停、清零。

(4)本身带有,工作时指示灯亮。

二、电路总体设计

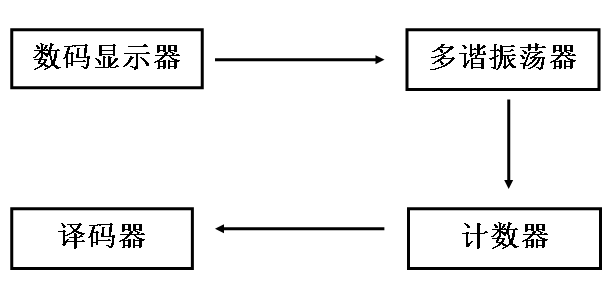

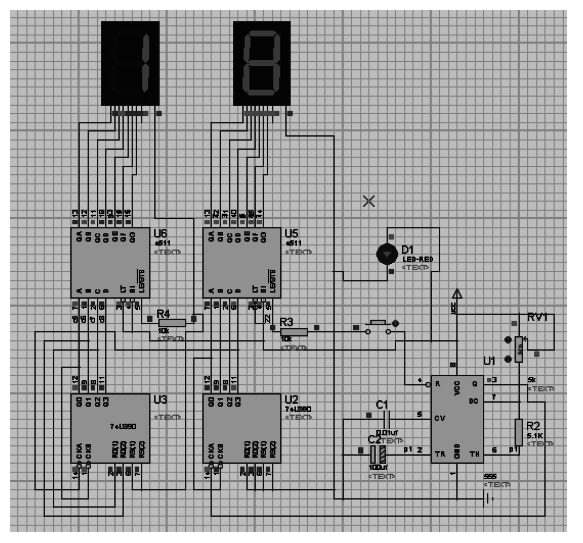

实验要求设计一个用于短时间测量的电子表,根据学过的相关知识可以知道和题目的要求,电路应该分为分为四个部分,分别是多谐振荡器、计数器、译码器和数码显示器。

电子秒表电路的基本组成(方框图)

1 两个方案:方案一 555定时器做的,方案二 石英晶体构成石英晶做的。

方案一、

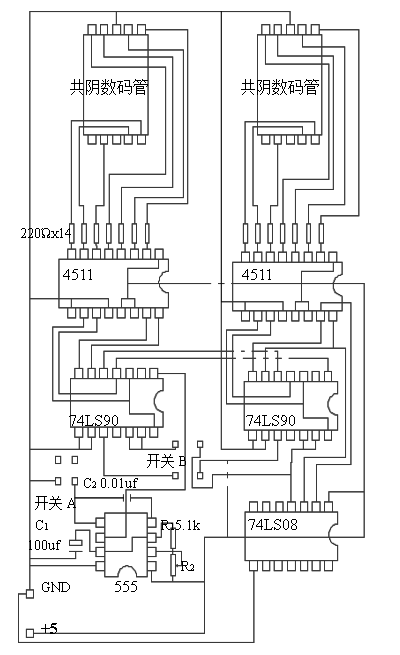

用一个555定时器做出多谐振荡电路为计数电路提供计数脉冲,通过调节外围电阻R1、R2和电容C的值使振荡电路产生1Hz的计数脉冲(即周期为1秒的信号)。用74LS90计数器做成60进制的秒计数电路,并用7408配合反馈清零,4511三线七线译码器通过开关态控制数码管暂停。

方案二、

用石英晶体构成石英晶振脉冲发生器。计数电路是74LS90串接构成的60进制计数器可以计数到60秒(1分钟)这样控制起来比较方便、控制电路同方案一。

最终方案:

方案一。由于对方案二的石英晶振电路原来不是很熟悉,并且方案二的计数显示不符合人的一般思维方式,因此选用方案一作为最终方案。

2 元器件选择

4511 74ls08 74ls90 555

3 参数计算

充电时间 T1

T1=0.7(R1+R2)C=0.7*1210*0.001=0.847s

放电时间T2

T2==0.7 R2 C=0.7*210*0.001=0.147s

电路震荡周期T

T=T1+T2=0.7(R1+2R2)C

电路震荡频率

f=1/T=1.43/(R1+2R2)C

三、模块电路设计

1. 多谐震荡器电路

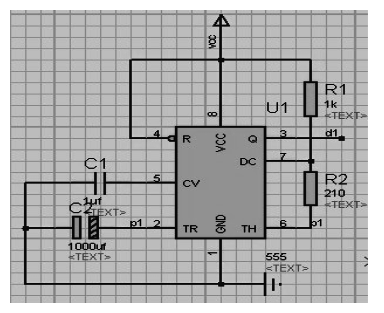

为由555构成的多谐振荡器电路,根据实验的要求需要获得1HZ的时间信号,则令f=1HZ,由上面的公式推算出:R1=5.1kΩ, R2为5KΩ微调电阻约为4592欧,C1=100uF。就能得到1HZ的秒脉冲信号‘实验时其3管脚输出脉冲为1Hz。 下图为555构成多谐振荡器电路

555构成多谐振荡器电路

2. 计数器电路

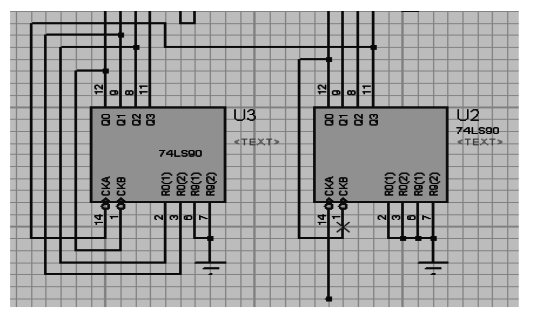

秒信号发生器是数字电子钟的核心部分,它的精度和稳定度决定了时信号发生器和分信号发生器的精度。“秒”计数器为60进制计数器。实现此100模数的计数器是由两片中规模集成计数器74LS90构成的。首先分别将两片74LS90设置成10进制加法计数器。即将两片的74LS90的置数端R0和R9都接地,将INA端接到QA端,以QD为进位输出端,则构成了10进制加法计数器。再将其中一片74LS90计数器的进位输出端QD接到另一片74LS90的进位输入端INA端。如此,两片计数器最大的即可实现100进制的计数器。接下来,利用74LS90的反馈置数的方法实现60进制。74LS90属于异步置数,所以计数器输出“2QD2QC2QB2QA、1QD1QC1QB1QA=0110、0000”时,通过置数脉冲使计数器清零,也就是此时QB,QC发出置数脉冲送至清零端R0,则R0使计数器清零[4- 6]。“秒”计数器电路图如图所示

计数器电路图

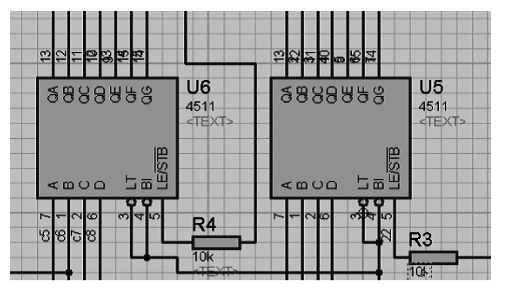

3. 译码器电路

计数器实现了对时间的累计以8421BCD码形式输出,为了将计数器输出的8421BCD码显示出来,需用显示译码电路将计数器的输出数码转换为数码显示器件所需要的输出逻辑和一定的电流,一般这种译码器通常称为7段译码显示驱动器。为了减小流经数码管的电流,以便保护数码管,所以在数码管与地线之间联一个200欧姆电阻。

四、总电路原理图

五、元件清单

六 电路板的制作

1. 电路板的布局

2. 电路板的焊接

电路板的焊接是一项技术活,焊接的时候要很小心加很细心加很有耐心,应尽量避免虚焊和焊接短路的出现,需要跳线的地方,应选择小一些的电线当跳线。

焊接时一定要注意安全,不要让焊烙铁烫到手。

如果真的不幸被烫了,要保持冷静,不要慌,尽快用冷水浸泡伤口三到五分钟,之后可抑制水泡的产生。

焊接好之后,可以用专门的剪刀剪掉那些长出来的管脚。

3. 电路板的调试和检查

电路板焊接好之后,就可以安装上元件,进行调试检查了。这是课程设计的最后一步,需要耐心。调试时电源一定要量调好电压再接入电路板,不然会烧坏电路板。

调试时观察数码管的显示是否正确,振荡电路是否正常工作。

如果工作不正常,就要用万用表检查线路是否短路和虚焊,如果有,就要重新焊过。有些地方铜膜线断开了,要特别注意检查,因为这些地方,一般肉眼很难分辨。

调试和检查完成了,数字秒表正常工作了,这次课程设计才算圆满完成。

七 设计总结

1 实验中遇到的问题及解决方法

实验中遇到了很多意想不到的问题,从一开始的设计原理图到最后的电路板焊接,一直都是在发现问题和解决问题中度过。还好自己一路坚持了下来,把问题一一解决。

设计的时候,画原理图经常会连错线,元件的位置摆放得不好,经常出现线交叉的情况,这样就要从整个原理图出发去放置元件,以及连线。刚开始不知道数码管的管脚排列的顺序,问了好几个人,再加上自己用万能表测了才搞清楚。

还有其它的问题,比如,仿真时候,元件的值选多少;焊板时烫到了,怎么办;调试时,数码管没反应,又该怎么办……

其实这些都不是问题,只要我们有耐心,够细心,都可以把它们解决。

2 设计体会

以前看别人的一个电子秒表卖十几块钱,心里面有点愤愤不平,现在,自己做过一个电子秒表,才发现,其中的不容易,还有艰辛。其实做其他的事情也是一样,都会经过很多的困难,才能成功。突然想起一句话“不经历风雨,怎么见彩虹”。

通过这次设计让我真正体会到了,有付出,才会有收获。

八、设计参考资料

[1]. 孙丽霞.数字电子技术. 北京:高等教育出版社, 2010.

[2] .王港元.电子电工实践指导.江西:江西科学技术出版社.2009.

第二篇:数电自主设计实验报告——Verilog秒表

姓名 班级 学号 实验日期 节次 教师签字 成绩

基于BASYS2开发板的

记忆秒表设计

一、实验目的

1、熟悉基于Verilog HDL语言输入方式的数字电路的设计方法。

2、掌握基于FPGA的设计流程。

3、熟悉BASYS2开发板的使用方法。

4、熟悉Xilinx ISE软件的使用方法。

5、培养自己独立自主设计并完成实验的能力。

二、总体设计方案或技术路线

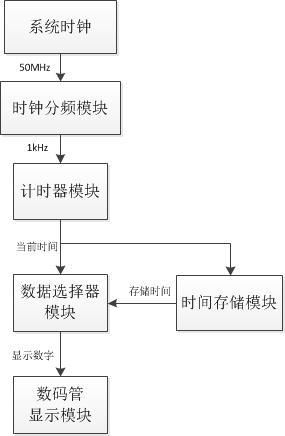

本实验利用BASYS2开发板的已有资源来进行设计实验,并用Xilinx ISE软件来编写和综合Verilog代码。总体设计方案是设计一个带有记忆功能的秒表。具体而言,该秒表通过BASYS2开发板的50M的时钟进行分频计时,最大计时时间为99.99s,用4位数码管动态显示计时时间,除了有基本的运行、暂停及复位清空功能,还有存储当前时间和查看存储时间的功能。

三、实验电路图

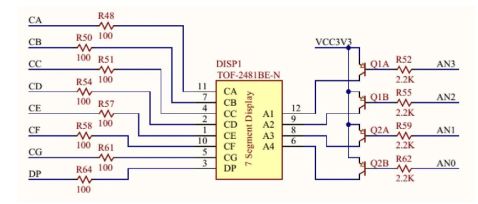

BASYS2开发板原理图--数码管

板上数码管为4位共阳极数码管,每段为低电平点亮,位选接了三极管增大驱动电流,同时为非逻辑,所以位选信号为低电平有效。

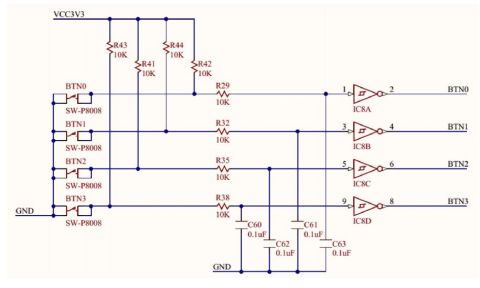

BASYS2开发板原理图--按键

本实验用到了两个按键BTN0和BTN1,BTN0为复位按键,对应程序的clear信号,BTN1为存储按键,对应程序的btn[1]信号,按一次该按键数据存储一次,下一次按下时这一次存的数据将被替换掉。

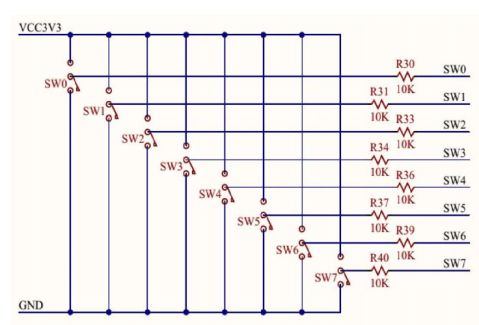

BASYS2开发板原理图--开关

本实验用到了两个开关SW7和SW1,SW7为运行、暂停开关,对应程序的sw[0]信号,开关打到上方为运行,下方为暂停,SW1为显示切换开关,对应程序的sw[1]信号,在计时暂停的前提下,将开关打到上方显示出存储的时间数据。

四、仪器设备名称、型号和技术指标 硬件:BASYS2开发板

软件:Xilinx ISE(编程)、Digilent Adept(下载)

五、程序流程图

六、程序源代码

/////////////////////////////////////////////////////////程序文件 `timescale 1ns / 1ps

////////////////////////////////////////////////////////////////////////////////// // Company:

// Engineer:

//

// Create Date: 15:45:01 11/26/2014 // Design Name:

// Module Name: miaobiao

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

///////////////////////////////////////////////////////////秒表的顶层模块

module miaobiao(

input wire clk,///////////////////////////////开发板系统时钟50MHz

input wire[1:0] btn,////////////////////////两个按键:[0]复位和[1]存时间

input wire[1:0] sw,/////////////////////////两个开关:[0]运行/暂停和[1]显示存储时间 output wire[7:0] smg,/////////////////////数码管的8个段选信号

output wire[3:0] smg_an/////////////////数码管的4个位选信号

);

wire clear;

assign clear=btn[0];////////////////////////////////////将复位按键信号传给clear变量

wire clk_1k;

clkdiv #(50000) m0(clk,clear,clk_1k);//将50MHz进行5万分频输出1kHz时钟信号

wire[15:0]number;

timer m1(sw[0]&clk_1k,clear,number);///////////计时器模块,输出当前时间数据

wire[15:0]num_save;

save m2(clk,clear,btn[1],number,num_save);//////按键按下存储当前时间

wire[15:0]num_display;

/////////////////////////////////////////////////////////////////////////////根据开关状态选择显示内容 choose_4num m3(sw,number,num_save,num_display);

display m4(clk_1k,clear,num_display,smg,smg_an);///////将数字送给数码管显示

endmodule

///////////////////////////////////////////////////////////////////////////////4选1数据选择器模块 module choose_4num(

input wire[1:0]sw,

input wire[15:0]number,

input wire[15:0]num_save,

output reg[15:0]num_display

);

always@(*)

case(sw)

0:num_display<=number;/////////////显示内容为当前时间

1:num_display<=number;/////////////。。。。。。。。。当前时间 2:num_display<=num_save;/////////显示内容为存储时间

3:num_display<=number;/////////////。。。。。。。。。当前时间 default:num_display<=number;

endcase

endmodule

//////////////////////////////////////////////////////////////////////////////////存储时间模块 module save(

input wire clk_save,

input wire clear,

input wire button,

input wire[15:0]number,

output reg[15:0]num_save

);

always@(posedge clk_save)

begin

if(1==clear)

num_save<=0;

else if(1==button)

num_save<=number;

else

num_save<=num_save;

end

endmodule

//////////////////////////////////////////////////////////////////////////////////////计时器模块 module timer(

input wire clk_timer,

input wire clear,

output reg[15:0] number

);

reg[3:0] reg_1ms;

always@(posedge clk_timer,posedge clear)

begin

if(1==clear)

begin

number<=0;

reg_1ms<=0;

end

else

begin

reg_1ms<=reg_1ms+1;

if(reg_1ms>=9)///////////////1ms的计数变量到10清零,同时10ms变量加一 begin

reg_1ms<=0;

number[3:0]<=number[3:0]+1;

if(number[3:0]>=9)////10ms变量到10清零,100ms加一

begin

number[3:0]<=0;

number[7:4]<=number[7:4]+1;

if(number[7:4]>=9)////100ms变量到10清零,1s加一

begin

number[7:4]<=0;

number[11:8]<=number[11:8]+1;

if(number[11:8]>=9)/////1s到10清零,10s加一

begin

number[11:8]<=0;

number[15:12]<=number[15:12]+1;

if(number[15:12]>=9)////10s变量到10清零

number[15:12]<=0;///综上,计时到99.99s后清零 end

end

end

end

end

end

endmodule

/////////////////////////////////////////////////////////////////////////////////////动态扫描显示数字模块 module display(

input wire clk_dis,

input wire clear,

input wire[15:0] number,

output wire[7:0] smg,

output wire[3:0] smg_an

);

reg[1:0] counter;

reg[3:0] reg_num;

wire dp;

always@(posedge clk_dis,posedge clear)

begin

if(1==clear)

begin

counter<=0;

end

else

counter<=counter+1;

end

always@(*)

begin

case(counter)

0:reg_num<=number[3:0];////////将10ms 变量送到数码管第0位显示 1:reg_num<=number[7:4];////////将100ms 变量送到数码管第1位显示 2:reg_num<=number[11:8];//////将1s 变量送到数码管第2位显示 3:reg_num<=number[15:12];////将10s 变量送到数码管第3位显示 default:reg_num<=0;

endcase

end

assign dp=(2==counter);//////////////////第2位数码管的小数点点亮,其余小数点熄灭 num2smg m0(counter,reg_num,dp,smg_an,smg);

endmodule

//////////////////////////////////////////////////////////////////////////////////////时钟分频模块 module clkdiv

#(parameter div=50000)///////默认5万分频

(input wire clk,

input wire clear,

output reg new_clk

);

reg[31:0] counter;

always@(posedge clk,posedge clear)

begin

if(1==clear)

begin

counter<=0;

new_clk<=0;

end

else if(counter>=div/2-1)

begin

counter<=0;

new_clk<=~new_clk;//二分频

end

else

counter<=counter+1;

end

endmodule

///////////////////////////////////////////////////////////////////////////数字转换成数码管段、位码模块 module num2smg(

// input wire clk_smg,

input wire[1:0] which,

input wire[3:0] num,

input wire dp,//dp=1时,点亮小数点

output reg[3:0] smg_an,

output wire[7:0] smg

);

always@(*)

case(which)/////////////////////////////////////////数码管位选子模块

3:smg_an<=4'b0111;

2:smg_an<=4'b1011;

1:smg_an<=4'b1101;

0:smg_an<=4'b1110;

default:smg_an<=4'b1111;

endcase

reg[7:0] r_smg;

always@(*)//////////////////////////////////////////////数码管段选子模块

begin

case(num)

0:r_smg<=8'hc0;

1:r_smg<=8'hf9;

2:r_smg<=8'ha4;

3:r_smg<=8'hb0;

4:r_smg<=8'h99;

5:r_smg<=8'h92;

6:r_smg<=8'h82;

7:r_smg<=8'hf8;

8:r_smg<=8'h80;

9:r_smg<=8'h90;

10:r_smg<=8'h88;

11:r_smg<=8'h83;

12:r_smg<=8'hc6;

13:r_smg<=8'ha1;

14:r_smg<=8'h86;

15:r_smg<=8'h8e;

default:r_smg<=8'hff;

endcase

end

assign smg=r_smg-128*dp;////////////////////////////////////判断是否显示小数点

endmodule

////////////////////////////////////////////////////////////////////////////程序结束END

//////////////////////////////////引脚约束文件

////////////////////////////////////////////////////时钟约束

NET"clk"TNM_NET=clk;

TIMESPEC TS_CLK=PERIOD"clk"20ns high 50%;

NET"clk"LOC="B8";

//////////////////////////////////////////////////////////数码管

NET"smg<7>"LOC="N13";

NET"smg<6>"LOC="M12";

NET"smg<5>"LOC="L13";

NET"smg<4>"LOC="P12";

NET"smg<3>"LOC="N11";

NET"smg<2>"LOC="N14";

NET"smg<1>"LOC="H12";

NET"smg<0>"LOC="L14";

NET"smg_an<3>"LOC="K14";

NET"smg_an<2>"LOC="M13";

NET"smg_an<1>"LOC="J12";

NET"smg_an<0>"LOC="F12";

//////////////////////////////////////////////////////按键

//NET"btn<3>"LOC="A7";

//NET"btn<2>"LOC="M4";

NET"btn<1>"LOC="C11";

NET"btn<0>"LOC="G12";

////////////////////////////////////////////////////开关

NET"sw<1>"LOC="L3";

NET"sw<0>"LOC="N3";

七、实验结果

最后,成功地编写出程序,调试通过,完成所有功能,整个设计达到预期目标:最大计时时间为99.99s,用4位数码管动态显示计时时间,除了有基本的运行、暂停及复位清空功能,还有存储当前时间和查看存储时间的功能。

八、实验中出现的问题及解决对策

问题一:数码管按照板子上给的位选引脚编号进行引脚约束后,发现4个数码管显示

的内容恰好反过来。

解决对策:用万用表检查电路后,再通过每一位数码管单独静态显示的测试后,证明确实是板子上给的引脚编号有误,在引脚约束文件中对4位数码管的引脚约束进行了修改之后,最后成功地改变了显示顺序,达到了预期的效果。

问题二:每次综合的时候都出现了很多很多的错误和警告。

解决对策:首先,通过软件给出的提示进行修改,解决了一部分错误和警告;然后,将错误和警告代码复制粘贴到网上进行搜索,寻找解决方案,又解决了一部分错误和警告;最后,给老师和学长发邮件请教,或者当面请教寻求帮助,解决了所有错误和又一部分警告,剩下几个警告直接无视,下载到开发板后证明对秒表的功能没有任何影响,说明这些警告可以忽视。

九、本次实验的收获和体会、对电路实验室的意见或建议

收获和体会:

本次实验,我从一开始的完全不懂FPGA到最后学会FPGA并且成功完成整个实验内容,我最大的收获就是一种自信和成就感,这增加了我在以后的学习生活中面对困难时的勇气和决心。在老师教授FPGA之前,我自己尝试去提前自学FPGA,边看文档边学习,通过对例程的编写和思考完成了基础知识的构建,然后自己编程锻炼和提高编程水平。在FPGA的编程控制过程中,我建立了模块化编程的思想,明白了FPGA触发式的运行方式,初步学会了FPGA编程,并且对FPGA产生了浓厚的兴趣。

但是,从另一方面我也明白了自己掌握的知识只是冰山一角,要想能力更强,还需要付出更多努力。

意见和建议:

1、希望实验室可以根据课程进度安排实验内容。

2、希望实验室能举办更多的FPGA的培训。

3、希望仿真实验室能在所有电脑上都安装Xilinx ISE软件。

4、希望实验室能定期检查领取了BASYS2开发板的同学的学习进度,或者安排定期必须完成的小任务,督促大家认真学习BASYS2开发板。

十、参考文献

[1] 廉玉欣. 电子技术基础实验教程.

[2] 孟涛. 电工电子EDA实践教程.

[3] 王伟. Verilog HDL程序设计与应用.

[4] 云创工作室. Verilog HDL程序设计与实践. 北京:机械工业出版社,2013.2. 北京:机械工业出版社,2010.2. 北京:人民邮电出版社,2005.3. 北京:人民邮电出版社,2009.2.

-

数字秒表设计总结报告

数字秒表课程设计总结报告一课题名称数字秒表设计二内容摘要本实验要求设计一个计数范围在0099秒的数字秒表电路设计基本包括01秒脉冲…

-

电子秒表设计报告

电子秒表设计报告目录1设计目的12设计任务和要求23设计的方案的选择和论证34电路设计计算与分析441模块总体方案设计441155…

-

99秒表设计报告

0099秒表设计报告一设计题目和要求题目三秒表应用AT89C51的定时器设计一个2位的LED数码显示作为秒表显示时间为0099s每…

-

简易秒表设计报告

一.前言在电子科学技术高速发展的今天,高科技产品越来越多的应用在我们的日常生活中,给我们的生活带来了非常大的方便,每时每秒我们都能…

-

电子秒表课程设计报告

电子秒表1设计课题任务及指标1通过本设计的选题方案论证设计计算安装调试资料整理撰写设计报告等环节初步掌握电子工程设计方法和组织实施…

-

数字电路课程设计总结报告

数字电路课程设计总结报告题目数字钟设计专业班级学生姓名学号指导教师日期20xx年12月11目录一设计任务1一设计课题1二功能要求1…

-

数字电路课程设计总结报告

数字电路课程设计总结报告题目:交通灯控制器1、设计背景2、设计任务书3、设计框图及总体描述4、各单元设计电路设计方案与原理说明5、…

-

数字电路实验报告3

暨南大学本科实验报告专用纸课程名称数字逻辑电路实验成绩评定实验项目名称三态门特性研究和典型应用指导教师实验项目编号08060038…

-

数字电路综合设计实验报告文档

数字电路综合设计课程报告姓名学号班级20xx0530数字电路综合设计目录一设计题目错误未定义书签二设计要求及技术指标错误未定义书签…

-

数字电路课程设计报告(好)

天津职业技术师范大学电子工程学院电子技术之万用表课程设计报告同组学生姓名学号寡人猪八戒任务分工查阅资料设计电路并进行电脑仿真设计时…

-

数电实验报告

北京邮电大学数字电路与逻辑设计实验实验名称学班姓学实验报告QuartusII原理图输入法设计与实现院级名号一实验名称Quartus…