EDA课程设计——交通信号灯控制器设计 2

海南大学信息科学技术学院

《EDA技术课程设计报告》

专业班级:20##级通信工程

姓 名: 刘 洋

学 号:20081604B062

指导老师:刘文进 老师

目 录

课程设计的要求及目的……………………………………………2

前言………………………………………………………………… 2

一设计内容与目的……………………………………………… 2

1.1设计内容………………………………………………… 3

1.2 设计目的………………………………………………… 3

二方案设计……………………………………………………… 3

2.1 设计思路…………………………………………………3

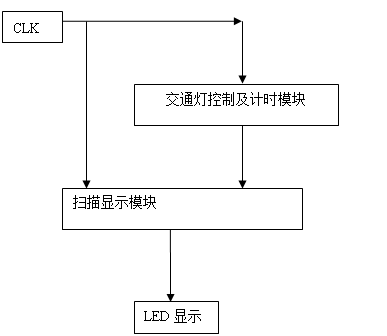

2.2 设计总体框图……………………………………………4

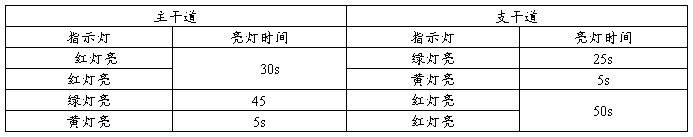

2.3 状态表……………………………………………………5

2.4 电路原理图………………………………………………5

2.5 静态显示电路……………………………………………5

三功能电路的设计……………………………………………… 5

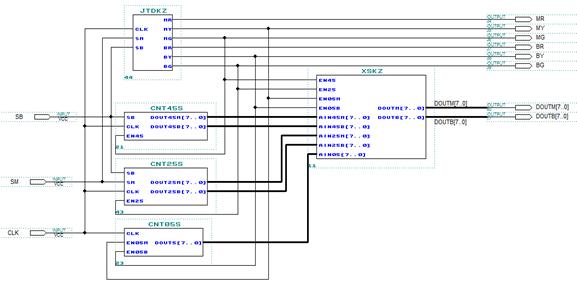

3.1 细化的设计总体框图……………………………………5

3.2 灯控制器电路设计………………………………………6

3.3 计数器设计………………………………………………8

3.4 显示控制部分设计………………………………………12

四系统仿真图……………………………………………………13

五设计心得会……………………………………………………14

六参考文献………………………………………………………15

交通信号灯控制器设计

课程设计的要求及目的:

1.了解电子设计的具体流程和方法。

2. 掌握电子设计的基本要求,能够运用所学的知识解决生活中的一些问题。

3. 初步掌握VHDL语言编程,并设计出一个有意义的小型系统。

4. 掌握MAX+plus Ⅱ软件的应用,并且了解相关硬件的组成和功能。

5. 用EDA(Electronic Design Automation)或者原理图完成一个课题的设计,并达到相应的功能要求。

前言

伴随着社会的发展以及人类生活水平的提高,汽车的数量在不断增加,交通事业得以蓬勃发展,而随之引起的安全问题已经不容忽视。EDA技术的发展和应用领域也在不断的扩大与深入,机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域的重要性日益突出。众所周知,随着生活的进步,我们身边的交通也日益繁忙,在众多的十字交叉路口,为了确保车辆安全,迅速地通行,就必须在每个入口设置红绿灯。本系统中设置了红,绿,黄三色共三种信号灯。红灯亮禁止一切该方向的行人和车辆通行,绿灯亮允许行人和车辆通行,黄灯亮则提示行驶中的车辆注意不要抢道,并让它们有时间停靠到禁行线之外或者加快通过,同时提醒行人加快行进或者等待下一次绿灯。人行道灯亮时,允许行人通过。

为了确保十字路口的行人和车辆顺利,畅通的通过,往往采用电子控制的交通信号来进行指挥。利用EDA技术设计交通灯来完成这个需求就显的更加迫切,同样也是非常的实用和合理。本交通信号灯控制系统以十字路口为例讲述设计的功能要求和设计的具体过程。

一 设计内容与目的:

1.1 设计内容:

用EDA设计一个简单的交通灯控制器,具有如下功能:

(1)设计一个交通信号灯控制器,由一条主干道和一条支干道汇合成十字路口,在每个入口处设置红、绿、黄三色信号灯,红灯亮禁止通行,绿灯亮允许通行,黄灯亮则给行驶中的车辆有时间停在禁行线外。

(2)用红、绿、黄发光二极管作信号灯,用传感器或逻辑开关作检测车辆是否到来的信号。

(3)主干道处于常允许通行的状态,支干道有车来时才允许通行。主干道亮绿灯时,支干道亮红灯;支干道亮绿灯时,主干道亮红灯。

主、支干道均有车时,两者交替允许通行,主干道每次放行45秒,支干道每次放行25秒,设立45秒、25秒计时、显示电路。

(4)在每次由绿灯亮到红灯亮的转换过程中,要亮5秒黄灯作为过渡,使行驶中的车辆有时间停到禁行线外,设立5秒计时、显示电路。

1.2 设计目的:

(1)掌握十字路口交通灯控制的设计原理,并能够运用VHDL编程语言编写出实验程序,进一步对所学的EDA知识进行掌握与实际应用。

(2)学会在MAX+plus Ⅱ软件环境中仿真,熟悉软件的基本操作和运行环境。

(3)锻炼自己获取信息的能力,以及能够独立自主的思考和解决问题的能力。

二 方案设计:

2.1设计思路

(1) 主、支干道用传感器检测车辆到来情况,实验电路用逻辑开关代替。

(2) 45秒、25秒、5秒定时信号可用顺计时,也可用倒计时,计时起始信号由主控电路给出,定时结束信号也输入到主控电路,由主控电路启、闭三色信号灯或启动另一计时电路。

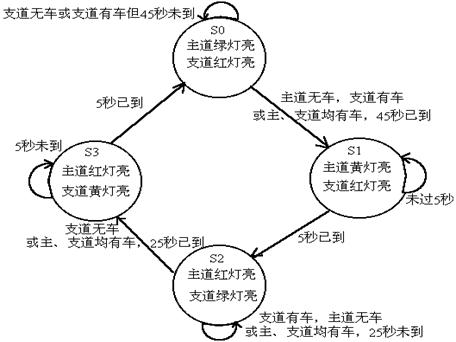

(3) 主控电路是核心,这是一个时序电路,其输入信号为:车辆检测信号(A,B); 45秒、25秒、5秒定时信号(C,D,E)。其状态转化图如下所示:

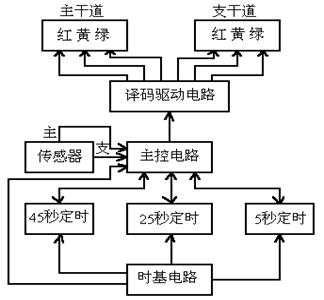

2.2 设计总体框图:

2.3状态表

2.4 电路原理图:

2.5 输出显示电路 : 静态扫描电路。

三功能电路的设计

3.1细化的设计总体框图

根据设计要求和系统所具有功能,并参考相关的文献资料经行方案设计画出如下所示的十字路口交通灯控制器系统框图,及为设计的总体方案,框图如下图3.1所示

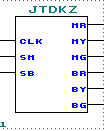

3.2 灯控制器电路设计

由一条主干道和一条支干道汇合成十字路口,在每个入口处设置红、绿、黄、左拐允许四盏信号灯,红灯亮禁止通行,绿灯亮允许通行,黄灯亮则给行驶中的车辆有时间停在禁行线外,左拐灯亮允许车辆向左拐弯。信号灯变换次序为:主支干道交替允许通行,主干道每次放行40S,亮5S红灯让行驶中的车辆有时间停到禁行线外,左拐放行15秒,亮5S红灯;支干道放行30S,亮5S黄灯,左拐放行15秒,亮5S红灯,其中主支干道的红黄绿灯表示如MR、MY、MG、BR、BY、BG。

程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY JTDKZ IS

PORT(CLK,SM,SB:IN STD_LOGIC;

MR,MY,MG,BR,BY,BG:OUT STD_LOGIC);

END ENTITY JTDKZ;

ARCHITECTURE ART OF JTDKZ IS

TYPE STATE_TYPE IS(A,B,C,D);

SIGNAL STATE:STATE_TYPE;

BEGIN

CNT:PROCESS(CLK)IS

VARIABLE S:INTEGER RANGE 0 TO 45;

VARIABLE CLR,EN:BIT;

BEGIN

IF(CLK'EVENT AND CLK='1') THEN

IF CLR='0'THEN

S:=0;

ELSIF EN='0'THEN

S:=S;

ELSE

S:=S+1;

END IF;

CASE STATE IS

WHEN A=>MR<='0';MY<='0';MG<='1';

BR<='1';BY<='0';BG<='0';

IF(SB AND SM)='1'THEN

IF S=45 THEN

STATE<=B;CLR:='0';EN:='0';

ELSE

STATE<=A;CLR:='1';EN:='1';

END IF;

ELSIF(SB AND (NOT SM))='1'THEN

STATE<=B;CLR:='0';EN:='0';

ELSE

STATE<=A;CLR:='1';EN:='1';

END IF;

WHEN B=>MR<='0';MY<='1';MG<='0';

BR<='1';BY<='0';BG<='0';

IF S=5 THEN

STATE<=C;CLR:='0';EN:='0';

ELSE

STATE<=B;CLR:='1';EN:='1';

END IF;

WHEN C=>MR<='1';MY<='0';MG<='0';

BR<='0';BY<='0';BG<='1';

IF(SM AND SB)='1'THEN

IF S=25 THEN

STATE<=D;CLR:='0';EN:='0';

ELSE

STATE<=C;CLR:='1';EN:='1';

END IF;

ELSIF SB='0'THEN

STATE<=D;CLR:='0';EN:='0';

ELSE

STATE<=C;CLR:='1';EN:='1';

END IF;

WHEN D=>MR<='1';MY<='0';MG<='0';

BR<='0';BY<='1';BG<='0';

IF S=5 THEN

STATE<=A;CLR:='0';EN:='0';

ELSE

STATE<=D;CLR:='1';EN:='1';

END IF;

END CASE;

END IF;

END PROCESS CNT;

END ARCHITECTURE ART;

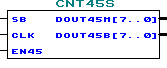

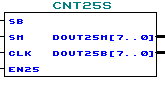

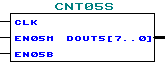

3.3 计数器的设计

根据路上状况,设计各个显示计时部分,包括45s、25s和5s,各部分采用顺时计数方法。各模块如下:

程序如下:

----CNT45S.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT45S IS

PORT

(SB,CLK,EN45:IN STD_LOGIC;

DOUT45M,DOUT45B:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY CNT45S;

ARCHITECTURE ART OF CNT45S IS

SIGNAL CNT6B:STD_LOGIC_VECTOR(5 DOWNTO 0);

BEGIN

PROCESS(SB,CLK,EN45) IS

BEGIN

IF SB='0' THEN CNT6B<=CNT6B-CNT6B-1;

ELSIF(CLK'EVENT AND CLK='1')THEN

IF EN45='1' THEN CNT6B<=CNT6B+1;

ELSIF EN45='0' THEN CNT6B<=CNT6B-CNT6B-1;

END IF;

END IF;

END PROCESS;

PROCESS(CNT6B)IS

BEGIN

CASE CNT6B IS

WHEN"000000"=>DOUT45M<="01000101";DOUT45B<="01010000";

WHEN"000001"=>DOUT45M<="01000100";DOUT45B<="01001011";

WHEN"000010"=>DOUT45M<="01000011";DOUT45B<="01001000";

WHEN"000011"=>DOUT45M<="01000010";DOUT45B<="01000111";

WHEN"000100"=>DOUT45M<="01000001";DOUT45B<="01000110";

WHEN"000101"=>DOUT45M<="01000000";DOUT45B<="01000101";

WHEN"000110"=>DOUT45M<="00111001";DOUT45B<="01000100";

WHEN"000111"=>DOUT45M<="00111000";DOUT45B<="01000011";

WHEN"001000"=>DOUT45M<="00110111";DOUT45B<="01000010";

WHEN"001001"=>DOUT45M<="00110110";DOUT45B<="01000001";

WHEN"001010"=>DOUT45M<="00110101";DOUT45B<="01000000";

WHEN"001011"=>DOUT45M<="00110100";DOUT45B<="01101001";

WHEN"001100"=>DOUT45M<="00110011";DOUT45B<="00111000";

WHEN"001101"=>DOUT45M<="00110010";DOUT45B<="00110111";

WHEN"001110"=>DOUT45M<="00110001";DOUT45B<="00110110";

WHEN"001111"=>DOUT45M<="00110000";DOUT45B<="00110101";

WHEN"010000"=>DOUT45M<="00101001";DOUT45B<="00110100";

WHEN"010001"=>DOUT45M<="00101000";DOUT45B<="00110011";

WHEN"010010"=>DOUT45M<="00100111";DOUT45B<="00110010";

WHEN"010011"=>DOUT45M<="00100110";DOUT45B<="00110001";

WHEN"010100"=>DOUT45M<="00100101";DOUT45B<="00110000";

WHEN"010101"=>DOUT45M<="00100100";DOUT45B<="00101001";

WHEN"010110"=>DOUT45M<="00100011";DOUT45B<="00101000";

WHEN"010111"=>DOUT45M<="00100010";DOUT45B<="00100111";

WHEN"011000"=>DOUT45M<="00100001";DOUT45B<="00100110";

WHEN"011001"=>DOUT45M<="00100000";DOUT45B<="00100101";

WHEN"011010"=>DOUT45M<="00011001";DOUT45B<="00100100";

WHEN"011011"=>DOUT45M<="00011000";DOUT45B<="00100011";

WHEN"011100"=>DOUT45M<="00010111";DOUT45B<="00100010";

WHEN"011101"=>DOUT45M<="00010110";DOUT45B<="00100001";

WHEN"011110"=>DOUT45M<="00010101";DOUT45B<="00100000";

WHEN"011111"=>DOUT45M<="00010100";DOUT45B<="00011001";

WHEN"100000"=>DOUT45M<="00010011";DOUT45B<="00011000";

WHEN"100001"=>DOUT45M<="00010010";DOUT45B<="00010111";

WHEN"100010"=>DOUT45M<="00010001";DOUT45B<="00010110";

WHEN"100011"=>DOUT45M<="00010000";DOUT45B<="00010101";

WHEN"100100"=>DOUT45M<="00001001";DOUT45B<="00010100";

WHEN"100101"=>DOUT45M<="00001000";DOUT45B<="00010011";

WHEN"100110"=>DOUT45M<="00000111";DOUT45B<="00010010";

WHEN"100111"=>DOUT45M<="00000110";DOUT45B<="00010001";

WHEN"101000"=>DOUT45M<="00000101";DOUT45B<="00010000";

WHEN"101001"=>DOUT45M<="00000100";DOUT45B<="00001001";

WHEN"101010"=>DOUT45M<="00000011";DOUT45B<="00001000";

WHEN"101011"=>DOUT45M<="00000010";DOUT45B<="00000111";

WHEN"101100"=>DOUT45M<="00000001";DOUT45B<="00000110";

WHEN OTHERS=>DOUT45M<="00000000";DOUT45B<="00000000";

END CASE;

END PROCESS;

END ARCHITECTURE ART;

--CNT25S.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT25S IS

PORT(SB,SM,CLK,EN25:IN STD_LOGIC;

DOUT25M,DOUT25B:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY ;

ARCHITECTURE ART OF CNT25S IS

SIGNAL CNT5B:STD_LOGIC_VECTOR(4 DOWNTO 0);

BEGIN

PROCESS (SB,SM,CLK,EN25) IS

BEGIN

IF SB='0' OR SM='0'THEN

CNT5B<=CNT5B-CNT5B-1;

ELSIF(CLK'EVENT AND CLK='1')THEN

IF EN25='1'THEN

CNT5B<=CNT5B+1;

ELSIF EN25='0'THEN

CNT5B<=CNT5B-CNT5B-1;

END IF;

END IF;

END PROCESS;

PROCESS(CNT5B)IS

BEGIN

CASE CNT5B IS

WHEN "00000"=>DOUT25B<="00100101";DOUT25M<="00110000";

WHEN "00001"=>DOUT25B<="00100100";DOUT25M<="00101001";

WHEN "00010"=>DOUT25B<="00100011";DOUT25M<="00101000";

WHEN "00011"=>DOUT25B<="00100010";DOUT25M<="00100111";

WHEN "00100"=>DOUT25B<="00100001";DOUT25M<="00100110";

WHEN "00101"=>DOUT25B<="00100000";DOUT25M<="00100101";

WHEN "00110"=>DOUT25B<="00011001";DOUT25M<="00100100";

WHEN "00111"=>DOUT25B<="00011000";DOUT25M<="00100011";

WHEN "01000"=>DOUT25B<="00010111";DOUT25M<="00100010";

WHEN "01001"=>DOUT25B<="00010110";DOUT25M<="00100001";

WHEN "01010"=>DOUT25B<="00010101";DOUT25M<="00100000";

WHEN "01011"=>DOUT25B<="00010100";DOUT25M<="00011001";

WHEN "01100"=>DOUT25B<="00010011";DOUT25M<="00011000";

WHEN "01101"=>DOUT25B<="00010010";DOUT25M<="00010111";

WHEN "01110"=>DOUT25B<="00010001";DOUT25M<="00010110";

WHEN "01111"=>DOUT25B<="00010000";DOUT25M<="00010101";

WHEN "10000"=>DOUT25B<="00001001";DOUT25M<="00010100";

WHEN "10001"=>DOUT25B<="00001001";DOUT25M<="00010100";

WHEN "10010"=>DOUT25B<="00001000";DOUT25M<="00010011";

WHEN "10011"=>DOUT25B<="00000110";DOUT25M<="00010001";

WHEN "10100"=>DOUT25B<="00000101";DOUT25M<="00010000";

WHEN "10101"=>DOUT25B<="00000100";DOUT25M<="00001001";

WHEN "10110"=>DOUT25B<="00000011";DOUT25M<="00001000";

WHEN "10111"=>DOUT25B<="00000010";DOUT25M<="00000111";

WHEN "11000"=>DOUT25B<="00000001";DOUT25M<="00000110";

WHEN OTHERS=>DOUT25B<="00000000";DOUT25M<="00000000";

END CASE;

END PROCESS;

END ARCHITECTURE ART;

--CNT05S.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT05S IS

PORT

(CLK,EN05M,EN05B:IN STD_LOGIC;

DOUT5:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY CNT05S;

ARCHITECTURE ART OF CNT05S IS

SIGNAL CNT3B:STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

PROCESS(CLK,EN05M,EN05B) IS

BEGIN

IF(CLK'EVENT AND CLK='1')THEN

IF EN05M='1' THEN CNT3B<=CNT3B+1;

ELSIF EN05B='1' THEN CNT3B<=CNT3B+1;

ELSIF EN05B='0' THEN CNT3B<=CNT3B-CNT3B-1;

END IF;

END IF;

END PROCESS;

PROCESS(CNT3B)IS

BEGIN

CASE CNT3B IS

WHEN"000"=>DOUT5<="00000101";

WHEN"001"=>DOUT5<="00000100";

WHEN"010"=>DOUT5<="00000011";

WHEN"011"=>DOUT5<="00000010";

WHEN"100"=>DOUT5<="00000001";

WHEN OTHERS=>DOUT5<="00000000";

END CASE;

END PROCESS;

END ARCHITECTURE ART;

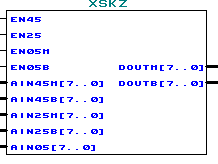

3.4 显示控制部分设计

根据从JZKZ部件中检测到个路况,从而使不同路况显示不同的计数时间,模块如下:

程序如下:

--XSKZ.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY XSKZ IS

PORT(EN45,EN25,EN05M,EN05B:IN STD_LOGIC;

AIN45M,AIN45B:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

AIN25M,AIN25B,AIN05:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

DOUTM,DOUTB:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY XSKZ;

ARCHITECTURE ART OF XSKZ IS

BEGIN

PROCESS(EN45,EN25,EN05M,EN05B)IS

BEGIN

IF EN45='1'THEN

DOUTM<=AIN45M(7 DOWNTO 0);DOUTB<=AIN45B(7 DOWNTO 0);

ELSIF EN05M='1'THEN

DOUTM<=AIN05(7 DOWNTO 0);DOUTB<=AIN05(7 DOWNTO 0);

ELSIF EN25='1'THEN

DOUTM<=AIN25M(7 DOWNTO 0);DOUTB<=AIN25B(7 DOWNTO 0);

ELSIF EN05B='1'THEN

DOUTM<=AIN05(7 DOWNTO 0);DOUTB<=AIN05(7 DOWNTO 0);

END IF;

END PROCESS;

END ARCHITECTURE ART;

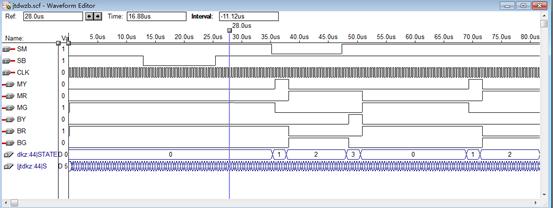

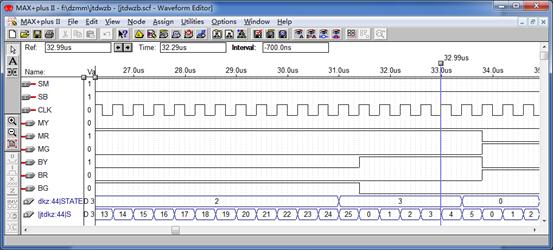

四 总体仿真波形

图4.1 JTDKZWZB.VHD的全局仿真结果

图4.2 JTDKZWZB.VHD的局部仿真结果

从图4.1和图4.2可以看出,本设计符合设计初衷,完成看所要求的设计任务。

五 设计心得体会

经过为其两周的课程设计,本人受益匪浅。这是我们自己大学三年以来自己第一次动手设计自己的东西,而不仅仅是停留在理论上。这一次的课程设计让我懂得了理论的指导意义,同时也深深知道自己实际动手能力的缺乏,深深认识到加强自己的理论指导实践的能力的紧迫性和重要性。

选了交通灯控制这一小项目,因为它很简单,很容易的就用原理图或者状态机设计完成。这是我选择它的最重要的原因。但是看是简单的交通灯控制,却让我明白,要想靠自己成功的完成,还得老老实实的花大力气去做。刚开始,由于MAX+plus Ⅱ这软件对我来说完全陌生,不知道怎么操作,我花了几乎三天的时间去熟悉它,但是还是不能很好的“驾驭”它,而VHDL语言虽然简单,可是由于仓促上阵,一时间难以接受。在开始的两天,完全不知从何下手,我几乎有点想放弃的感觉,尽管之前参加过课程设计的同学都说很简单,但是我觉得非也。

接下来的几天,实验室,图书馆,旧书店开始出现了忙碌的身影,我拼命的找资料。有关EDA的和电子系统设计的书,我前后下来看了不少于6本,研究书中的有关例子,寻求设计思路和设计方法,方案,同时学习VHDL这门硬件描述语言,边学边做,仿佛自己在做一个惊天动地大项目,“废寝忘食”。在进行课程设计这两周,是我最忙的两周,每天晚上几乎都到奋战到10点才回去,很冷,但是我还是坚持下来了,尽管后面的项目做得不是很成功,但是我觉得我还是收获了不少,至起码我懂得了VHDL语言,学会了一些小系统的设计方法和设计思路。

当写显示文件的程序时,也遇到了不少问题,特别是各元件之间的连接,以及信号的定义,总是有错误,在细心的检查下,终于找出了错误和警告,排除困难后,程序编译就通过了。再对控制模块仿真时,虽然语法正确,但在实物调制方面仍遇到了问题,显示译码管总显示错误,后来在老师的指导和同学的帮助下,我们才顺利的解决了这个问题。

其次,在进行引脚连接时一定要细心,有些引脚不能使用,我因为没注意使得开始时一直不能得到正确的结果。这次EDA课程设计历时两个星期,在整整两个星期的日子里,可以说是苦多于甜,但是可以学的到很多很多的东西,同时不仅可以巩固以前所学过的知识,而且学到了很多在书本上所没有学到过的知识,进一步加强合作能力。

通过这次课程设计使我懂得了理论与实际相结合是很重要的,只有理论知识是远远不够的,只有把所学的理论知识与实践相结合起来,从理论中得出结论,才能真正为社会服务,从而提高自己的实际动手能力和独立思考的能力。在设计的过程中遇到的问题,反映出来我的许多不足之处,我以后要努力克服缺点。在进行每一个设计之前必须充分考虑各种情况,明白自己设计的目的和要求,然后围绕着设计要求为中心,充分考虑设计的条件,为实现设计要求和设计目的找到最优的方案,而不是没有考虑清楚就急着去做。这是我这次的切身体会,正所谓是看得远看得清才不会摔跤。

总的来说,这次设计的交通控制器还是比较成功的,在设计中遇到了很多问题,最后在同学和老师的辛勤的指导下外加上自己的努力,终于都得到了解决,因此很有成就感,终于觉得平时所学的知识有了实用的价值,达到了理论与实际相结合的目的。

六 参考文献

[1] 谭会生,《EDA》,西安电子电子科技大学出版社,20##年

[2] 谭会生、瞿遂春,EDA技术综合应用实例与分析,西安电子科技大学, 2004

[3] 阎石.数字电子技术基础[M].北京市西城区:高等教育出版社.20##年12月

[4] 谢自美.电子线路设计实验测试[Z].武汉:华中科技大学出版社.20##年9月

[5] 郭照南 电子技术与EDA技术课程设计

-

交通信号灯课程设计报告

单片机课程设计报告题目:基于单片机的交通灯设计专业:电子科学与技术班级:20##级电科微电班学号:姓名:完成时间:20##年12月…

-

交通信号灯课程设计报告

20xx级通信工程数字电路课程设计报告设计题目姓名及刘俊君20xx0343019交通灯控制电路周啸20xx0343061学号符勇武…

-

交通信号灯课设报告

电子技术课程设计说明书电子技术课程设计说明书题目:交通信号灯控制器(A)学生姓名:学号:院(系):专业:指导教师:20##年12月…

-

交通灯课程设计报告6

《电子技术》课程设计报告指导教师(签字)前言在现代城市中,人口和汽车日益增长,市区交通也日益拥挤,人们的安全问题也日益重要。因此,…

-

微机接口交通信号灯课程设计报告

郑州大学信息工程学院课程设计报告交通灯模拟系统序言红绿灯(交通信号灯)系以规定之时间上交互更迭之光色讯号,设置于交岔路口或其他特殊…

-

微机原理与接口技术课程设计实验报告-交通灯控制系统

《微机原理与接口技术》课程设计报告交通灯控制系统班级:学号:姓名:指导教师:成绩:xxxx年x月x日目录1、课程设计的目的和要求3…

-

EDA课程设计报告_交通灯控制与显示电路

EDA课程设计报告班级姓名组成员指导教师XXX08电信1班XXXXXX报告目录1EDA技术综述2设计实践报告1课题名称2内容摘要3…

-

哈夫曼编码与多叉路口交通灯管理课程设计报告

目录一哈夫曼编码译码器21需求分析22详细设计221哈夫曼树节点的数据类型定义为222所实现的功能函数如下223流程图33调试分析…

-

交通灯课程设计报告6

《电子技术》课程设计报告指导教师(签字)前言在现代城市中,人口和汽车日益增长,市区交通也日益拥挤,人们的安全问题也日益重要。因此,…

-

交通灯课程设计报告

桂林航院电子工程系单片机课程设计与制作说明书设计题目:智能交通灯控制专业年级:10级电子信息工程技术(1)班学号:**姓名:**同…