EDA课程设计报告

EDA 课程设计

------A/D0809转换控制设计

一、 课题要求:

二、 1.利用实验箱上FPGA芯片控制ADC0809的时序,进行AD转换,然后将ADC0809转换后的数据以十六进制的数据显示出来。

三、 2. 实现时必须严格遵守ADC0809的工作时序,在编写代码时要注意。对选定的通道输入一个模拟量,调节电位器改变输入的模拟量。

关键字:AD0809 VHDL

四、 实验目的

1、 了解ADC0809的工作原理。

2、 了解用扫描方式驱动七段码管显示的工作原理。

3、 了解时序电路FPGA的实现。

4、 学习用VHDL语言来描述时序电路的过程。

五、 硬件要求

1、 可变时钟源。

2、 七段码显示。

3、 A/D转换芯片ADC0809

4、 主芯片EP1K10TC100—3。

5、 三个拨动开关,进行地址选择。

六、 实验原理

该实验是利用FPGA控制ADC0809的时序,进行AD转换,然后将ADC0809

转换后的数据以十六进制的数据显示出来。

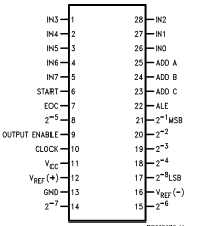

ADC0809是8位8通道的逐次比较式AD转换芯片。该芯片管脚如右图所示。芯片引脚及其说明如下:

ADC0809是8位8通道的逐次比较式AD转换芯片。该芯片管脚如右图所示。芯片引脚及其说明如下:

D0-D7(2-8-2-1):8位双先三态数据线。

ADDA、ADDB、ADDC:通道选择地址。

OUTPUT ENABLE:输出允许控制。

Clock:ADC转换时钟。

Vref+、Vref-:正负参考电压。

IN0-IN7:8个模拟信号输入通道。

START:AD转换启动信号。

EOC:AD转换结束信号。

ALE:通道地址锁存信号。 图1. AD0809引脚图

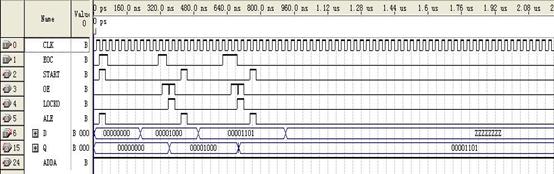

ADC0809的工作时序如下图所示。其详细工作过程可查阅其他资料。

本实验FPGA实现时必须严格遵守ADC0809的工作时序,在编写其驱动代码时尤其要注意。ADC0809的时钟信号从FPGA获取,FPGA的时钟在500KHz至800KHz都可以选择。现具体介绍代码编写思想:

首先将要转换的ADC0809的地址输出,然后产生ALE信号的,在该信号的上升沿,地址被打入ADC0809的地址锁存器,这样就选中了对应的通道。地址产生结束后,便可产生START信号,使ADC0809开始进行AD转换,需要注意的是,在ADC0809转换期间,输入的模拟信号必须稳定,否则可能出现比较大的误差。在地址锁存并且启动转换后,EOC便会呈现低电平,知道AD转换结束,所以FPGA在EOC从低电平变成高电平之前,不能读取ADC的转换数据。在EOC变成高电平之后,FPGA便可将OUTPUT INPUT信号拉高,这样ADC转换的数据就会呈现在数据线上,FPGA读入该数据后,在8位七段码管上显示出来,这就是整个实验过程的工作流程。

AD0809的工作时序如图2所示。

七、 实验内容及步骤

图2.AD0809的工作时序

本实验的内容就是用FPGA模拟产生ADC0809的时序,使其正常工作,对ADC0809输入一个模拟量,进行A/D转换,然后将读入后的数据进行显示,实验步骤如下:

1、编写ADC0809时序的VHDL代码。

2、对其进行编译仿真。

3、在时序确定无误后,选择芯片ACEX1K EP1K10TC100-3。

4、给芯片进行管脚绑定,在此进行编译。

5、根据自己绑定的管脚,在实验箱上对ADC0809、显示七段码和FPGA之间进行正确连线。

6、对选定的通道输入一个模拟量,给目标板下载代码,调节电位器改变输入的模拟量,观看实验结果。

八、实验连线

实验连线如下:

Clk:时钟输入信号,500KHz至800KHz之间均可。

EOC:输出信号,接ADC0809的EOC信号。

Din:数据输入,接ADC0809的数据总线D0-D7;

Start:输出信号,接ADC0809的START信号。

Ale:地址锁存,接ADC0809的ALE信号。

OE: 输出允许,接ADC0809的OUTPUT ENABLE信号。

Sa、Sb、Sc:七段显示选通信号,接七段码显示SEL0、SEL1和SEL2。

A、B、C、D、E、F、G:分别连接至七段码显示的a、b、c、d、e、f、g。

ADC0809的地址选择信号A、B和C分别到三个拨挡开关。

通过A、B、C选取输入通道CH0~CH7其中的相应通道输入一个可变模拟量。

九.程序流程图:

0

0

1

1

其他

上升沿

上升沿

十. 程序代码如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity display is

port ( D : in std_logic_vector(7 downto 0); --ADC0809输出的采样数据

clk,eoc : in std_logic; --clk为系统时钟,eoc为ADC0809转换结束信号

seg : out std_logic_vector(1 downto 0);

ADDA,start, ale,oe : out std_logic; --ADC0809控制信号

LOCK0 : OUT STD_LOGIC;

Q : out std_logic_vector(7 downto 0); --送至8diode

LED : out std_logic_vector (6 downto 0));

end display;

architecture behav of display is

type states is ( st0,st1, st2, st3, st4); --定义各状态的子类型

signal current_state, next_state:states;

signal regl : std_logic_vector(7 downto 0); --中间数据寄存信号

signal lock : std_logic;--lock AD output after converted

signal dcount: std_logic_vector(1 downto 0);

signal data: integer;

signal data_h : integer;

signal data_l : integer;

signal LED_0: std_logic_vector (6 downto 0);

signal LED_1: std_logic_vector (6 downto 0);

begin

ADDA<='1';--enable channel 1

Q<=regl;lock0<=lock;

com:process(current_state,eoc) --规定各种状态的转换方式

begin

case current_state is

when st0=>next_state<=st1;ale<='0';start<='0';oe<='0';lock<='0';--0809init

when st1=>next_state<=st2;ale<='1';start<='1';oe<='0';lock<='0';

when st2=>ale<='0';start<='0';oe<='0';lock<='0';

if (eoc='1') then next_state<=st3; --EOC=1 convert accomplished

else next_state<=st2;--havn't accomplish

end if;--convert haven't ending,waiting for...

when st3=> ale<='0';start<='0';lock<='0';oe<='1';next_state<=st4;--enable oe,output converted data

when st4=> ale<='0';start<='0';lock<='1';oe<='1';next_state<=st0;

when others => next_state<=st0;

end case;

end process com;

reg:process(clk)

begin

if clk'event and clk='1' then current_state<=next_state;end if; --在clk1的上升沿,转换至下一状态

end process reg;

latch1:process(lock)

begin

if lock='1'and lock'event then regl<=D;end if;

end process latch1;

process(clk,regl)

begin

if clk'event and clk='1' then dcount<=dcount+1; end if;

data<=conv_integer(regl);

data_h<=data/16;

data_l<=data rem 16;

case data_h is

when 0 => LED_0<="0111111";

when 1 => LED_0<="0000110";

when 2 => LED_0<="1011011";

when 3 => LED_0<="1001111";

when 4 => LED_0<="1100110";

when 5 => LED_0<="1101101";

when 6 => LED_0<="1111101";

when 7 => LED_0<="0000111";

when 8 => LED_0<="1111111";

when 9 => LED_0<="1101111";

when 10 => LED_0<="1110111";

when 11 => LED_0<="1111100";

when 12 =>LED_0<="0111001";

when 13 => LED_0<="1011110";

when 14 => LED_0<="1111001";

when 15 => LED_0<="1110001";

when others => null;

end case;

case data_l is

when 0 => LED_1<="0111111";

when 1 => LED_1<="0000110";

when 2 => LED_1<="1011011";

when 3 => LED_1<="1001111";

when 4 => LED_1<="1100110";

when 5 => LED_1<="1101101";

when 6 => LED_1<="1111101";

when 7 => LED_1<="0000111";

when 8 => LED_1<="1111111";

when 9 => LED_1<="1101111";

when 10 => LED_1<="1110111";

when 11 => LED_1<="1111100";

when 12 => LED_1<="0111001";

when 13 => LED_1<="1011110";

when 14 => LED_1<="1111001";

when 15 => LED_1<="1110001";

when others => null;

end case;

seg<=dcount;--00 01 10 11 00

case dcount is

when "00"=>LED<=LED_0;

when "01"=>LED<=LED_1;

when others=>LED<="0000000";

end case;

end process;

end behav;

Ad0809 的仿真时序如图3

图3.AD0809仿真时序

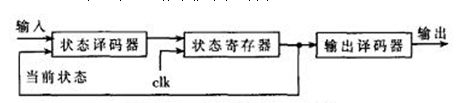

Moore型状态机组成框图如图4所示。

图4 Moore型有限状态机组成框图

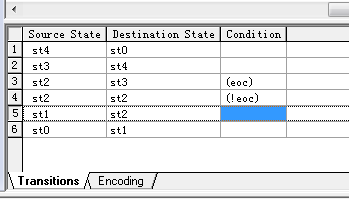

在仿真完成以后可以生成状态图如图5:

图5.ADC0809状态图

也可表示为图6所示的状态表:

图6.ADC0809状态表

十.心得体会

通过这次有关于EDA技术的课程设计的学习与应用,我们基本了解了EDA技术的相关应用,也掌握了EDA设计的相关软件Quartus7.2的最基础的使用方法,丰富了我们的设计手段,也让我了解了更多的仿真方法。

在上机操作的过程中,刚开始我们遇到了很多的困难,对软件的不熟悉以及对原理掌握的不透彻,使得刚开始的时候举步维艰,但是经过对最简单的模型的设计及仿真练习过后,我们基本掌握了软件的使用方法,再根据我们所学习过的数电模电的知识将四位全加器的原理图做出来之后,通过软件仿真及对各个参数的设置,我们不断调试仿真出来的波形,是全加器的仿真达到最佳效果。这期间我们也了解到,虽然软件的仿真功能很强大,但是还是需要操作人员仔细的进行观察及调试的,否则也容易出现仿真错误。

这次的学习开阔了我们的视野,使我们了解了更多的专业方面的实际应用,在生产应用方面的用处等,以及专业方面的发展方向等……随着微电子技术和计算机技术的不断发展,在涉及通信、国防、航天、工业自动化、仪器仪表等领域的电子系统设计工作中,EDA技术的含量正以惊人的速度上升,它已成为当今电子技术发展的前沿之一。 EDA技术发展迅猛,完全可以用日新月异来描述。EDA技术的应用广泛,现在已涉及到各行各业。EDA水平不断提高,设计工具趋于完美的地步,所以我们更加应该多多掌握这方面的知识。

十一.参考文献:

【1】 电子技术应用 20##年09期

【2】潘松,黄继业 . EDA技术实用教程(第三版). 科学出版社 . 20##-07

【3】曾繁泰 陈美金 VHDL程序设计[M].北京:清华大学出版社,2001

-

课程设计报告

1课程设计目的课程设计是船舶设计原理课程重要的实践性教学环节是培养学生掌握船舶设计基本原理和能力的技术基础主尺度论证与总布置设计是…

-

课程设计报告内容

一设计目的1强化上机动手能力在理论和实践的基础上进一步巩固数据结构课程学习的内容掌握工程化软件设计的基本方法2掌握图的创建和应用3…

-

课程设计报告

中国计量学院信息工程学院课程设计报告课程设计名称系统设计与仿真课程计二级学院信息工程学院专业班级10电信2班学姓成绩号名10003…

-

课程设计报告模板

信息科学与工程学院高级语言程序设计课程设计报告学生成绩管理系统学科专业计算机科学与技术班级1301学号指导教师唐郑熠讲师学生二零年…

-

课程设计报告

扬州大学数据结构课程设计报告课题名称姓名学院系科班级指导老师日期自来水管架设问题广陵学院陈宏建1一课程设计的题目自来水管理架设问题…

-

小班班务总结

伴随着夏日气息的来临,我们将结束这个学期的学习,为小班的活动画上圆满的句号。和孩子们朝夕相处的每一分钟都是那么快乐,犹记得孩子哭哭…

-

房地产公司工程部年终总结

工作总结每年的这个时候,公司都要组织一次职工的个人年度述职报告,作为公司工程建设的核心职能部门的一员,要牢记公司领导的教诲和嘱托,…

-

四年级中队工作总结

本学期,我担任四年级一班中队辅导员工作。在学校领导的支持下,在政教处的配合下,我顺利地完成了学校布置的各项任务。在从事德育教学过程…

-

总经理年度工作总结

这是我见过的最好的总经理年度工作总结,是我们头儿写的,以前在其他公司工作也看过、听过不少工作总结,但我认为我们头儿这次写的工作总结…

-

管理学院“学习郭明义,践行雷锋精神”主题团课总结

“学习郭明义践行雷锋精神”主题团课总结管理学院20xx年x月x日“学习郭明义,践行雷锋精神”主题团课总结一、活动背景:19xx年x…