数字电子技术课程设计报告

北京工商大学

《数字电子技术》课程设计报告

学 院: 计算机与信息工程学院

专 业: 自动化

学 生 姓 名: 乔灵芝

学 号: 0904010317

课程设计题目: 数字电子钟及万年历设计

设 计 时 间: 2012/1/2至2012/1/6

一、设计目的

1、熟悉集成电路的引脚安排

2、掌握芯片的逻辑功能及使用方法

3、了解数字电子钟及万年历的组成及工作原理

4、熟悉数字电子钟及万年历的设计与制作

5、熟悉multisim电子电路设计及仿真软件的应用

二、设计思路

1、设计60进制秒计数器

2、设计24进制时计数器

3、设计31进制天计数器

4、设计12机制月计数器

5、设计7进制周计数器

6、设计闰年平年不同月份不同进制逻辑电路

7、设计调整时间电路

三、设计过程

1、60进制计数器

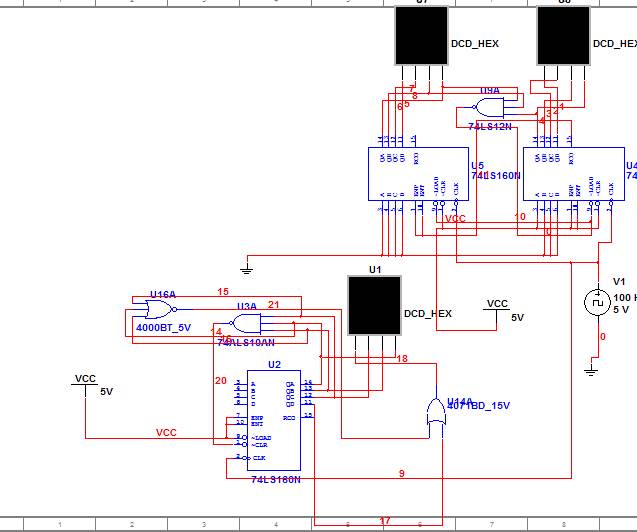

“秒”、“分”电路都六十进制,它由一级十进制计数器和一级六进制计数器组成,六十进制计数器的设计如图1,采用两片74ls161串联而成,低位芯片的抚慰信号作为下级输入信号,串接起来构成“秒”、“分”计数器

2、二十四进制计数器

24进制计数器的设计如图2,时计数电路由两片74ls161串联组成。当时个位计数为4,十位计数为2时,两片74ls161复零,从而构成24进制计数。

3、天计数器及周计数器

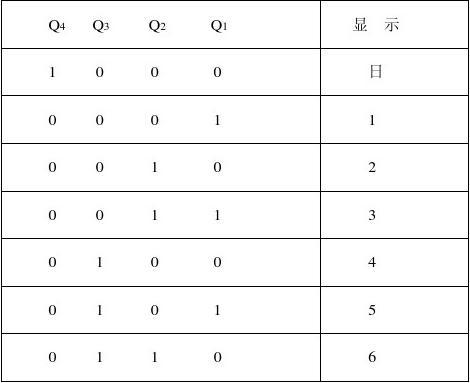

均采用74ls160芯片串联而成,基本原理同上,其中将周计数器0通过逻辑函数改变为8 ,则在显示端输出为周1到周日

12进制月计数器也采用74ls160芯片串联而成原理同上,电路设计图如下:

4、调时电路

调试电路采用两个开关串联,第一个开关为统一控制开关,闭合则电路开始工作,打开则可进行调整时间。第二个开关一段接高电平1,另一端接地,按下时则输出一个高电平,松开则变为低电平,期间产生一个下降沿,是为调整信号,每一个芯片都有独立开关,独立调整电路,可以很快捷。

加了调整电路的始终电路如下:

5、闰年平年各月份不同进制逻辑控制电路设计

通过二与门,三与门,将28日,29日,30日,31日的特征信号输出;特征信号引入数据选择器,由地址信号进行选择,然后接回控制日期的160芯片。数据选择器的A、B信号由“月”的特征信号及”闰年”的特征信号,通过逻辑电路给出,通过不同信号选择不通进制。如下:

而闰年信号通过再加一个四进制计数器,平年输出信号为0,闰年输出信号为1,另其与月份信号够成选择信号,实现各进制的转换。

加入调整电路的整体电路如下:

六、设计体会

通过Multisim软件,可以很方便的实现计算机仿真和虚拟实验,与传统的实验方法相比,通过Multisim仿真可实现设计与实验可以同步进行,且修改电路容易,连线直观。缺点是仿真中的虚拟实验的“时间”受仿真速度的影响,要比现实中的“时间”慢很多,因此实验中所用的“秒”脉冲信号是用交流电压源,其频率接近1khz,仿真速度才相当于现实生活中的秒。

整个过程花了我不少时间,主要是在调试时花了不少时间,其间换了不少器件,查了很多资料,有的器件在理论上可行,但在实际运行中就无法看到效果,所以调试花了我不少时间,有时无法找出错误便更换器件重新接线以使电路正常运行。Multisim软件有时会出问题,在理论上可行的电路在调试中未必能显示出来,这就需要不断地尝试才能得出正确的答案。

在实际的操作过程中,能把理论中所学的知识灵活地运用起来,并在调试中会遇到各种各样的问题,电路的调试提高了我们解决问题的能力,学会了在设计中独立解决问题,也包括怎样去查找问题。似乎所有的事都得自己新手去操作才会在脑海中留下深刻的印象,这个小小的课程设计让我可以熟练的操作Multisim软件,也了解了不少器件的功能的应用,也加深了对数字电路认识和理解。

整个过程都是我独立完成的,感觉很难尤其是较时功能的实现,费了很长时间,但收获不小,发现调试的过程并不是想象中的那样简单,需要耐心、仔细地分析和解决问题,可以让我的性格更加沉稳。这样的课程设计很能培养我们的能力,让我们不再局限于书本上的知识。

第二篇:数字电子技术课程设计报告——电子钟设计

数字电子技术课程设计报告

课 题:数字钟的设计与制作

学 年:09学年 学 期: 第二学期 专 业:

班 级:

姓 名:

时 间:20xx年6月20日—20xx年6月26日

数字电子技术课程设计报告

一、设计目的

数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。 数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。 因此,我们此次设计与制作数字钟就是为了了解数字钟的原理,从而学会制作数字钟.而且通过数字钟的制作进一步的了解各种在制作中用到的中小规模集成电路的作用及实用方法.且由于数字钟包括组合逻辑电路和时叙电路.通过它可以进一步学习与掌握各种组合逻辑电路与时序电路的原理与使用方法.

二、设计内容及要求

(1)设计指标

① 由晶振电路产生1HZ标准秒信号;

② 分、秒为00~59六十进制计数器;

③ 时为00~23二十四进制计数器;

④ 周显示从1~日为七进制计数器;

⑤ 具有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间; ⑥ 整点具有报时功能,当时间到达整点前鸣叫五次低音(500HZ),整点时再鸣叫一次高音(1000HZ)。

(2)设计要求

① 画出电路原理图(或仿真电路图);

② 元器件及参数选择;

③ 电路仿真与调试。

(3)制作要求 自行装配和调试,并能发现问题和解决问题。

(4)编写设计报告 写出设计与制作的全过程,附上有关资料和图纸,有心得体会。

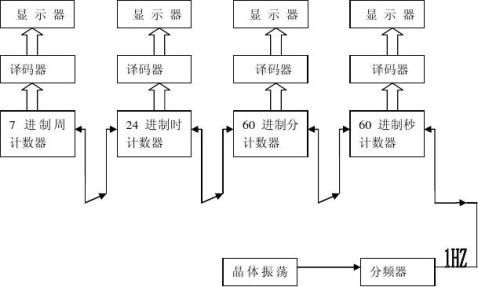

三、原理框图

数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ时间信号必须做到准确稳定。通常使用石英晶体振荡器电路构成数字钟。数字电子钟的总体图如图(1)所示。由图(1)可见,数字电子钟由以下几部分组成:石英晶体振荡器和分频器组成的秒脉冲发生器;校对电路;六十进制秒、分计数器、二十进制时计数器及七十进制日计数器;以及秒、分、时的译码显示部分等。

四、主要部分的实现方案

1 秒脉冲电路

由晶振32768Hz经 CD4060分频为2Hz,再经过74LS74一次分频,即得1Hz 标准秒脉冲,提供给时钟计数脉冲。如图示:

20pF 74LS74

10 Q 1Hz

CD4060 Q14 C1

3—20pF 1D

11 R

32768Hz 22MΩ 12

2 时间计数器电路

由6个74LS90 计数器组成时分秒的计数电路,74LS90 是4位二进制同步加计数器,它的设置为多片集成计数器的级联提供方便。它具有异步清零,同步并行预置数,保持和计数的功能。

(1)秒计数器

秒的个位计数单元为10进制计数器,当QDQCQBQA变成1010时,通过与非门把它的清零端变成0,计数器的输出被置零,跳过1011到1111的状态,又从0000开始,如此重复。秒的十为计数单元为6进制,当QDQCQBQA变成0101时,通过与非门把它的清零端变成0,计数器的输出被置零,跳过0110到1111的状态,又从0000开始,如此就是60进制。同时秒十位上的0101时,要把进位信号传输给“分”个位的计数单元。

(2)分计数器

分的个位和十位计数单元的状态转换和秒的是一样的,只是它要把进位信号传输给时的个位计数单元。 秒脉冲发生器

(3)时计数器

当“时”十位的QDQCQBQA为0000或0001时,“时”的个位计数单元是十进制计数器,当他的QDQCQBQA到1010时,通过与非门使得个位74LS90上的清零端为0,则计数器的输出直接置零,从0000有开始。当十位的QDQCQBQA为0010时,通过与非门使得该74LS90的清零端为0,“时”的十位有重新从0000开始,此时的个位计数单元变成4进制,即当个位计数单元的QDQCQBQA为0100时,就要又从0000开始计数。这样就实现了“时”24进制的计数

( 4 ) 日计数器

日计数器由两个74LS74,四个TTL 和一个 74LS20 构成,实现了七定制的功能。每个74LS74控制一个输入,即控制QDQCQBQA中的一个。当从0000到0111 时,显示是按照74LS74集成们电路的逻辑功能来实现的,当为0111的时候,QCQBQA各为1 1 1 ,他们三个通过74LS74 与非门输出为0 。再与QD 所控的0 通过 TTL集成门电路输出了0 ,如此循环,使得四个TTL 输出都为 0000。即使得输出变为了“置零”状态。从而实现了七禁止循环。如下图所示:

3 数字钟的译码及显示单元电路

译码显示采用共阳极LED八段数码管和译码器74SL247组成。

4.整点报时电路

电路应在整点前10秒钟内开始整点报时,即当时间在59分54秒到59分59秒期间时,报时电路报时控制信号。

当时间在59分50秒到59分59秒期间时,分十位、分个位和秒十位均保持不变,分别为5、9和5,因此可将分计数器十位的QC和QA 、个位的QD和QA及秒计数器十位的QC和QA相与,从而产生报时控制信号。

报时电路由74LS08高音和74LS04低音通过74LS32来构成。

五、实验过程中遇到的问题及解决方法

大部分的线路都连完了之后,我们用干电池进行了试验,结果发现数码管不发光。于是重新检查电路,发现有几处的地线与地线、电源线与电源线之间没有连接,连上后数码管可以正常发光。但是问题接踵而至,数字不会变动,即没有起振。检查晶振等原件及附近电路,未发现问题。再检查74LS90的接线,发现管脚多处未接地,接上后数字开始跳动。秒的显示正常,但是不进位,经过检查发现是某一根线接错了,改正后进位正常。时、分、秒的显示都正常后,日的显示又出现了问题。在欧阳同学反复检查与试验之下,终于发现了错误的根源。纠正了接错的导线之后,终于,数字钟可以正常显示时间。

当遇到蜂鸣器不能在要求的时间上发声时,我们请教了部分已经完成设计的同学,了解到了一些可能的原因,对这些可能一一试验,究其根本,并最终解决了问题,达到了预期的目标。

六、心得体会

通过这次对数字钟的设计与制作,让我们了解了设计电路的程序,也让我们了解了数字钟的原理和设计理念。要设计一个电路总要对着一个参考电路图才可以连接,但是最后的成品却不一定与想象的完全一样,因为在事迹接线中有着各种各样的条件制约,所以要合理布局这样连出来的成品才比较美观。设计过程中,在一次又一次的失败面前,我们没有退缩,而是勇敢的去面对,积极的去解决,充分运用所学知识和他人的帮助,最终取得了成功。通过亲自动手连线,试验,遇到问题,解决问题,我们巩固了书本的知识,同时也学到了新的学问,明白了实践的可贵性。动手能力的提高,细心与耐心的培养,品尝自己劳动成果的喜悦,是我们在这次课程设计中最大的收获。

七、元器件

1.四连面包板1块

2.镊子1把

3.剪刀1把

4.共阳八段数码管7个

5.导线若干

6.74LS90 集成块6块

7.CD4060集成块1块

8.74LS247集成块7块

9.74LS20 集成块1块

10.74LS00 集成块1块

11.74LS08集成块2块

12.74LS32 集成块 1块

13.74LS04 集成块 1块

14 74LS74 集成块 4块

15.32.768k时钟晶体1个

16.22pF和20pF可调电容各一个

17.三极管8050一个

18.300Ω7个 22MΩ一个 1KΩ一个

八、参考资料及文献 参考资料:

《电子技术基础(数字部分)(第四版)》 《电路及电子技术实验》

《电工电子技术实践教材》

10KΩ一个

-

数字电子技术课程设计报告

吉林建筑大学电气与电子信息工程学院数字电子技术课程设计报告设计题目:数字钟的电路设计专业班级:电气112班学生姓名:学号:指导教师…

-

数字电子技术课程设计报告(数字钟)

目录一设计目的1二实现功能1三制作过程1四原理框图341数字钟构成342设计脉冲源443设计整形电路544设计分频器545实际计数…

-

数 字 电 路 课 程 设 计 报 告

数字电路课程设计报告课题名称:篮球竞赛30秒计时器姓名:学号:专业班级:通信工程1指导教师:设计日期:20##年1月5日摘要:随着…

-

数字电路课程设计电子钟设计报告[1]

数字电路课程设计总结报告题目数字钟设计专业班级学生姓名学号指导教师20xx年12月15日目录一设计任务设计课题功能要求二设计框图及…

-

数字电子技术课程设计报告(样例)

大庆师范学院数字电子技术课程设计报告设计课题基于VHDL自动售货姓名杨浩北学院物电学院专业电子信息工程班级08级2班学号20xx0…

-

数电课程设计心得体会

课程设计刚开始,拿着选定的题目不知如何入手。毕竟课程设计不同于实验课,电路图和程序都要自己设计。静下心来,仔细分析题目,再加上指导…

-

数字电子技术课程设计总结

数字电子技术课程设计总结指导教师王新旺课程设计地点电子创新技术实验室课程设计时间8天课程设计班级电子信息工程1001班课程设计时间…

-

数字电子技术课程设计实习报告

长沙学院数电课程设计说明书题系部目电子节拍器设计电子与通信工程系专业班级电气2班姓学指起名号导止教日师期李凯20xx032121陈…

-

数字电子技术课程设计报告(样例)

大庆师范学院数字电子技术课程设计报告设计课题基于VHDL自动售货姓名杨浩北学院物电学院专业电子信息工程班级08级2班学号20xx0…

-

数字电子技术课程设计报告

课程设计课程名称数字电子技术课程设计题目名称四人智力竞赛抢答器学生学院专业班级学号学生姓名指导教师200年月日1目录一设计题目3二…