设计验证计划实施流程

设计验证计划实施流程

流程更新记录

1. 控制目标

此流程规范公司开发新产品时的设计验证计划的实施、实施的过程和结果的记录,旨在明确相关部门和相应人员的职责权限。

2. 适用范围

此流程适用于实施设计验证计划。

3. 流程责任人

技术中心主任负责本文件的有效性。

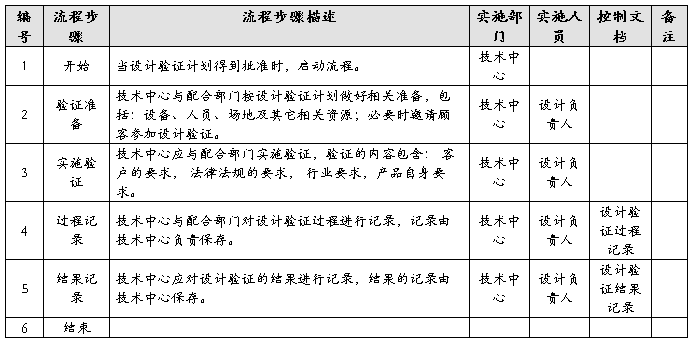

4.设计验证计划实施流程图

5. 流程说明

第二篇:芯片设计的验证技术和验证流程研究

浙江大学

硕士学位论文

芯片设计的验证技术和验证流程研究

姓名:梁骏

申请学位级别:硕士

专业:通信与信息系统

指导教师:张明

20040201

潺汪大学撩l:学位论文YS81455

摘要

在芯,{‘设计规模F1盏增大,芯片应用越来麒f’‘泛的今天,保{正设计的正确性是每…位芯片设计者必须考虑的大事。本文对芯片设计特别是ASlC领域的验证技零鞠豢.羲答理进嚣了搽讨,款验涯理论,骏诞实黢,验诞鑫凌纯,验涯重焉帮验证管理等处着眼,研究如何通过验证技术的应用和验证流程的合理化实现高效率验证,提高芯片设计的质量。

本文考察了动态验证技术和静态验证技术的最新发展,并积累了实践应用经验。动态骏{正技术是验证懿蒸礁,在今焉戆验毯浚程中也将继续扮浚熏要懿怒色。静惑骏证技术在近几年国有蓿飞速的发震。静态验证技零可以克服芯片规模增大时动态验证时间耗费巨大的缺点。本文尝试将动态验证技术与静态验证技术结合应用予芯片的验证工作。

本文还结合FPGA懿应用深入研究了验诞技术的另一发展方向——硬件仿真按拳。逶过穆理模墅将较释模亨鼙的糇序魏嚣受为硬{孛鹃著嚣藏{亍,仿真技术可以将动态验证的速度提高2副3个数量级,消除速度瓶颈。但是仿真技术在现阶段还有速度,规模,接口方丽的技术问题有待提高。

奉文提出通过验证语滔丽不是硬件描述语畜来建立验证环境,帮助验证工程爨褥列’淹与蘧力集中在验证愚怒豹表达上瑟不楚霹验{歪实瑷缡节熬表达上。传睫着骚证技术只益专业化,离级验证语言开始靛挥自己的贡献。高缀验证语言的普及与使用必将提高芯片骏诞的效率与质量。

提简芯片设计质量的关键一是先进的验证技术,二是科学的验酲管理。

本文在验证理论的磷究秘实践的基础』二,对验证团酞的建立,培莽与管理进{亍了攘索,提舞班验{=丕猿立纯靛壤囊帮全瑟骚潦管理懿蕊点螽譬验诞工{乍。验证独立化是芯片设计规模发展后的必然需要。通过分工,验证以其独立的视角为设计提供有力保障。验证独立化也为验证的质徽锗理提供基础。通过提高验证流程的矮墩束保证验证的质羹怒全面质量管理的核心思想。

数字毒鼙菝蜃延理芯片楚最有枣场嚣发侩您灏数字电褪孩心蕊冀之一一。该瑷嚣有指导地应用本文研究酮验证理论与方法,建立独立的验证组织,采用科学的验证流穰,实施全面质量管理,有力地保障了项目的高质量完成a

关键词:芯片,设计,黢证,流程,ASIC

1寒爨露嚣、萼§》霪塞匆垒文公衣

Abstract

Todaylarge’scalechipsleadtogreatlostdue

should

be

taken

tothe

are

usedwildlyIt'salwaysreportedthatbugsofchips

correctnessofeachchip

inefficiencyofverification.The

first

consideration

intothe

Appling

modem

verification

technologiesandreformattingverificationflowwillcapturemorebugs,whichwill

raisequalityofchipdesigns.Thisdissertationfocuses

on

theverification

technology

andqualitymanagementinchipdesignsespeciallyinASICdesigns

Verificationtechnologies

are

catalogedintodynamicverification

technology,

run

whichmust

run

DUV,andstaticverification

stone

technology,which

needn’tDUV.

as

an

Dynamicverification,stand

ofverificarlon,will

continueacting

importantroleduringtheverificationflowinthefuture.Withtherapiddevelopment

recentyears

thestaticverification

one

can

can

offerrelativefasterspeedandshortertime

thandynamicdointhegrowingfieldoflargescalechip.Thedynamic

on

verificationandthestaticverificationwilldependverificationfield.

eachotherinthecoining

Anotherfocusforverificationtechnologyishardware

an

technology.By

building

phy7sicalmoduleofDUV

to

rumthesequentialexecutionofsoftwaresimulation

canrun

into

on

consequential

executionofhardwareemulation,emulationtechnology

100to1000timesspeedthansimulationtechnologydoes,which

erase

the

bottleneckofsimulationtechnology.Buttherestillaresometechnologyproblems

such

as

maxspeed,scale,andinterfacetosoftware,foremulation

technology

to

0Vercome

Advancedverificationlanguagesstarttomaketheircontributiontodaywhentheverificationtechnologyhasbeen

powerful

a

specializeone.Verification

engineers.They

one

languagesoffer

focus

on

languageplatform

forverification

can

the

expressionofverificationthoughtotherthantheverification

oflanguagedetailsbyusing

languages

to

languages

otherthanhardware

use

description

build

verificationenviromnent

Thewildly

ofverificationlanguageswillraisethe

efficiencyandqualityofdesignverification

Onekeytoguaranteedesignqualityisdevelopingverificationtechnologies,anotherimportant

Based

obeyedononeisscientificqualitymanagement.theorystudyandpractice,theindividualverificationprincipleiswholebytheindustry.Theindividualverificationisnecessaryforverificationtakesdifferentviewpointsandtools.Andtheindividualverificationmakesqualitymanagementmorepossible.Totalqualitymanagementactsastrafficrulesindesignflow.Thekernelofqualitymanagementistoguaranteetheproductqualitybyguaranteeingtheproductflowquality.

Duringthedigitalvideopost-processingprojeetadaptingscientificverificationflowweapplyverificationtheoryandskills,whichmakessatisfiedqualityofdesign.Keywords:chip,deNgn,verification,flow,ASIC

第1章验证的重要性

本章回顾了集成电路的飞速发展,针对芯片设训的瓶颈提m了验证的重要性和验证的独立性原则。

§1.1

IC(IntegratedIC制造业的发展Circuit)的发展F]新月异:1962年制造出包含12个晶体管的小规模集成电路SSI(Small.ScaleIntegration);1966年发展到集成度为100--1000个晶体管的中规模集成电路MSI(Medium—ScaleIntegration);1967—1973年,研制出1000个至lo万个晶体管的大规模集成电路LSI(Large—ScaleIntegration);1977年研制出在30平方毫米的硅晶片上集成15万个晶体管的超大规模集成电路VLSI(VeryLarge.ScaleIntegration),这是电子技术的第四次重大突破,从此真正迈入了微电子时代;1993年随着集成了1000万个晶体管的16MFLASH和256MDRAM的研制成功,进入了特大规模集成电路ULSI(UltraLarge—ScaleIntegration)代;1994年随着集成了1亿个元件的1GDRAM的研

Scale制成功,进入了巨大规模集成电路GSI(GigaIntegration)时代。

II"aDSI斑ors

l、cIdie

、c、1I

幽表1Intel处理器与DRAM的发展

图1提供了作为芯片设计坐标的Intel处理器和DRAM芯片的发展历程。IC产l诮集成度不断提升的最佳写照是摩尔定律,即所谓每18个月,相同面积大小

的芯片内,品体管数量会增长一倍的规则。

在Ic产品集成度的提高依赖于IC制造技术的飞速发展。IC产品的特征尺iJ越来越小。Ic产品的特征尺、J平均在25年I内缩小到原来的一半。随着芯片制造业的发展,j艺=片设计工程师可以进行越来越复杂的设计。当人们可以利用超过1000M门的资源进行SOC(SystemOnChip)的设计来创造新世界时,当芯片上的资源不再是对创造力的限制时,芯片设计的成功率却限制了设计规模的急剧扩大。现在单个芯片所能提供的晶体管数量已经超过了大多数电子系统的需求,如何去发挥这些几乎无限的计算能力就变成了一项重大的挑战。验证技术成为应对这个挑战的关键㈣。

§1.2验证的必要性

1.2.1缺陷的代价

现代生活丰富多彩。各种娱乐产品,如电视,DV,数码相机等,点缀了闲暇生活:各种交流工具,如电话,手机,互联网等,将世界缩小;尖端科技,如火箭,卫星,飞船等,探索未来。芯片在其中扮演着不可或缺的角色。没有芯片,世界将黯然失色。然而一块有缺陷的芯片造成的损失可能比没有芯片还要糟糕。

验证的重要性已经被业界的一次次bug造成的重大损失所证明。英特尔的浮点危机就是一例。1994年底,英特尔面临着一个危机,一个数学教授在研究’些复杂的数学运算时,机器出现了除法错误。英特尔对此的解释是,这是由于芯片的设计上有一个小错误,使计算机在90亿次除法运算中会出现一次错误。一个月之后,IBM宣布停止将装有奔腾芯片的计算机出厂。最终英特尔不得不免费为所有用户更换所有问题芯片,这场风波终于平息下来了。这个没有验证出来的缺陷的价值近5亿美元。

From30%一40%lo50%一80%

1996

390KGalescodeVerifv。Synth30-40‘P&R

2000

1MSOC50-{code汶≮\\1SynthP&RVerily

图表2验证工作的开销变化

随着设计规模的增大,验证上作的丌销越来越大。从统计资料中可咀发现1996年的30万门的j卷片设计中验证工作在整个项目中占据了30--40%的时间与资源,到了2000年100万门的芯片设计中验证工作在整个项目中占据了50一80%的B,l-rnj与资源【1,3,14]。

验证的技术和验证的管理包含以下两个重要方面:一是利用先进的工具与方法得到设计在某一较高概率下的工作可靠性保证。:二是对验证的资源进行合理分配,验证的流程进行优化,最终达到验证工作的有效性的保证。其一是对设计质量的度量的过程,其二是对设计质量的度量的过程的质量保证。验证技术与验证管理这对孪生子对ASIC的成功起到保驾护航的作用。验证的效率和彻底性能够缩短上市时间,减少大型复杂ASIC设计重新流片的次数。

根据DeepChip日前的报告,61%的集成电路设计及ASIC需要重新设计并返回到晶圆厂,至少需要一次重新流片。失败原因统计数据分别如下:功能逻辑错误43%、模拟调整(AnalogTuning)20%、信号完整性问题17%、时钟电路错误14%、可靠性问题12%、混合信号问题l1%、使用过高功率ll%、路径速度过慢10%、路径速度过快10%、IR压降问题7%、固件错误4%和其它问题3%。3

图表3流片失败原因统计

矸:仅提高验证水平可以保证避免重新流片的投资风险,高质量的验证可以

保证提交个用户的芯片隐含着尽可能少的缺陷。

图4指出了Ic复杂度的提高与设计生产率的提高之间的鸿沟。这道鸿沟还随着时间不断地增大。提高Ic的成功率可以大大缩小这道鸿沟。在Ic重新流片的原因统计中可以看出主要障碍是占43%之多的功能逻辑错误。通过提高验

证技术与质量管理水平可以大大减少功能逻辑错误的可能性,提高IC设计的生

产率[34,36】。

ProductivityGap

0

1

/

58%Nr.Comblexitv。,——‘..--

growth

100∞O

10.000

000

E

000王

咖㈣Ⅲ伯,

啪咖姗姗啪Ⅲ”,

./’

rateI。/一一

I.∞o

000

甍

,’,f

一芏屯一£~价一∞行卜一口。一

一,.叫粥:甭■~

growthrate

l

100,000.0,310、000

尝

霉

.=

÷二j哼’≮Productivity

1998

1∞a

100

】.1I..III._.IIt_.I。.1.I

2003

I__l

ChipCapacityandDesignerProductivity

图表4ic复杂度与设计生产率

4

1.2.2』托生缺陷的原因

划芯片设训的缺陷进行分析,可以发现缺陷产生有以F各种各样的原因:1.交流不够、交流上有误解或者根木不进行交流

在应用应该做什么或不应该做什么的细节(应用的需求)不清晰的情况下进行丌发。

2.设计的复杂性

庞人的系统规模,使得系统的复杂性呈指数增长,没有Ic丌发经验的人很难理解它。

3.程序设计错误

向所有的人一样,设计工程师也会出错。

4.需求变化

需求变化的影响是多方面的,客户可能不了解需求变化带来的影响.也可能知道但又不得不那么做。需求变化的后果可能是造成系统的重新设计,设计人员的日程的重新安排,已经完成的工作可能要重做或者完全抛弃,对其他项目产:生影响,硬件需求可能要因此改变,等等。如果有许多小的改变或者一次犬的变化,项目各部分之间己知或未知的依赖性可能会相互影响而导致更多问题的出现,需求改变带来的复杂性可能导致错误,还可能影响工程参与者的积极性。

5.时间压力

项目的同程表很难做到准确,很多时候需要预计和猜测。当最终期限迫近和关键时刻到来之际,错误也就跟着来了。

6.代码文档贫乏

贫乏或者差劲的文档使得代码维护和修改变的异常艰辛,其结果是带来许多错误。

由丁-以上的原冈,通常无法避免产生错误,但是通过有效的验证手段和科学的管理,可以m没计过群中找到错误与缺陷,保iE产品质鼙,避免花贫巨人的重新流片等损火。5

§1.3验证工作的独立性原则

由于验证工作的特殊性需要实现独立验证原则来保证验证的质量。人类的活动具有高度的目的性,建立适当的目标具有重要的心理作用。如果目的是要证明程序巾没有错误,那么就会不自觉地朝这个方向去做;也就是说,会倾向于挑选那些使程序出错的可能性较小的测试数据。另一方面,如果目标是要证明程序中有错,那就会选择一些易于发现程序所含错误的测试数据。而后一种态度会比前者给程序增添更多的价值洲。

1.3.1代码设计开发者应避免验证自己的代码

开发者被指定测试自己的代码是一件很糟糕的事。开发和测试生来就是不同的活动。开发是创造或者建立什么东西的行为,一个模块或者整个系统。而测试的唯一目的是证明一个模块或者系统工作不正常。这两个活动之间有着本质的矛盾。一一个人不太可能把两个截然对立的角色都扮演的很好。基于这个想法,应该限制开发者在测试中的参与。他们比较合适的任务是进行有可能的最低层的测试一一单元测试。当一个程序员在完成了设计,编写程序的建设性工作后,要一夜之间突然改变他的观点,设法对程序形成一个完全否定的态度,那是非常困难的。大部分设计工程师都由于不能使自己进入必要的精神状态(不是抱着要揭露出自己设计中错误的态度),因而不能有效地测试自己的设计。

除了这个心理学问题之外,还有一个重要的问题:设计中可能包含由于设计工程师对问题的叙述或说明的误解而产生的错误。如果是这种情况,当设计工程师测试自己的设计时,往往还会带着同样的误解致使问题难以发现。

再者,可以把测试看作是对一篇论文或书做校对,或与写评论相类似的工作。正如许多作者所知,校对或批评自己的著作是非常困难的。也就是说,在自己的工作中找出缺陷往往是人的心理状态所不容的。

硬件设计与验证需要不同的技术和思想。硬件设计关注与满足系统性能要求,着眼与对设计的优化,对代码风格的追求。验证关注与目标是否被实现。验证工程师需要对代码有强烈的怀疑态度。验证工程师更是软件工程师,他们没宵可综合的约束,可以自由地选择实现方法,更需要创造力。

以上看法并不意味着没计工程师不可能测试自己的设计I。不过相比之下如6

果山另外一些人来进行设计测试,就会更有效、更成功。

1.3.2代码设计机构应避免验证自己的代码

在许多意义上来蜕,一项工程或一个设计机构是个有生命的有机体,它同样有心理学问题。再者,在大多数情况下,人们部是以在给定同期内,以一定代价编制程序的能力求衡量程序设计机构和项目管理人员的。这样做的一个理由是时IN.,Tfl成本指标便于衡量,而程序的可靠性却很难度量。要程序设计机构在测试自己的程序时保持客观的态度是困难的,因为如果用正确的定义看待测试,就不大可能按预定计划完成测试也不大可能把耗费的代价限制在要求的范围以内。

验证是对设计的保证。在小规模设计时代,设计工程师可以对自己的设计进行充分的验证。随着芯片规模的急剧扩大,验证需要与设计不同的技术与思考方式。芯片验证的工作的发展需要独立的验证组织与验证方法论。

§1.4本文主要工作和章节安排

本文主要工作可分为下面方面:

本文归纳总结了大规模芯片设计特别是ASIC设计中的现代验证技术的发展与应用,对芯片设计过程中的验证管理技术进行有益的探讨,在数字视频后处理项目的实践中提出并实现了结合质量管理的芯片验证技术与流程,以期解决“验证危机”对芯片设计的阻碍。

数字视频后处理项目将最新的验证技术应用在工作中,并根据工作中的实际效果进行对验证流程的合理化,形成了比较科学的验证流程,有力地保障了芯片设计工作。

di文的章节安排如下:

第一章芯片设计中验证的重要意义与验证的独立性原Ⅲ

第:章验证过程中使H{的技术:7

浙7rJ、学坝I.学位论文

第i章验证过程叶]的质量管理:

第四章验证重用的重要意义与方法及其实践;

第五章数字视频后处理项目巾的验证技术与流程的实现

第六章全文的总结。8

第2章验证流程与技术

本章对验证过程进行舞定帮分类,讨论了传统的基于模拟婚动态验证技术,结合ASIC援模抉速增长静趋势,改遗传统骚涯流程,缮加静态验证在验证过平犟中的地位与作用。

§2』验证的范围

匿F领蓼]0磊rH茅一1L~,。..—,。,JL—,,,,,,,,,,一L——一、..,—,————ji.......................................j

图麓5芯片设计的抽象层次

j誊片设计可以按照蕻擞述语言的抽象鼷次分成算法级描述,弦为级描述,RTL(RegisterTransferLevel)缓摇透手鬟瓣袭级攒述。在一个熬囊懿蜜上嚣下(Top.Down)的设计中,设计的起点是一个缒功能描述的算法级功能模型。这个功能描述模型是完全幽软件实现的,它描述了系统所要实现的具体功能。这个功能模型既没有结构划分,也没有时序关系,完全是串行的功能描述。一个模块麴行为级模型是对该模块的算法黥描述。与缝软传的程序不弱斡是,行为缀横型中输入输出的孳亍为是基于时镑静。RTL模型是在设诗中摇述了寄存器,并在寄存器之间加入组合逻辑。基于此,系统功能的实现就要依赖与有限状态机(FSM)和数据通路(datapath)。寄存器值的更新是在时钟边沿发生的,在RTL的描述中,无论燕猩接口还是在内部,都是基于时钟的。艇谓基于时钟的禽义是:莰诗必颈涛楚鹣绘窭系统奁每个时耱到来时爨应该发生豹行为。在雩亍为级中,只是输入输盘才与时钟有着严格的关系。网表级摇述由标准单元门构成。网表级描述通常有综合器对RTL级描述进行综合所得。图6是ASIC设训’的撼个流程。验证覆盏赣从系统规划到提交GDSII网表之问的所有过程。其中最蕊襄懿盘是难度最大憨工{管是对HDL{弋鼹黪功能验证。9

Design

/。。?一一一~、、-SynthesysManu%Cture7。,,’’’一一~、、、t//’’’’~~-l

SPEC●HDLO’、一~——一一一一一/I~~一一一一一一一7+。'、~~——一一一一一一7Testbench

Ecqhueicvaki]negn。。FT●6aLes●

图表6验证的范围

§2.2验证技术的分类

验证技术可以按照以下不同的角度进行分类。

从是否需要执行被验证设计(DUV,designunderverification)的角度,验证的技术可以分为动态验证和静态验证两大类。动态验证是指使用软件或硬件对设计的行为进行模拟和评估,其核心是对时间序列的模拟,所以必须要有验证矢量序列来驱动DUV。静态验证则相反,它不需要时间序列的概念,而是通过数学的等效性计算完成验证的功能。静态验证技术由于不需要建立验证矢量序列和验证环境,在设计规模增大的时候显示出了越来越强的活力。静态验证技术包括静态检查,形式验证和静态时序分析三大类。

按照验证的目的可以将验证分为意图测试,压力测试,回归测试等几类:意图测试是指将设计运行在『F常模式下完成正常功能的测试。意图测试占据验证工作的大部分工作。任何规格书中标注的设计功能都要经过意图测试。

压力测试是指将设计运行在极端负荷情况下,考验设计的处理能力的测试。比如将FIFO(FirstInFirstOut)运行在满的情况下,同时写入读出。将总线运行在高负荷下也是压力测试的一例。

回归测试是指运行以保证已经验证的问题不会再现的测试。在测试阶段通常会发现缺陷,然后设计工程师对被发现的缺陷进行修改。然而在修改新发现的缺陷时可能导入新的缺陷,或者从新激活原来的缺陷。回归测试的把关可以保证设计的修改不会导致原来的缺陷被激活。但是在实践中回归测试可能被轻视。设计工程师对自己的自信,对修改缺陷的工作的轻视都有可能使得被修改的设计跳过回归测试,特别是当设计1:程师测试A己的设计时。

办法是通过验证工程师的严格把关,杜绝川归测试逃逸现象。个好的解决

浙江人学坝I.学位论义

§2.3动态验证

动态验证包括模拟(simulation)验证与仿真(emulation)验证两大类。模拟技术通过计算机软件对硬件漫计的行为进行某种程度的近似和简化,模拟出硬件的应有的行为,并x,H7为进行评估。仿真则是通过硬件平台划‘没计进行近似。由于硬件运行的并行性的速度远远大于软件串行的模拟速度,通常仿真会比模拟快2到3个数量级。但是软件与硬件的交互障碍等同难限制了仿真的应用。

模拟验证时根据对DUV内部数据的可观察性和可控制性的程度可以将其分为臼盒子测试,黑盒子测试和灰盒子测试技术三大类。

2.3.1白盒子测试

白盒子测试也称结构测试或逻辑驱动测试,它是知道设计内部工作过程,可通过测试来检测设计内部动作是否按照规格说明书的规定正常进行,按照设计内部的结构测试设计,检验设计中的每条通路是否都有能按预定要求正确工作,而不顾它的功能。白盒子测试的主要方法有逻辑驱动、基本路径测试等。

白盒子测试用例设计包括:

1逻辑覆盖,以HDL程序内在逻辑结构为基础的测试,包括以下5种类型:1.1语句覆盖:每一条可执行语句至少覆盖一次;

12判定覆盖(分支覆盖):设计若干个测试用例,运行所测程序,使程序中每个判断的取真分支和取假分支至少执行一次;

1.3条件覆盖:设计足够多的测试用例,运行所测程序,使程序中每个判断的每个条件的每个可能取值至少执行一次:

1.4判定.条件覆盖:设计足够多的测试用例,运行所测程序,使程序中每个判断的每个条件的所有可能取值至少执行一次,并且每个可能的判断结果也至少执行一次:

l5条件组合测试:设计足够多的测试用例,运行所测程序,使程序中每个判断的所有可能的条件取值至少执行一次:

1.6路径测试:设计足够多的测试用例,运行所测程序,要覆盖程序中所有可能的路径。

2基本路径测试

在程序控制流图的基础上,通过分析控制构造的环路复杂性,导出摹本可执行路径集合,从而设计测试用例。包括以I、.5个方面:

2.1程序的控制流图:描述程序控制流的一种图示方法。

2.2程序环境复杂性:从程序的环路复杂性可导出程序基本路径集合中的独立路径条数,这是确定程序中每个可执行语句至少执行依次所必须的测试用例数目的上界。

2.3导出测试用例

2,4准备测试用例,确保基本路径集中的每~条路径的执行

2.5图形矩阵:是在基本路径测试中起辅助作用的工具,利用它可以实现自动地确定一个基本路径集。

“白盒”法全面了解程序内部逻辑结构、对所有逻辑路径进行测试。“白盒”法是穷举路径测试。在使用这一一方案时,测试者必须检查程序的内部结构,从检查程序的逻辑着手,得出测试数据。贯穿程序的独立路径数是天文数字。但即使每条路径都测试了仍然可能有错误。第一,穷举路径测试决不能查出程序违反了设计规范,即程序本身是个错误的程序。第二,穷举路径测试不可能查出程序中因遗漏路径而出错。第三,穷举路径测试可能发现不了一些与数据相关的错误。

2.3.2黑盒子测试

黑盒测试也称功能测试或数据驱动测试,它是在己知设计所应具有的功能,通过测试来检测每个功能是否都能正常使用,在测试时,把DUV看作一个不能打丌的黑简子,在完全不考虑程序内部结构和内部特性的情况下,测试者在DUV接口进行测试,它只检查DUV功能是否按照需求规格说明书的规定正常使用,程序是否能适当地接收输入数据而产生正确的输出信息,并且保持外部信息的完整性。黑盒测试方法主要有等价类划分、边界值分析、因果图、错误推测等。

黑盒测试用例设计包括:

等价类划分:划分等价类一确立测试闱例一设计用例12

边界值分析:通过分析,考虑如何确立边界情况。边界值分析也是.种黑盒测试方法,适度等价类分析方法的一种补充,由长期的测试工作经验得知,大量的错误是发生在输入或输出的边界上。因此针对各种边界情况设计测试用例,可以查出更多的错误。

选择测试用例的原则:

一、如果输入条件规定了值的范围,则应该取刚达到这个范围的边界值,以及刚刚超过这个范围边界的值作为测试输入数据:

:、如果输入条件规定了值的个数,则用最大个数、最小个数、比最大个数多1格、比最小个数少1个的数作为测试数据:

三、如果HDL程序的规格说明给出的输入域或者输出域是有序集合(如有

四、如果程序用了一个内部结构,应该选取这个内部数据结构的边界值作为测试用例;

五、分析规格说明,找出其他可能的边界条件。

错误推测法:靠经验和直觉来推测程序中可能存在的各种错误,从而有针因果图:通过画因果图,在图上标明约束和限制,转换成判定表,然后设计测试用例。这适合于检查程序输入条件的各种组合情况。

功能图:通过形式化地表示程序的功能说明,并机械地生成功能图的测试用例。

“黑盒”法着眼于HDL程序外部结构、不考虑内部逻辑结构、针对功能进行测试。“黑盒”法是穷举输入测试,只有把所有可能的输入都作为测试情况使用,卅能以这种方法查出程序中所有的错误。实际上测试情况有无穷多个,人们不仅要测试所有合法的输入,而且还要对那些不合法但是可能的输入进行测试。黑盒测试通常有下列的缺陷【5(1j:1.规格书可能不完备,特别是设计的角落部分;序表、顺序文件等),则应选取集合的第一个和最后一个元素作为测试用例;对性地编写测试用例。可以列举出可能的错误和可能发生错误的地方,然后选择测试用例。

很难检查设计的所有输入;

难以验证设计所有输出的行为:

如果输出有错误,很难确定错误的源头

某一些类型的缺陷很难被检测出来;

2.3.3灰盒子测试

灰盒子模拟是白盒子模拟与黑盒子模拟的混合产物。它不像黑盒子模拟一样对DUV内部。无所知,也不像白盒子模拟一样完全知道DUV内部信息。通过对关键信号的提取,灰盒子模拟可以提高验证的效率。

§2.4静态检查

静态检查是对DUV进行预查的有效手段。它主要对代码风格进行检查和评估。通过静态检查可以在开始模拟编译之前将语法错误,设计风格的违反检查出来,避免了以后编译调试的时间与精力。

静态检查工具通常可以预先设定设计规则。通过施加一个严格的设计规则,设计工程师可以避免大量可能发生的潜在的错误。通过培训和工作中使用,良好的设计规则形成的代码风格有效地提高了设计的质量。以下是视频后处理项目使用的简单但是有效的设计规则:

1.每行限定只声明一个端口、参数或变量。例如:

图表7每行限定只声明一个端口、参数或变量

2.所有的信号线必须显示声明,包括Ibit的wire信号线,二二态信号使用14

浙江人学fⅢ!I学位论业

tl_1束声明。小声明模块中不使用的冗余信号

3.‘个语匀一行

4.代码块之问采用空行分隔以增加可读性。代码必须整齐。采用统一缩进,

以及begin和end必须对齐等等

5.注释,尽量使用中文,简洁清楚并采用“,,”注释,而不是严…+/注释6.运算符与变量之间保证一‘个空格,如

assignc=(~alb)&~(e“f);

7.同一个reg变量不能在多个always块中赋值

8,case语句的分支要完全,并且一定要写default语句

9.非组合逻辑(即时序逻辑)用非阻塞型赋值:组合逻辑用阻塞型赋值10.

11.只允许时钟的上升沿触发所有寄存器的复位或置位必须是同步的,不允许“异步”逻辑出现12.调用底层器件时,对输入管脚都应该有确定的状态,禁止输入管脚

悬空

i3.always敏感事件表的变量要写全,不能有遗漏。也不允许敏感变量

列表中存在没有际使用的变量

图表8always敏感事件表

14.在if,else中的语句必须用begin开始,用end结束以避免就近匹配

原则而产生的错误15

图表9就近匹配原则

静态检查工具使用简单,不需要软件模拟,节省时间。通过静态检查软件的审查后的代码风格一致,便于今后的重用和移植,也为验证提供了一定程度的保证。但是静态检奄工具的作用也是非常有限,只能进行文本处理相关的检奄。

§2.5形式验证

2.5.1形式验证的原理

形式验证通过数学运算将设计与正确的设计进行一致性对比,得出是否一致的结论和不一致处的电路点。形式验证不需要验证矢量,运行时间也比模拟的时间要少,是一种彻底、严格的验证方法。

采用形式验证有助于在设计周期的较早阶段发现功能问题。形式验证的使用能确保较早地检测出绝大多数功能问题,从而能够更容易并以更少的成本来修复它们。16

浙L【=J、学坝I学位论史

?基于声明的验证?等效性检查

?属性/模型检查

验证流程

图表10形式验证流程

形式验证是一种无向量的验证方法。它不使用传统的激励.响应机制,而是采用系统的、智能的数学分析柬判断某个设计在所有的输入或状态条件下是否能按预期的情形工作。形式验证提取出比较设计和待比较设计中的对应点,通常是寄存器和输入输出端口。通过将设计分成许多的逻辑锥(Lo百cCone),形式验证比较相对应的逻辑锥。如果比较设计与被比较设计的对应的逻辑锥功能一致,则通过形式验证,否则报告不一致的逻辑锥的位景,以便进行分析。

》叫)

图表11逻辑锥

使用形式验证工具可使一个设计得到全面的验证。在用形式验证工具检查过每个行为特性后.被比较设计在任何工作条件或情况下都将与比较设计一致。

形式验汪在设计t的两个主要阶段一一“设计确认”和“实现验证”中是非常有用的。设计确认发生在设计阶段的初期,这时设计者设法确定该设计I执行搿是否币确,或荷是否符合设计规范要求。实现验证发生在没计确认之斤亏,用

以确保实现步骤中不会生成另外的缺陷。

形式没训4确认是用数学n,gYyi去检查设计是甭遵守用户定义的一系列特,I峰。设计者可以有二种选择,即检查所期望的特性是否总是发生或者检查不期望的特性永远不会发生。形式声明检查器、模型/属性检查器就是形式设计验证工具的二个例子。

等效检查器是最常见的一类实现验证工具。它们可用于自动验证由于设计流程的多阶段性而产生的设计转换。这些转换可能包括逻辑综合、布局布线、物理优化、测试插入、时钟树插入或对网表进行手T修改等设计步骤。

形式验证技术对设计有下列的要求:

1.必须有已经经过确认的比较设计;

2.设计采用同步设计风格;设计不能包含逻辑反馈回路;

3.端121,黑盒子,时序单元在参考设计和比较设计中必须结构一致;2.5.2形式验证的应用

当设计进行以下改进时可以使用形式验证代替同归验证:

●验证RTL--RTL的一致性。

1.增加时钟门控以减少芯片功耗;

图表12增加时钟门控

2.对关键路径进行结构优化18

图表14加入扫描链浙|T人学坝I学位lL-"迁“田’岖3.优化逻辑以减少芯片面积;●验证RTL—GATE设计的一致性。1.为以后的版本升级保留RTL级设计2.使用RTL设计进行系统级设计;3.使用RTL综合;?验证GATE—GATE设计的一致性。1.加入扫描链等测试逻辑;Pro.Sc^n……………………………Post.ScandobIndataou【¥carlIIiscane11elk

2.对扫描链重新排序3.加入时钟树;

19图表13关键路径进行结构优化

图表15加入时钟树

4,加入I/O引线脚;

5.进行设计布局布线;

6.设计展平}u调整单元大小

7.为硬件加速生成网表;

§2.6静态时序分析

静态时序验证可以嵌入完成综合后的设计流程的任一阶段,如逻辑综合后、测试准备后、版图设计后都可以。还可以在综合前,这主要是验证SOC设计中布局规划的合理性,由此得到准确的约束驱动逻辑综合。这里讨论要做到准确的时序验证需要着重考虑的几个方面:

●模拟工艺波动对时序的影响

?避免非真实路径的分析

?信号完整性的分析

2.6.1模拟工艺波动对时序的影响

由于同一硅片上的制造工艺、电压和温度有波动,门器件和连线的延时一般都是不确定的。为考虑最悲观的情况,如图t6,静态时序验证在检查DL2/ck到DL2/d的建立(setup)时问是否满足时,取:

?clockpathl的最大可能延唰

path的最长路径(datapalh.data1TlaX)的最大可能延时

clockpath2的最小可能延时

检查DL2/ck到DL2/d的维持(hold)时删足否满足时,敞

clockpathl的最小可能延时

data』ath憝最篷熬经(datapathjnin)麓最小可憨延列‘

clockpath2的最大可能延时

d0怕pall]Imal

CL

图纛16建立(setup)珏寸I霹

翅象试为上述的鼗大最,j、可琵延辩裁楚醚背最差帮最好浚凝下蕊延翳,这样的时序验证是过于悲观了。由于一块芯片面积只是整个硅片面积的几十分之一,其工艺波动也比整个硅片小的多,所以静态时序验证可以考虑合理的工艺波动对延时的影响。如图17,在芯片的这部分电路中,路径的最大可能延时就楚壤蓑馕援下夔延辩(鬻中xx/xx缝右边数字),最小可糍延嚣誊疑有最差谤凝下延时的80%<图中xx/xx组左边数字),静态时序验证检查DL2建立时间是否违反:

clockpathl+datapatNnax—clockpath2十setup<=dockperiod

在上述表达式中,

clockpathl=0.840,6=1.4

datapath_max=3.80

clockpath2=O.64十O.52=1,16

setup=0.2

霹跫,露暴要瀵避建立时闯,时镄遴麓至少要有l。《0+3。8G—l,16+0.2=4.24ns。

为保证设计成功,必颁在芯片生产6口就考虑片上工艺波动,并以此为标准验证设计时序。要做到凇确的验证时寄,需襞选择台理的工艺波动参数,不要

剖J,j考虑过严误导没计过程,也不要过松导致设计失败。

图表17工艺波动对延时的影响

2.6.2避免非真实路径的分析

静态时序验证计算电路中每一条路径的延时,路径分为四种:输入端口到寄存器数据端、寄存器数据端到寄存器时钟端、寄存器时钟端到输出端口和输入端口到输出端1:3的纯组合逻辑路径。只要有连接关系,不管该路径是否功能上真实存在,静态时序验证都会计算其延时,并按照约束判断其时序是否有违反。如图18,实际电路是永远不会激励同时经过两个选择器的A端或B端的路径的,这条路径就是一条非真实路径(FalsePath)[33]。

mux2图表18非真实路径

图表19多周期路径

还有,山于不做动态仿真,静态时序验证总是按照一个时钟周期来约束路径。,如果不指出经过乘法器的路径允许两个周期内到达,静态时序验证显然会认为醵路径违反时序约束。

对非真实路径和多周期路径(MulticyclePath)的时序验证往往混淆对关键路径的判断,所以在验证前,应该指出那些可能会违反时序约束的非真实和多周期路径,帮助正确分析电路并借以指导设计实现过程。

2.6.3信号完整性的分析

信号完整性是表示一个电信号可靠传送信息和抵抗临近高频电磁干扰的能力。要保证信号完整性,很重要的一点是要能够分析串扰(Crosstalk)对电路的影响【34-371。串扰是由于两根或更多的物理上接近的连线因为电容的耦合引起的电子干扰,它会影响信号跳变延时从而影响信号延时甚至改变信号值。当工艺尺寸缩小到0.18um以下时,电路中的串扰效应越来越严重。静态时序验证技术适合SOC发展的还有一个原因就是它可以考虑串扰效应,更准确分析时序,保证设计的成功。

下面来看一下串扰如何影响电路延时。假设图20中信号线A、B、c在物理上十分接近。因为电容耦合,信号B跳变的时刻会受到临近连线信号跳变的影响。连线A的上跳变可以引起连线B上的下跳变时刻延迟,这可能会造成经过B的路径的建立时间的违反。类似的,连线C的下跳变可以引起连线B上的下跳变时刻提早,这可能会造成经过B的路径的维持时间的违反。图表20串扰对信号跳变延时的影响

浙江人学{i!;j{j学位论义

图表21不同跳变时刻的串扰影晌

受到临近连线电容耦合影响的连线被称为受害连线(victimnet),旎加这种影响的连线被称为侵犯连线(aggressornet)。注意侵犯连线同时可以是受害连线,受害连线也可以是侵犯连线。侵犯和受害指的是两根被分析的连线间的关系。侵犯连线对受害连线的时序影响依赖于以下几点:

夺

夺

夺

夺耦合电容的大小信号跳变的时刻和斜率跳变的方向(上跳变、下跳变)多个侵犯连线对同一受害连线的总体影响

静态时序验证考虑所有的上述因素计算串扰影响。同时忽略那些耦合电容过小和耦合连线的跳变时刻不重叠的情况,这样可以节省不少运算时间。

图21显示了计算串扰影响时考虑跳变时刻的重要性。信号A有一个可能到达时刻的范围。如图,如果A上的跳变发生在最早时刻,它会引起信号B跳变前的一个向上的波动,这对信号B的延时没有影响。类似的,如果A上的跳变发生在最晚时刻,{1起信号B跳变后的一个向上的波动,对延时一样没有影响。除非波动太大,产生一个脉冲,这样的脉冲会在布置布线时避免掉。但是,如果A上的跳变和B上的跳变同时发生,就会引起B的跳变延迟,可能造成建立时问的违反。所以静态时序验证会计算出每一条受害连线和侵犯连线的最早和最晚可能发生的跳变时刻。这个最早和最晚的a,l间范围成为受害连线或侵犯连线的时I'tlJ窗。只有两类时恻窗交叠时爿发生影响延时的串扰。

验畦版图设计后设计的时序是否满足,需要在门级网表上反标后端提取出24

来的物理寄生参数,掘此计算连线和门的延时,分析设计时序。串扰分析时也一样,需要物理寄生参数。它实际上通过模型的彤式给出物理连线寄't-fl<j电容和电阻值。图22是~个版图的一小部分和它的包含耦台电容的详细模型。

Circuitmodel

叼gmssor11e{C

图表22耦合电容的详细模型

图表23版图的一小部分

以上分析了串扰分析的机制及它对信号完整性的影响。随着超深亚微米技术的不断发展,考虑信号完整性是ASIC设计的一个非常重要的部分。实际上,不仅静态时序验证时应考虑这部分影响,在版图设计时也应结合这种思想,才能设计出高性能的芯片。

§2.7声明验证

动态验证在设计规模增大的情况下表现越来越不尽人意,特别是在捕获边界条件和减少验证时间上。在验证SOC时,声明(Assertion)可以监视设计深处的信号协议。声明用来描述设计要求。对应测试计划,声明描述出什么是期望的信号忉、议,什么是不期望的信号协议。声明验证采用命题以可执行的形式来捕捉并证明设计假设及接口规范。EDA】一具能在仿真和形式验证期问核查这些命题,隶保证设引乖元工作JF常。ABV(assertionbased、Terification)在捕捉用传统

浙江J、学f叭卜’革位论』

的基于仿真的验证方法遗漏的缺陷时效率更高,因为命题就在本地检测缺陷。山于ABV不再需要传送错误到输出以进行比较,因而简化厂测试。本地检测电极大地减低了珍断错误根源的需求,提升了调试效率。

使用HDL语言‘建立的声明远不如声明语吉‘所建立的声明更有效率。OpenVera是Synopsys公司提供的声明语言。OVA(OpenVeraAssection)可以在模拟中进行动态检查,也可以在形式验证工具中进行静态检查,并且提供功能覆盖率的支持。OVA还提供重用库和预建立的声明以利于验证的重用f4酊。

OVA提供以下的特性:

1.基本事件与序列来描述事件发生先后:

2.参照过去和将来的事件的时间紧密序列

3.序列的逻辑组合

4.循环序列

5.条件序列

6.自定义的单时钟和多时钟

7.序列中的数据存储和检查

8.参数化的库支持

9.线性时序逻辑的规则表达式

10.表达式的异步支持

OVA支持层次化的验证。在子模块中的声明可以在验证上一层模块时使用。这种子模块独立的验证方式可以更快地完成设计的完全验证。OVA还可以访问过去,现在和将来的数据。这个特性提供了对特定时间点上的数据检查。比如在FIFO的输出检查过去的输入。

下例表明了OVA在描述信号协议时的便利:如果ready信号间断或连续地持续3个时钟周期,那么在4个时钟周期内必须transmit为真,或者期间有reset。

在图24中定义了2个事件,一是ready3,二是protocol。

Ready3定义为在3个ready信号持续有限,并且期间transmit信号与reset信号无效。

Eventready3:istrue(!transmit&&!reset)in(ready#[1.]ready#[1.]ready);

Protocol定义为如果read3发生,那么在紧接的4个时钟周期内transmit有效或reset有效。

Eventprotocol:if(matchedready3)then#[1.4】(transmit|Ireset);

最后声明检查事件protocol。

AssertcJrotocol:check(protoc01);

如果使用HDL语言将很难描述以上的时序。

图表240VA例

图表250VA例的时序mofluleprotoc01{clockPosedgeclkfeveDtready3:iStEue《‘t【o.nsmic&&!reSet)ineready耕l。.]ready引1..]EeadY);eVen七protoc01:itfmatchedrearly3)then¥【1..4]ftransmitI1reset);Bsse【tc—prOtOCol:check{Protoc01);)TIME0l2345n心…奸lfl-.】…却#【1..】~曲)I莹|Ol234S咄呻27

§2.8硬件仿真技术

现赴验证过程变成了一个系统验证问题。如果需要考虑多种总线接口、实时数据、嵌入式软件及外部用户接口,则将需要多次验证。此时,为了不影响整个上市周期,可以采用模拟加速技术。

仿真验证利用硬件的高速并行性加速验证的进程。仿真通常利用FPGA或CPLD等可编程器件,将设计局部或全部硬件化,通过通讯软件进行硬件与设计直接的信号交互。

尽管设计人员看到仿真设计与实际软件和外设一起高速运行时,但实际达到的ASIC功能空间测试覆盖面可能很小。查找、隔离、修复并确认某些类型的设计缺陷也可能仍比传统仿真工具费时。设计缺陷主要是由于待测在线软硬件和逻辑之间的复杂交互而引起的。此外,这一问题还会因所含无数时钟周期而恶化。在很多方面,仿真与系统级调试的相似点比模拟测试要多。正是由于这些原因,可以认为仿真是模拟的一种有效补充,而不是一种完整的验证方案。硬件仿真使得很多独特验证和开发工作成为可能。在模拟不能满足实际设计需要的场合,通过仿真生成的大量测试循环和实际系统环境的不可预测性非常相似。

如果正在开发一项新的大型复杂设计,那么仿真可以在该系统的环境下对芯片进行完整的测试。借助适当的仿真器,就可以将整个设计放到硬件上运行,其速度比模拟要快好几个数量级。

例如,采用仿真技术在两天内就可完成二百万门无线设计的验证工作,而采用传统模拟技术也许要花四个月的时间。

可以将lC设计映射到仿真器上”‘样,也可以将它与目标系统连接起来。这两种模式都可识别并解决在模拟中根本无法发现的问题。

§2.9多项目晶片

在大规模流片之前,通常还通过多项目晶片(MPW,multi—projectwafer)进行小批量的样片生产。MPW将多家设计融合到一起。通过多家共同分担NRE(NotRecurEngineering)费用来减少流片的费用。对于在设计阶段的产品来说,低成_i的MPW可以提供高保证的验证效果。MPW的。个不足是它通常需要超

过1个月的制造周期。而使用FPGA则是及时的。设计人员可以立刻看到结果并根据反馈快速修改设计。

§2.10验证效果的评估

对验证的效果进行有效的评估是验证工作不可缺少的技术。覆盖率分析是对验证工作评估的主要标准。如果不达到既定的覆盖率那么验证的工作就不足,需要有针对性地增加覆盖。

2.10.1覆盖率

覆盖率主要指代码覆盖率。代码覆盖率是评估DUV在测试矢量序列的激励下所达到的对代码的执行情况的表征。通常代码覆盖率含盖行覆盖率,条件覆盖率,路径覆盖率,跳转覆盖率和有限状态机覆盖率等【4Jo

行覆盖率是指在测试矢量序列的激励下DUV中的被模拟软件执行到的代码的行数与代码的总行数的比值。如果行覆盖率没有达到100%,那么意味着该DUV中没有被覆盖到的代码没有被测试过,在以后的使用中存在着潜在的问题。

进行行覆盖率分析还有助与提高DUV的模拟速度。通过行覆盖率,可以对执行次数占大多数的语句进行优化,提高总体运行速度。

条件覆盖率是指在测试矢量序列的激励下,DUV中的条件表达式中的所执行的输入条件的数量与所有的可能输入条件的数量的比值。对于没有测试过的条件输入在实际使用中有潜在的问题。

路径覆盖率是指在测试矢量序列的激励下,DUV中执行到的路径条数与实际可能路径条数的比值。对于没有测试过的路径在实际执行中可能存在未知的问题。

跳转覆盖率是指在测试矢量序列的激励下,DUV中数据位从0到1和从l到0的跳转数目与所有可能跳转数目的比值。跳转主要对数据进行监测。不完备的跳转覆盖可能意味着没计对某些数据存在不足,通常需要验证工程师有针对性地埔加特定地数摒或者进行更长的模拟过程。有限状念机覆盖二簪重点检查状态|1BJ的转换。必须对不I司的转换路径进行完

备的测试。通过对有限状态机的覆盖率的检测,可以保证在测试中没有遗漏转换路径。

有限状态机的测试还要考虑初始状态的可到达性和_F法状态的可跳转性。上电和复位后有限状态机要停留在确定的状态。如果因为异常,有限状态机跳转到非法状态时要保证有限状态机能够跳出非法状态,保证设计继续运行。

100CoverageWithoutCoverageWith

Time

图表26覆盖率曲线

2.10.2对覆盖率的误解

对于覆盖率普遍存在着误解。人们将100%的覆盖率定为验证的目标。事实上覆盖率只是验证的一个度量。100%的覆盖率并不意味着覆盖的目标已经达到。覆盖率并不能提供模块的正确性的信息。覆盖率用束在验证的过程中提高发现comercase的速度与便利。对于覆盖率反馈的信息,验证工程师可以更有针对性地建立testbench,及早地实现100%的覆盖率,提高验证的效率。覆盖率只能评估实现了的代码,对于由于设计人员的理解与规格书的不同而没有实现的功能覆盖率是无能为力的。这些只能通过功能验证来保证。

第3章验证自动化与重用

为了提高验证的抽象层次提高验证的效率必须进行验证的自动化和重用。在项目中验证代码量是设计代码量的2--4倍。如果每一次都重新进行验证代码的设计,验证工程师将无法跟上设计规模的增长。验证自动化比不可少。对于验证工作中重复的功能,可以利用重用技术提高验证的效率。而且由于使用经过检验了的代码,可以减少出于新建加入的缺陷。

本章讨论了应用高级验证语言‘实现验证自动化的实现,提出了全面验证重用的方案与实践。

§3_1验证自动化

各种设计的验证工作都包含一些共同的工作。对于这些工作进行抽象,并通过自动化实现能够有效地提高验证的效率。一些适于考虑进行自动化的测试操作为:

l堋0试用例的生成(包括测试输入,标准输出,测试操作指令等)。

2.测试的执行写控制(包括单机与网络多机分布运行,夜间及假日运行,测试个案调用控制,测试对象、范围、版本控制等)。

3坝9试结果与标准输出的对比。

4.不吻合的测试结果的分析、记录、分类、和通报。

5.总测试状况的统计,报表的产生。

下面举出一些测试自动化的例子:

3.1'l测试用例的生成

用编程语言或更方便的脚本语言(例如CShell,Perl,TCL等)写出短小的程序来产生大量的测试输入(包括输入数据与操作指令)。或同时也按一定的逻辑规律产生标准输出。输入与输出的文件名字按规定进行配对,以便控制自动化测试及结果核对的程序易于操作。这q!提到测试个案的命名问题,如果在项目的文档设计中作统。规划的话,

软件』、2品的需求与功能的命名就应垓成为盾继丌发过程的中间』一品的命名分类依槲。这样,就会为文档管理和配置管理带来很大的方便,使熬个产晶的"发过稷交得更有条理,更符合逻辑。任何新手半途加入到开发工作巾也会更容易避入状态。

3.1.2测试的执行写控制

翦元测试或集成测试可能多用单机运于亍。但对于系统测试戏回归测试,就极有可能需要多台机在网络上同时运行。在开发过程中的任何时候,如果需要等媛溺试豹运行羹暴熬话,那羧是一一令缀缀野发霹渗熬穰会。

对于荤个豹测试运行,挖潜的机会在测试的设置及开始运行和结果的对比及撼示。有时候,需整反复修改程序,重新编译和重新测试。这样,每一个循环的各种手工键入的设嚣与指令所花费的时阈,加起来就非常可观。如果能利t霹lmake或类{陛靛软件_】二其寒蘩助,藏能节省大量懿露I蠢J[20,33]。

对于系统测试或国娲测试这类涉及运行大量测试臻辆的}鸯况,挖掘潜力翡机会除了利用软件工具来实现自动化之外,就是怎样充分利用…切硬件资源。通常在白天的工作时间内,每台计算机的负荷都没有被充分利用。能够把大量测试鞲侧分配到各台机器上去同时运{亍,就熊节省大量的时闻。另外把大量的系绕测试及嚣妇溅试安瓣翻夜凌及羯末运行,也魏提毫效搴。

嗣时,软件19动测试工具必须能够有办法方便地选择测试用例库中的全部或部分来运行,也必须能够自由地选择被测试的产品或中间产晶采作为测试对象。

3。1.3溪试结巢与禄准狻密酶对比

在设计测试用例的时候,必须考虑到怎样才能够易于对此测试结果和标准输出。输出数据量的多少及数据格式对比较的速度有直接影响。而另一方面,也必至夔考虑到输出数搦与测试用倒的测试鳍栎的逻辑对应性及翁读性,这将会大天骞稠予分援溺试蹶发疆豹夺唆舍,也有铡予溅试嗣溺戆缭护。

许多时候,要写…些特殊的软件来执行测试结果与标准输出的对比工作,凼为可能有部分的输出内容是不能直接对比的(比如,对运行lI勺FI期时阳J的记录,对运行的路径的记录,以及测试对象的版本数据等),就要用程序进行处理。

浙江人‘竽1咂I争’位论文

3.1.4不吻合的测试结果的分析、分类、记录和通报

I一一点所谈到的,用于对测试结果与标准输出进行对比的特殊软件,往律也同时担任对)fi吻合的测试结果进行分析、分类、记录和通报的任务。

“分析”是找出不吻合的地方并指出错误的可能起因。“分类”包括各种统计L的分项,例如,对应的源程序的位置,错误的严重级别(提示、警告、非失效性错误、失效性错误,或别的分类方法),新发现的还是已有记录的错误,等等。“记录”,足按分类存档。“通报”,是主动地对测试的运行者及测试用例的“负责人”通报出错的信息。

最直接的通报方法是由自动测试软件发出电子邮件给测试运行者及测试用例负责人。邮件内容的详细程度可根据需要灵活决定。

3.1.5总测试状况的统计,报表的产生

这些都是自动测试工具所应有的功能。目的是提高过程管理的质量,同时节省用于产生统计数据的时间。

产生出来的统计报表,最好是存放到一个约定的路径位置,以便任何有关人员都知道怎样查阅。同时,可按需要用电子邮件向适当的对象(如项目经理,测试经理和质量保证经理)寄出统计报表。

为了充分利用时间与设备资源,下班之后进行自动的软件构建,紧接着进行自动测试(这里多数指的是系统测试或回归测试),是一个非常行之有效的方法.

§3.2高级验证语言

提高验证效率必须推进验证的自动化。验证由于它的特殊性需要使用专业的验证语言来提供抽象性的支持。通常的设计是由业界应用最为广泛的硬件描述语言,VHDL或者Vefilog语言进行电路设计。验证工程师可以使用VHDL或Vefilog语言书写testbench,这样的验证语言是与设计语言一致的,可以无缝地使用模拟器。但是硬件描述语言的本意是为了实现硬件电路的描述。而验证是1i需要物理实现的,它更是一种软件的概念。硬件描述语言不可能实现对验

—————————————————————————~龇扎人竽fl_)!I争。化L色殳

证需求的强力支持。高级的验证语言内部嵌入了对验证的支持,提高了验证的抽象层次,最终便利了验证1=程师的工作,提高了验证效率。现在还没有标准化的验证语言,f且是Verisity公司推出的E语言,Synopsys公司推出的vERA等验证语言可以在市场上得到。E结合着SPECMAN工具,vERA结合着vcs模拟器可以提供对验证工作的有力保讦。

3.2.1验证语言与HDL的比较

对于验证工作中必须的比较工作,验证语言都由比硬件描述语言更加有效CLK-]n厂|厂】『_1㈠F/『]Y1广|n。一一~…uuuUUr_.U

Vera:

@l,10¥signal==exp;

e

expect{[1..9];true(’signal,-=exp)}@dk

Verilog:

begin

repeat(1)@(posedgeclk);

fork:window

begin

wait(signal==exp);

disablewindow;

end

begin

repeat(9)@(posedgeclk);

Sdisplay(”E1TOr!”);

¥finisb;end率的语句。通过以下的Veril。g语言对输出的比较可以看出验证语言的便利。Siganl皎一...二面二二二)④图表27时序检查

浙江入学坝I学位论文

j0111

end

E例使用了VERA,E,verilog实现对信号signal的时序检查。当signal信号在1到10个后续时钟周期内保持为exp的值时,testbench继续运行,否则系统报错并停止运行。由于verilog语言‘没有对验证的内在支持,所以要实现这样的。。个简单的功能验证需要14行代码,而VERA和E语言都是高级验证语言,它们只需要l行代码就可以完成以卜功能,验证效率大大提高。对于复杂的设计的验证,使用高级验证语言更是有着优越性㈣。

尽管使用verilog的函数功能可以将代码封装起来,如下:

tasktaskwindowwait;

in。putleft;

integerleft;

i‘nputright;

integerfight;

m‘putsignal;

m。putexp;

mputclk;

begm

repeat(1eft)@(posedgeelk);

fork:window

begin

wait(signal==exp);

disablewindow;

end

begin

repeat(right)@(posedgeclk);

Sdisplay(”Error!”);

¥finish;

end

jom35

浙江人学城I‘学位论文

end

在使用时调用函数:

taskwindow_wait(1,9,signal,exp,clk);

这种方法也是无法与高级验证语言‘在效率上进行相比。这种在verilog语言的基础卜l改进的方法有下列的不足因素:

1.需要单独建立适应不同需要的函数;

2.复杂规则的函数难于建立;

3.Verilog函数的不可重入性限制了改种方法的使用:

3.2.2测试矢量自动生成

验证语言都实现了测试矢量的自动生成。通过对矢量的条件进行约束的设定itJ.以自动地进行测试矢量地生产工作。

随机激励通过随机变量的定义与约束条件和随机函数共同生成。

以下是一个使用随机激励生成的vera源代码

constraintcDatal{

riaddress>=0:

riaddress<256;

riData>=一1;

riData<-23×riaddress;

}

处理随机数的产生外,随机序列的自动产生是验证自动化的重要部分。在VERA中可以高效地产生随机序列。

randseq(){

main:topmiddlebottom;

top:{…;;;

middle:f…}bottom:bottom:【.:}{…:l:

I

randseq语句执行的只是第一句main,然后再调用其他的语句。可以加权重来有概率地执行语句,如下例:

main:&(2)topl&(4)middleI&(6)bottom;

其中top语句以2/12的概率执行。

middle语句以4/12的概率执行。

bottom语句以6/12的概率执行。

3.2.3进程控制

高级验证语言都提供了简便的进程控制支持。

VERA提供了forkjoin语句支持并行控制。

图表28进程控制

fork

{

语句1

菪铌;语句N

浙江,、学顺卜学位论文

Joln[allIany}none3

使用joinall会等待所有进程执行完毕后执行下‘条指令,joinany则会等待任何一个进程执行完毕后立刻执行F一条指令,joinnone则立刻执行F_。条指令。充分的进程控制语句为验证代码的设计提供了极大的变量。验证工程师将不会被语言‘所束缚。

3.2.4进程通信

多进程间的通信是建立。个高效的测试程序的必备保证。如果使用全局变量进行进程间的通信那会是一个灾难。VERA对进程间的通信的细节进行封装。用户可以方便地使用3种进程闯的通信方式:Semaphore,Region和Mailbox。

1.Semaphores

Semaphore相当于一个装有钥匙的虚拟的桶。如果桶里还有钥匙,那么进程可以拿走一把钥匙,并进行相应的操作。如果桶早没有钥匙,那么进程必须等待其他进程还回钥匙刁‘能进行相应的操作。

2.Regions

Region提供了一种互斥机制,它保证不同的进程不会同时访问同一资源。Region内有不同的钥匙,每一个进程要访问一个资源时,它必须得到该资源对应的钥匙,否则必须等待其他进程返回该钥匙。

3.Mailboxes

Mailbox提供进程间交换信息的机制。Mailbox01]同实际的信箱。现被放八mailbox臼勺信息会现被提取。如果进程访问mailbox时,如果mailbox里没有信息,该进程可以等待信息或者离开。

由于高级验证语言提供的进程控制结构提供的高效支持,验证工程师可以方便地写出并行的程序,而且进行程序削的通讯。这提高了复杂系统的验证工作的效率。

3.2.5directC技术

数字视频后处理芯片项目利用directC技术对VERA的不足进行弥补。在项目设计t时如果已经有了c语言形式的设计或工具,??r以利用dircetC技术实现重用,减!b新建的丁作量。

DJ【“l(’L.Jh

图表29directC流程

图表30VERA与C的数据对应图表31VERA与C的函数对应i+file:adder.c{{/+adder.c—addsint0andbitvec0andreturnstheirintcfunc0(intinto,intbitvec0)(SLIm+/

intitmpj

printf(”C—received%d%d\n”,intO,bitvec0

itmp=int0+bitvec0

return(itmD)j

/+file:adder.c★/

Hcfunc0

anowtakesanintegerandbitvectorfromVERA,andreturnsbitvector+|

vec32+cfunc0(int

Staticvec32into,vec32★bitvec0)fstorageforthesum.tmp;//Temporary

vec32+ptri

intitmp;

ptr=&tmpj

printf(”C—received%d%d\n”,int0,bitvec0一>d)jitmp=int0+bitvec0一>d;ptr一>d=itmpj//Addingandbitvectorinteger

return(ptr);/+ReturningsumbitvectortoVERA.+///file:adder.vr

#include<reradefines.vrh>

#include”adder.if.vrh”

#include”adder.dc.vri。‘//Includetheheaderfilehereextern”C”functionbit[31:0】cfunc0(integerinto,bit[7:0]bitvec0)?

classAdder{

bit【7:0]in0

bit【7:0]inlrandrand

浙i【J、学f"I。学似论艾

taskshow(){

printf(“VERA—driving%d%d\n”,inO,inl);

)

)

programadder——test

{

Adderobjj

obj=new()j

repeat(i0)

(

if(!obj.randomize())

error(”Randerror\n”)i

@oadder.inO=obj.in0;//Drive

adder.inl=obj.inl;toRTL.@o

@o.3

Cadder.outO==cfunc0(obj.in0,obj.inl)j//InvokefromVERA.function

obj.show()j

)

)

§3。3验证重用

3.3.1重用的重要意义

在SOC时代对设计的最大限制是人们对规模巨大的复杂度的掌握,而不是复杂度的提供与制造。随着设计规模的急剧增大,设计时问被大大地拉长。然而市场的压力却迫使人们实现更快的上市期。

一般而言,,“品快速丌发的最大障碍是设计周期中的功能验证环节。高密度ASIC设计不断引入的新功能及各种新功能之间的相互联系,加深了验证1:作的复杂程度。捡验那些数百朋、]级没计能甭精确地完成预期功能,就需要长41

刚问、伞面的仿真及昂贵的测试1I具。所以,目6U一些设计小组要耗费一半的H,I-I’日怫1资源米完成验证厂作,这不足为奇。

设训人员们通常采用新语言和新工具来解决速度和成本问题。在功能测试过程中,语占和T具固然扮演着很重要的角色,但在很大程度上,它们还是次要的因素。基于系统级芯片的嵌入系统,其系统级功能验证的进一步发展需要新的方法。它必须具有高度的灵活性,并能在调动所有项目参与者的同时,使复杂程度最低。更重要的是必须能够使代码和组件得到最大程度的复用以加速功能验证。当然,这种基于代码和组件复用的功能验证方法学体系,还应该显著缩短测试文档的丌发时间,并提高设计人员的工作效率。

为了实现上述目标,有力的掌握复杂度而不是被复杂度掌握需要普遍的实现重用。同设计重用一样,验证重用同样具有不可忽视的意义。

验证重用的目标是减少建立验证环境的工作,增加验证的效率,加速系统验证的速度,提高验证的质量。ASIC的密度和性能在继续发展,设计周期中的功能验证环节仍将是设计人员必须面对的重要挑战。通过建立基于软件复用方法学体系的功能验证方法,设计人员就能够大幅减少验证所需的时间和资源,确保产品及时投放市场。

3.3.2重用的目标

重用会带来以下好处:

1.提高代码生成率;

验证工程师直接使用经过验证过了的模块代码,无需重新书写底层代码,节省了验证的时间。

2.缩短丌发周期:

验证工程可以使用框架式的结构,快速地建立和改变验证结构。

3.降低代码丌发和维护费用:

由于新代码减少了,那么由新代码导入的缺陷也相应地减少了,验证的1:作量也会减少。

4.牛产更加标准化的代码:

山丁.效率提高,工程师叫‘以更加关注与代码的质量而不是完成代码的速唐.42

浙江人学埘l学位论疋

5.提高代码丌发质量;

6.减少软件丌发人员数量:

7.使丌发人员能比较容易的适应不同性质的项目丌发。

不同的项目共享相同的代码,丌发人员不必为每一个项目丌发单独的代码。

3.3.3重用的层次

验证重用需要在各个验证层次上体现。

1.同一模块,不同版本的设计的验证重用

在设计中,设计的版本更形是不可避免的。如果设计的需求在设计时发生了一些细小的改变,那么设计也就得跟随着改变,随之而来的便是对验证代码的改变了。通过对验证语言的选择和验证结构的优化,可以很便利地实现利用以前的设计而不需要熏头再来。

在设计验证结构时,要加重对重用结构的实现。将DUV的驱动和结果比较等严密地结合在验证代码中不是利用重用的结构设计。为了实现重用,验证结构必须将DUV激励的产生,施加和结果比较都要使用独立的结构。这样如果设计有细小的改变时,比如增加或减少DUV的端口等,就可以通过修改其单独相关的结构来实现,不需要对验证结构改动太大。

2.同’项目,不同模块的设计的验证重用

对于不同模块的验证的共同之处是验证的框架,不同的是验证的细节。同上~样的将框架与细节清楚地分开有利于将相同的验证框架移至到不同的模块的设计的验证工作中去。

3.不同I质目间的设计的验证重用

不同项目间的验证的重用的是最有挑战性和意义的工作。此时的验证重用体现在验证文件,目录,脚本的重用和验证IP的重用。验证文件,目录,脚本的重用可以提供高效无误的支持。验证IP的重用可以从根本上改变验证工作的方式。验证【P的建立,分发,维护将是今后验证工作的一个热点瞄】。43

3.3.4测试代码的重用

要实现测试代码的重用,必须要构建种可复用及可扩展的验证测试环境,采用严格的代码编写方法,和制定代码编写的内部标准。

构建一种可复用及可扩展的验证测试环境,首先需要采用基_丁面向对象的设计技术。这种以数据为中,心的方法,应该洋绌、精确地描述系统所有接口的数据类。通过将这些特有的数据类型与它们各自的接口相联系,并详尽而有效地进行定义,设计人员便完成了构建用于验证的可复用代码过程的第一步。数字视频后处理的项目没有使用verilog作为验证语言,而是采用VERA作为验证语言。因为VERA是面向对象的高级验证语言,便于实现重用。

通过系统接口以数据为中心的描述,设计人员就可以添加这一项功能,即在测试系统插入数据进行验证,或从测试系统中提取数据以验证测试结果。一旦这些具有插入激励和提取结果功能的代码编写完毕,便可将其与面向对象的数据类集成起来,压缩到可按次序排列的更大数据类中。

复用方法的第二个关键要求是采用严格的代码编写方法。要使代码的可复用性最大,组成设计验证环境的软件,必须严格按照高度模块化的软件设计概念进行编制。例如,设计人员不应编写一个单片电路程序来进行测试,而应首先编制一个独立的模块来描述测试器件引入激励的过程,再编制第二个模块来检验结果,最后编制第三个模块,用来度量测试的有效范围。这种方法使不熟悉源代码的设计人员也能方便地读懂它、理解其功能的实现方法,并在类似项目或将来的项目中复用部分代码。同时,这种方法也便于代码的初始设计人员以后维护和修正代码。使用vera建立testbench的时候,激励的产生封装成一个类。理想期望的产生也封装成一个类。验证的主体结构也封装成一个类。

制定代码编写的内部标准

丌发人员需要根据协商的设计标准保持一致的代码编写风格。为了巩固这种方法,项目负责人必须确立满足这些目标的内部标准。为确保代码的征确性、可读性和可维护性,代码复习的重要程度不Ⅱ于代码的常规设计。这种复习同样也为J1:发小组成员提供交叉培训I的机会,使其熟悉项目的不同部分。

无论是在项|=j内部,还是在项目与项目之恻,使资源得到晟犬复用的任何功能验证方法,都必须甲衡现有的资源。设计人员应该最大限度地复用其他内

部研发人员、第二方或I.具销售商的现有组件o”1。

刈于验证人员都要实现的特性,数字视频后处理项目将其封装成可以重用的类提供给验证工程师使用。如由一个vera的类C1TI实现DUV的覆盖率的检查。

Cm类提供以下的功能接口:

1.指定检查覆盖率的对象;

2.设定覆盖率检查的种类;

3.设定覆盖率检查的目标;

4.提供覆盖率的报告;

5.在覆盖率满足的情况下停止验证程序:

通过将Cm类分发给验证工程师后,每一个人都避免了重复编写相同代码的工作,而且得到该类可以有效工作的保证。

3.3.5测试环境的重用

在验证时需要使用不同的软件。如vccfa源程序的编辑,编译,VCS模拟器的使用,对输出的文本处理,unix操作系统的使用等。使用脚本来管理这些软件的运行。这些脚本将软件的运行条件进行了有效的封装,验证工程师可以直接重用,避免了手动输入每一个命令行的时间和出错的可能【331。

在验证时需要经常进行验证程序的编译,运行工作。通过对脚本的重用可以提高验证的速度。视频后处理项目使用makefile进行脚本编写,使用make命令进行脚本的执行【20,541。Make是UNIX系统提供的一个命令,通常用于源代码的编译与安装。

Makefile文件有其特殊格式如下:

注解:在Makefile中,任何以”撑”为开头的文字为注解,make在执行Makefile的时候会忽略它。

续接下行:在Makefile中,若一行不足以容纳该命令的时候。可于该行之最后加一反斜线(\)表示F。一行为本行之延续,两行应视为一行来处理。

宏(macro):宏的格式为:<string>=<value>例如:CFLAGS…O

<commatadl>systypebsd43法I)2.tJ(Rulesl:格式如F:<Targetl>:<depend>

<command2>

<Target2>:<depend>

<command3>

<command4>

下面是一个非常简单的Makefile。

假设有。个程序,共分为下面的部份:

menu.C主要的程序代码部分

menu.hmenu.c的includefile

utils.c提供menu.C引用的一些functioncalls

utils.hutils.c的includefile

同时本程序代码亦引用了ncurses的function

menu.c和utils.e放在/usr/src/menu下。calls。

menu.h和utils.h放在/usr/src/menu/include下。

程序编译完之后,可执行文件名为menu且要放在/usr/bin下面。群ThisistheMakefileofmenu

CC=gcc

CFLAGS=一DDEBUG—C

LIBS=一lncurses

INCLUDE=.1/usr/src/menu/include

a11:cleaninstall

install:menu

cNnod750iIlenu

cprnenu/usr/bin

nlenu:menu.Outils.O

¥(cc)一0¥@¥?¥(LIBS)

menU.o:

¥(cc)¥(CFLAGS)一0¥@menu.c¥(INCLUDE)

utilsO:46

浙江人学删j学位论文

¥(cc)¥(CFLAGS)一o¥@utils.c¥(INCLUDE)

Clean:

一iTn}.0

在卜述的Makefile中,要使用某个macro可用¥(macro_n锄e)如此的形式。make会自动

的加以展开。

¥@为陔rule的Target,而¥?则为该rule的depend。

若在command的前面加一个”.”,表示若此cornmand发生错误则不予理会,继续执行下去。

,L述的Makefile的关系可以表示如下:

a11

/\

cleaninstall

\

menU

/\

mentl.outils,o

若只想清除source以外的文件,可以打makeclean。

若只想做出menu,o可以打makemenu.o。

若想一次全部做完,可以打makeall或是make。

要特别注意的是cmmnand之前…定要有一个TAB(R[ITAB键1。

3.3.6目录结构的重用

验证工程师应该使用同一种目录结构以便利工程师之问的交流。对与执行相同命令的脚本可以在不同的工程师问无需修改地使用。从验证工作的角度,视频后处理项目重用了如下的验证目录结构。47

浙≯[人学坝I‘学位沦爻

垒

图表32验证目录结构RRIlI...._J【..._Jscripts5cripts

根目录与验证模块同名。

Bak目录下包含所有的备份文档。

Bin目录下包含ped脚本,shell等可执行脚本和应用程序。

Doc目录下包含readme等说明文档。

Dut目录下包含被验证的模块源代码。

Include目录下包含所有vera类的代码。

Ova目录下包含ovaassertion的代码。

Sim目录是运行模拟时的工作目录,其下的scripts目录包含所有模拟使用的脚本文件。

Vera目录是运行vera编译程序的工作目录,包含vera的主程序和vera编译程序产生的辅助文件,其下的scripts目录包含所有编译使用的脚本文件。

所有的文件通过相对路径进行访fq,以保证整个文件夹备份或移动后能够不需修改地执行脚本。

脚本的执行通过make程序进行管理。

3.3.7DFV设计与设计重用

验证不仅在提交设计前非常重要,在完成芯片制造后如何进行验证和调试是男一个重要问题。由于芯片的高复杂度,通常无法利用芯片的有效的管脚进行仃效的验证工作。l们食证设计(DesignForVen-ification,DFV)屉当fjlJ形势下

芯片设计时必须仔细考虑的一个问题。

DFV通过将验证逻辑嵌入芯片的设计巾,芯片制造后只有进行有效设置就能够工作在验证模式下,便于工程师进行调试。虽然DFV逻辑并不参与芯片正常工作,但是DFV逻辑简化了验证过程和方法,减少了芯片验证成本,与芯片面积增加的成本代价来说远远是得大于失。

最简单的DFV方法是增加对内部数据的可观察性。通过将内部节点引出信号到输出管脚便可以在芯片运行时进行对内部数据的观测。这种方法简单有效,但是需要改进以便实用。由于内部关键节点很多,如果都引出到管脚的话会增加管脚数。由于芯片已经大量使用管脚,无法也没有必要使用单独测试管脚。因而通过使用输出管脚复用将内部信号引出到输出管脚。根据选择信号的不同可以在输出管脚卜观察到指定的内部信号。

视频后处理芯片使用12C总线配置测试选择寄存器来选择不同的信号。这样芯片既实现了对内部信号的观察,又没有增加管脚,芯片的面积增加也非常有限,对成本影响极少。实践证明这种DFV的工作为以后的调试工作节省了大量的时间。

12C配置寄存器

内部

信号a

内部

信号b

输出

图表33DFV设计

另一种DFV方法是采用内建自测(BuildInSelfTest,BIST)模块。B1ST模块可以自身产生激励施加到被检测模块上,同时对被检测模块的输出进行同步检查对比,确定被检测模块的工作情况是否正常。通过增加BIST模块,可以实现对芯片内部的功能模块进行测试。如果不通过测试就可以定位查找。BIST既可以实现对芯片制造故障的检测,也可以实现模块功能的检查。视频后处理项目,芯片为了芯片的强壮性,对输入时钟增加了倒相选择逻辑,对输入信号的延时自动选抒,方便了对不理想时钟的处理,简化了以后的调试c49

LII于视频后处理项目芯片内已经实现了12C模块,对RAM的BIST模块等。重复利用这些已有的功能,可以实现既增加DFV的功能又小会增加芯片的成本,也不影响验证的效果,是比较理想的方案。

浙江J、学倾I。学位论艾

第4章验证管理

为了实现对验证质量的保证,在验证过程中对各项丁作的高效管理是关键。验证管理是对验证过程的约束,以提高验证过程的合理性和有效性来为验证的效果保驾护航。

本章结合数字视频后处理项目的实践对验证管理包括文档管理,人员管理,质量管理等进行探讨。

§4.1文档管理

程序是代码加文档。验证过程除了验证语言书写的代码外还必须提供相应的文档支持。最重要的文档是测试计划,其他还有测试记录和版本等。

4.1.1测试计划

测试计划是对验证过程的+个统筹,对验证对象的界定。通过测试计划,验证工程师可以合理的安排时间进度。验证工程师所有的工作是对测试计划负责,保证验证过程符合测试计划的安排。测试计划是验证过程中最重要的文档[16,17,38]。

测试计划应该包括以下内容。

1.测试计划标识。说明赋予该测试文档的唯一编号。

2.背景介绍。概述软件背景资料,及要测试的该软件的事项及性能。可以

包括必要的各项目及其历史,以及与之相关的其它计划的参考材料。

3.测试项目。如果有以下材料的话,请提供参考资料:

需求说明书、设计说明书、用户指南、操作指南、问题登记指南、测试

外的其它各项。

4要测试的特性。确定要测试的所有方面的特点。例如性能、或功能性。

确定与各项性能关联的测试设计规格。

5不测试的特性。在某些情况下,某些需要测试的特性现在还不能测试,

存此一一列出。

6.方‘法与步骤。蜕明整体的方法与步骤,指出用于测试每个特性绢的主要51

浙江J、学坝{?学位论义

活动、技术和工具。这旱要作到足够洋尽,以能够确定主要的测试任务,并能估计出每项所需的时间。说明想要的可理解度的最低要求。确定衡量测试工作的可理解度的技术。确定测试的重要约束条件,如测试条目的有效性、测试资源可用性、最后日寸限。

7.各项“通过/失败”的准则。说明用于确定每个条目测试是否通过或失败

的准则。

8.测试中止的标准和恢复的条件。说明全部或计划中所列各部分测试活动

中止及重新启动的条件,指出那些必须重复的测试活动。

9.测试的交付。确定下要提交的文档,可能包括:

测试计划、测试设计说明书、测试用例说明书、测试流程说明书、测试项目传输报告、测试记录、测试事件报告、测试汇总报告、测试输入数据和测试输出数据、测试工具。

10.测试任务。确定必须准备并执行的测试一系列任务,标识出所有任

务间的依赖性和所需的特殊技能。

11.需要的环境。说明测试环境的必需资源、及必要的道具。这些应包

括:硬件、通讯、系统软件、独立平台或局域网,及任何其他需要的专用软件。

12.责任和角色。确定各个不同测试活动小组的责任,如管理、设计、

开发、建造、执行、验证、问题登记以及问题解决。这些小组将包括系统管理员、开发者、质量保证员、测试分析人员、实际系统用户、帮助文书员、项目经理人员以及小组长。

13.人员配备和必要的培训。确定根据技能水平所需的测试人员配备,

以及执行测试任务所需的培训。

14.时间计划安排。应包括项目计划早确定的各个转折点(Fixpoint/Mile

stone)。

15.风险和意外处理。确定测试计划中的可能的高风险,并说明各种意

外事故的应对汁划。

16.审批。标识出所有必须同意这个计划的人员的姓名和职务。

4.1.2测试记录

测试汜录是对测试过程的历史记录。为了实现测试的重现和对测试质量的合理评估,测试记录的保存至关重要。如果在测试过程中发现了缺陷,那么记录中还要对缺陷的原因进行分析。

除了使测试过程可重复之外,还需度量项目以便于明白修改是提高还是恶化了软件质量。以下是一些可供度量所在项目的数据:

?对错误的管理性描述(所提交的数据、编写报告的人所修改的数据)?对问题的充分描述

?重复问题的方法

?对问题的建议处理方法

?相关错误

?问题的严重性——例如,致命错误,令人讨厌的错误或无关紧要的错

误

?错误排序——分析、设计、代码或测试错误

?代码错误的排序——边界错误、赋值错误等等

?所确定的错误位置。

?由修改所引起的模块和子程序修改

?每个错误所影响行数

?发现错误所需时间

?改正错误所需时间

一旦得到以上数据,就可以对其进行分析以确定项目质量是好还是不好。?每个子程序的错误数。从最坏到最好的顺序排序

?发现每个错误所需平均测试时间

?发现每个错误所需平均测试用例数

?定位每个错误所需平均编程时间

?测试用例所覆盖代码的百分比

?每科,严重错误中突出错误数

4.1.3版本管理

版本管理是文档管理中重要的一环。因为错误的文档版本会在项目中导致不可想象的混乱,极人地延迟项目的进度㈣。

在书写代码时要保证所有人工作在同一个版本上。如果设计工程师更新了版本,而验证工程帅还工作在旧版本上,那是BtI'日J与资源的极大浪费,并造成项目进度缓慢。

就是同一个人也需要进行有效的版本管理。当对源版本进行修改后生成版本A,又对源版本进行修改后生成版本B。此时很难同时保留A与B的工作。

版本管理通常使用版本管理软件来避免人:【在版本管理中的出错情况。版本管理软件可使用商业软件,GNU的CVS软件等。

§4.2人员管理

验证工程师是所有验证技术的实行者,验证过程的体验者。先进的验证方法学要同先进的人结合才会转化为先进的生产力。

验证工作的特殊性对验证工程师提出了特殊的要求:

1.沟通能力

一名理想的测试者必须能够同测试涉及到的所有人进行沟通。当告诉某人他出了错时,就必须使用一些外交方法。机智老练和外交手法有助于维护与开发人员的协作关系,测试者在告诉开发者他的软件有错误时,也同样需要一定的外交手腕。如果采取的方法过于强硬,对测试者来说,在以后和开发部门的合作方面就相当于“赢了战争却输了战役”。

2.技术能力

就总体言,开发人员对那些不懂技术的人持一种轻视的态度。一旦测试小组的某个成员做出了一个错误的断定,那么他们的可信度就会立刻被传扬了出去。一个测试者必须既明白被测硬件系统的概念又要会使用工程中的那些工具。要做到这一点需要有几年以上的编程经验,前期的丌发经验可以帮助对软件丌发过程有较深入的理解,从开发人员的角度诈确的评价测试者,简化自动测试:r具编程的学习曲线。3.自信心

丌发者指责测试者mj’错是常有的事,测试者必须对自己的观点有足够的自信心。如果园J,j别人对自己指责而改变自己的观点,就不i能完成什么更多的事情了。

4.很强的记忆力

一个理想的测试者应该有能力将以前曾经遇到过的类似的错误从记忆深处挖掘出来,这一能力在测试过程中的价值是无法衡量的。因为许多新出现的问题和已经发现的问题相差无几。

5.而小心

一些质量保证工作需要难以置信的耐心。有时需要花费惊人的时间去分离、识别和分派一个错误。这个工作是那些坐不住的人无法完成的。6.怀疑精神

可以预料,丌发者会尽他们最大的努力将所有的错误解释过去。测试者必须听每个人的说明,但他必须保持怀疑直到他自己看过以后。7.洞察力

一个好的测试工程师具有“测试是为了破坏”的观点,捕获用户观点的能力,强烈的质量追求,对细节的关注能力。应用的高风险区的判断能力以便将有限的测试针对重点环节。

同时验证人员要有下列的专业水平要求:

1.抽象能力

为了提高验证的效率,验证工程师必须在验证时提高抽象层次,合理的建立BFM(busfunctionmodule),使用高级控制语言来加速验证。2.数据处理能力

验证会产生大量的待分析的数据,验证工程师要对数掘进行合理有效的组织和处理。

3.软件与硬件编程能力

验证语言摈弃了硬件11]-实现性的约束,验证工程师通过对软件技术的运用可以提高验证的技巧。同时DUV由硬件描述语言描述,验证工程师必须对其有一定的了解。

沛7rIJ、学似3学位沦史

4.专业软件使用能力

在验证工作中,验证工程师必须使用模拟器,专用分析软件等来提高debug的效率。

§4.3质量管理

“质量是免费的”。实现高质量的产品可以免除后期的为产品质量付出的成本。低质量的产品必然在后期为质量的修复花费人力物力。加强过程的质量管理有助于提高设计的质量。从产品的整个生命周期来看,在质量上的投入都将带来总成本的减少。

验证流程作为保证产品质量的一个关键过程。该过程本身也有质量上的要求。验证流程中的主体,验证程序,必须满足下列的质量要求:

1.能够自我检查;

在报告的故障中,有一大部分的故障是由验证程序自身导致的。自我检查可以报告此类故障,避免设计二I:程师的无效努力。

2.可以配置:

便于配置的验证程序方便了各种验证历程的实现。

3.相对容易使用;

4.能够保存log文件;

5.可以产生大范围的输入激励;

对于各种输入激励都能够覆盖才能提供验证空间中足够的保证。

6.方便添加驱动和观测:

当设计由轻微的改变是,验证程序可以方便地进行扩展,而不用重新书写。

7.便于产生测试矢量文件

4.3.1何时结束验证工作

验旺工作需要人力和时间。何时结束验证工作对项目的成功有着关键的影响。过早的结束验证工作导致大量缺陷存在设计中。过晚的结束验证工作导致验训:成本的上升,项目结束时问拖延,匕市同期的推迟等等=需要利学的选择56

验证结束的方法。

扯实际工作中,山各个凼数综合考虑,有下列的结束验讧E工作的评估方法:1.40billion随机测试周期没有发现缺|5}j:

2.直接测试结束

3.功能目标达到

4.减少的缺陷率

5.某一同期

由于实际情况的不同,不同的项目可能采用不同或综合的方法确定验证工作的结束。但是,由方法5唯一确定验证工作结束是最不科学的。方法5通常带来巨大的时间压力而导致验证质量下降。这在实际丁作中屡屡出现。4-3.2同级审查

代码会审是由一组人通过阅读、讨论和争议对程序进行静态分析的过程。会审小组由组长,2~3名程序设计和测试人员及程序员组成。会审小组在充分阅读待审程序文本、控制流程图及有关要求、规范等文件基础上,召开代码会审会,程序员逐句讲解程序的逻辑,并展开热烈的讨论甚至争议,以揭示错误的关键所在。实践表明,程序员在讲解过程中能发现许多自己原来没有发现的错误,而讨论和争议则进一步促使了问题的暴露。例如,对某个局部性小问题修改方法的讨论,可能发现与之有牵连的甚至能涉及到模块的功说明、模块间接口和系统总结构的大问题,导致对需求定义的重定义、重设计验证,大大改善了设计的质量【5”。

审查的主要目标是尽可能在早期去处开发过程中的缺陷。在审查会议上要实现以下目的:

1.在准备阶段发现潜在的缺陷,并在审查会议上加以确认:

2.确认发现的缺陷是真『F的缺陷;

3.记录缺陷;

4.向丌发人员提供记录,以供修正;

在审查会议I要将注意力集中在发现缺陷上,避免将时问花在讨论如何解决缺陷的技术细节上。完成审查会议后,必硕确保存审查中发现的所有缺陷都已经披改正。改矿

的址录将保存在审查记录中。

在进行审查时要注意以下事项:

1.评审人员必须理解作者的敏感性:

审查的目的是发现设计中可能出现的每一个缺陷,同时作者刈提交审查的设计有一种自豪感。由于人性的自我保护倾向会导致相互交流的障碍。

2.审查要保持客观性;

主管个人不应该参与审查的过程中,也不应该试图获得某个人的审查结果。审查对设计的质量负责,不应该由于其他原因影响审查的客观性。3.审查人员应该不要超过5个人;

4.数据收集要一致;

收集的数据可以形成历史数据库。一致的数据便于记录与比较。

审查不是万能的,不能代替测试。但是审查可以显著提高质量和生产率,成效很大。在很多问题的发现上,审查不仅比测试根有效,而且可以在纠正成本较小时及早发现问题【8,9,531。

4.3.3缺陷管理与预防

缺陷预防的基本目标是在错误被标识和修改后不会再次发生。通过实际的统计数据的分析可以发现类似的错误会一次又一次地发生。不同的设计工程师会犯类似的错误,就是同一个工程师也会犯下过去出现的错误。针对错误进行修改不会带来效率的提高。通过过程的改进,减少过程的质量波动,追溯缺陷的源头,人人参与的缺陷预防措施可以起到防范于未然∞]。

缺陷预防有下列原则:

1.设计工程师必须对自己的错误做出评价:

2.及时进行反馈;

3.不存在灵丹妙药,重视小改进:

4.过程的改进需要时间;

缺陷预防的实施步骤如下:1.缺陷报告包括用柬将缺陷分类并确定原因的fh-启、:

浙江J、学顺l学位论艾

2.原因分析确定发生最普遍的缺陷的原因;

3.指定{i-动计划设计出预防最普遍的问题的方法

4.行动的实施全员参与;

5.跟踪状况收集质量状况数据

6.重新丌始

缺陷预防必须在标识缺陷的同时收集大量的信息。这些信息需要使用一个数据库来管理。每个提交的问题都会记录问题的简要和详细描述,提交人,时fNJ,所属部门,严重级别,影响程度以及该问题应当由哪个部门负责解决的信息。使用基于web的数掘库访问技术可以为所有人提供一个友好便利的访问平台。

问题在提交时会对问题进行分类以便处理。可以安装下列的方案进行问题分类:

1.技术性的问题的可定义性,解决问题的可行性,解决过程和工具的可

用性;

2.组织性的工作量的分配,信息的可用性,沟通及资源;

3.历史性的项目的历史,设计的历史,特殊原因以及外部影响:

4.与开发组有关的组成员协作的意愿,项目组内的角色分工:

5.个人的经验,才能,工程师个人素质;

问题提交后,应该尽早地分析原因。确定是什么导致了目前已发现的缺陷?主要的原因种类是什么?为了防止这些错误以后发生,需要采取那些措施?应该怎样安排这些行动的优先级?分析出原因后要形成分析报告。分析报告将加入数据库,并保证所有人都可以访问。在分析报告中提出的改进意见要整合到项目的设计流程中去,在下。个循环中实现质量的有效提高。59

第5章视频后处理项目的实践

本章改进在i占片实现中的验证流程,分析了层次式的验证方法,并应用于数字视频后处理项目的芯片实现过程巾,得到较好的验证效果。本章还详细地讨论了FPGA在芯片验证和调试中的作用。

§5。1视频后处理项目介绍

数字电视接收机中,主要包括信道解调、信源解码、视频后处理三个核心芯片.其中信道解调芯片的开发有待于国家标准的确定;信源解码国际上统一采用MPEG--2标准;数字视频后处理芯片则由于数字电视出现后,各种新业务的不断加入以及各类新颖显示终端的出现,目前尚无定型产品,因而是当前最有市场开发价值的数字电视核心:芭:片之--[311。

数字视频后处理芯片可以把众多格式的视频信号通过数字信号处理的方法转换成统一格式的输出信号,在数字域实现多种业务信号到显像管之间的无缝连接。不论输入的是何种视频信号,通过该芯片处理后的视频信号的格式是统一的,显像管所工作的扫描频率是单一的,这将大大降低对显像管及周边电路的性能要求,降低设计成本,简化生产测试。该芯片除了为显像管提供信号转换外,还可以很方便地实现精确的伽玛校正和枕形失真修正,其准确度是采用模拟方法所无法达到的。对于一些特殊效果,如画中画,淡入淡出,轮廓增强,无闪烁处理等都可以在该芯片内实现,不但可以增强数字电视接收机的功能,还可以应用到演播室设备。

预处理部分完成对高清晰度电视及各类不同输入视频信号的接收,包括MPEG.11支持的18种信号格式,中国制式的25p/50i,以及模拟制式的全电视信号等,其中对模拟电视信号需茸先完成A/D变换,设计重点集中在彩色解码电路模块及其消除模拟电路与数字电路混合设计所出现的干扰影响卜。图像处理部分完成视频扫描格式转换及数字信号处理工作,设计重点集中在运动补偿的算法与电路实现上。后处理部分完成选定格式视频信号的输出,包括高清晰度、},J;准清晰度及模拟电视i类典型格式。芯片还包含了内置OSD部分,采H{0l8urnCMOS1艺进行哎计。图34给m了视频后处理芯片的内部结构框图。6n

浙江人学坝I.学位论迎

数卓'YUVIRGB

(申』牛抒)

垒自提信号

VGA店VGAⅨGAS.耻o

垒电砚信号

S—V诅eo

VGA临vGAⅨGA

越丰j『UVIRGB

(申,牛行)(T兀1伊DP毋MD等)

图表34数宇视频后处理芯片内部结构框图

§5.2验证流程

在数字视频后处理芯片项目中,设计的质量通过流程的合理化来保证。在模块规格书完成后,设计组与验证组同时开始基于模块规格书的工作。61

浙iIA学坝卜学位_【=}:文

+、r+

p幢la吼n;【】l

I

lR亿I:j。lcodei{…^{I…81

厂|羔nv三。II1掣III汹‘蒜。h|r一一。一。LL——L_lIIl÷

{;vncheckHVerilog

testbench

f-

Log

CoverageH一,‰tesetbenchlL—lI『l提交叫tl;Report

追踪数据库

V。/可再%丽\?—\逝ll1,,—]【

7满足\—外———一\coverag/卜—乓;虿一、。

J、\!箜!÷!!堂,,7。

tI提萎。盯【I

图表35验证流程【l提交盖报告I卜一一—刊lj修改dut

验证组首先开始进行测试计划的制定工作。为了保证测试计划的质量和有效性,项目在实践中实行测试计划的同级评审制度。

在验证工程师完成测试计划后,由模块规格书作者,模块代码作者,验证工程师共同进行同级评审。对于任何有疑义的地方都必须进行细致的讨论和确定。只有通过同级评审的测试计划才可以进行验证代码的编写。同级评审制度对测试计划进行把关。同时经过讨论,对于模块规格书的要求都进行了较细致的界定,减少不同人员对模块规格书的语言理解的歧义。同时避免了匆忙编写验证代码带来的返工。

验证组在考察了各种验证语言后选择了Synopsys公司的验证浯占VERA作为验证的编程语言,选择VCS进行硬件模拟软件。

在模块级验证阶段,验证组采用黑盒子验证策略。根据流程,验证组在拿到模块的规格书后丌始进行模块的验证计划书的建立工作。然后按照验证计划

{S的要求进行模块的验证环境的建立和比较模型的建立工作。在进行模块验证之前,验证组对建立的验证环境和比较模型进行质量检查。当模块的硬件描述代码完成时,验证组丌始进行全面地验证工作。在这个期问如果有异常出现将会进行记录,并同设计工程师一同进行进一步地调试。

根据统计发现,建立验证环境的时间化得少,急于进行验证代码的模拟工作反倒是会阻碍验证的及时完成。由表1验证时间分配可以看出在验证的前期进行完备的工作可以减少总的工作时间。由于验证环境建立的质量对验证的进程有着重要的影响。为此规定在完成验证环境必须内建自我检查的功能,并调试通过。

表格1验证时间分配

时间时fnJ

理解DUV规格书,建立验证10lO

策略

建立充分的testplanlOlO

建立验证环境1035

建立和调试案例6010

回归测试lO10

总计10075

数字视频后处理芯片的验证过程采用OVA语言作为时序验证语言。OVA是Synopsys公司推出的时序验证语言。通过OVA编程,着重进行模块接口的检查。使用OVA可以方便地对接口协议进行跟踪,确保接口不会出错。

§5.3模块级的验证

模块的设计是设计的根本,模块级的验证更是验证工作的起点和重点。模块级验证有以下的特点:

1.模块缎验证在项日的早期丌始进行,在此时发现的问题可以很快很便

利地进行修改,对项目地改动和影响最小;

2.模块需要验iEfj',J特性要求明确,可以全而验证:63

浙}【人学1I!(!l学位沧史

3.模型模块的代码很难在系统中被执行到,在模块级可以有针对性地进

行验证:

4.模块代码少,执行速度快;

在验证时使用层次式的验证方法。通过层次的分离,验证工程师可以提供清晰的验证结构,实现一次修改,全部实现的便利,对与信号的底层甚至可以使用BFM模型来代替实际的实现以提升抽象性。验证代码在设计验证框架时t验证代码分成以下的4层。

1.信号层

2.命令层

3.事务层

4.应用层

5.3.1信号层

信号层是验证结构同模块代码间的直接的物理的连接。

信号层包括以下特性:

1.signalnameabstraction,使得高层次的代码书写与RTL模块的代码名

字脱离直接的对应关系,便于重用。

2.co彻ectivitv。提供端口的分类与封装,提供动态连接的特性,便于

重用。

3.monitor。监控信号的合法性,以及错误

vera的验证代码包括以下内容:

1.interfacefiles:.ifivrh

2.virtualportsandbindconstructs

使用动态端口绑定可以提供更加便利地重用。

5.3.2命令层

命令层提供BFM模型的支持,封装了协议与数据,提供监视与错误检测功能。命令层通过BFM模型提供驱动硬件的服务,判装了对硬件的直接访问。用

/tJiiY.人学倾I’学位论史

_rLl可以脱离对硬件的联系。通过对BFM模块的选择,用户可以通过模拟得到寄存器的数据,也可以直接访问寄存器的数据。

5.3.3事务层

事务层是第一个能够提供实际应用要求的服务的层次。这些服务是面向应用的而不是面向测试的。事务层提供自我检查功能,这些功能使得合法的testbench结束就保证结果的正确。

事务层应该提供功能覆盖率的支持。

5.3.4应用层

应用层是最高的一层。通过选择不同的参数,该层提供不同的应用场景。定义不同的事务流。

应用层提供不同进程的同步。通过使用mailbox,semaphore,region等进程通讯结构,VERA提供了对进程间同步很好的支持,帮助建立复杂的应用场景。应用层还包括对事务层的流量管理等。

在验证时应用BFM模型可以大大提高模拟的速度。BFM模型是对物理底层的抽象。进行模块验证时需要对相邻模块的使用,但是该模块还没有完成HDL的描述。此时使用BFM模型可以代替HDL设计进行验证。即使完成了HDL设计,也可以使用BFM模型柬减少软件模拟时间,提高模拟速度‘17J81。

§5.4系统级的验证

系统级的验证是设计的最终保障。在完成系统的功能验证之后,系统级的验证主要集中在系统能否正常工作上,对输入输出等与芯片设计规格书要求的一致性上和对实际工作环境的模拟上。

系统正常工作是系统级验证的最低要求。通过模块级验证的设计并不能保证系统能够正常工作。由于模块阳J的通讯协议的错误理解,对系统要求的误解都有可能导致设计在实际工作环境F失败。

系统级验证主要进行下列的检查:1.检查芯片是否符合觇格书要求;

出于设计时的疏忽,可能存在芯片遗漏规格书的要求。通过遍历所有的规格书要求以确保芯片满足要求。

2.检查芯片接口是否符合协议:

对于SDRAM接口协议等是验证的重点。

3.检查在边界输入下芯片是否T作『F常;

4.检查在异常输入下的芯片工作情况;

避免在异常输入下芯片能够在输入恢复后芯片能够正常工作。

§5.5

5.5.1FPGA原型验证FPGA验证技术的利弊

数字视频后处理芯片项目通过FPGA进行物理验证。在芯片验证中,输入,输出模块是最难验证的,因为输入输出接口有不少物理问题很难用软件进行模拟。通过FPGA进行物理验证可以提高该部分的可靠性。电视信号的输入,画质增强模块和SDRAM控制模块都进行了FPGA验证。

片外的高容量SDRAM为系统提高了有效的存储空间,但是SDRAM的控制时序复杂。测试板上的FPGA和SDRAM芯片实现对SDRAM控制模块的充分的验证。为了验证的便利性,修改了SDRAM控制模块中的地址映射部分。

画质增强模块实现对电视图像的增强。通过FPGA的仿真,实现了实时地对增强后地图像进行评测。如果使用软件模拟,需要难以承受的时间去得到处理后的图像,以至于该方法没有实际意义。

FPGA验证有其有缺点,与软件模拟验证互为补充。FPGA可以实现高速仿真。FPGA的仿真速度通常比软件模拟高3个数量级。对于数字视频后处理芯片项目来说,使用软件模拟无法实现实时的数据处理,只能通过文件进行缓冲。使用FPGA就可以实现实时地对图像的效果进行有效的评估。

高速是FPGA最突出的优点。但是FPGA验证也有很大的缺点。

一是使用FPGA需要建立一块测试板。测试板的设计与调试需要时问与人jj。

.是FPGA与ASIC存在着‘些不同。面向ASIC的设计很可能尢法满足66

FPGA的要求,需要进行修改然后才能使用。现在的技术还无法提供高速高容量的FPGA。数字视频后处理芯片的系统丰频工作在108M。两级寄存器问进行的人量的运算可以在ASIC中实现但是在FPGAL}J只能增加寄存器,使用流水结构。这样就需要对部分设计进行面向FPGA的修改。这种修改需要大量的工程师的努力,而且降低了验证的效果。

三是对FPGA内部的信号缺乏访问,无法进行深入地追踪调试。对于信号也无法保存,通过逻辑分析仪只能采集到有限的信号。

FPGA验证无法代替软件验证,但是它是软件验证的很好的补充。数字视频后处理芯片项目积极地使用FPGA验证柬加速验证流程。

5.5.2ASIC向FPGA移植技术

ASIC与FPGA的实现结构上互不相同。ASIC通常使用综合工具将RTL级代码映射到对应芯片制造厂提供的标准单元去。这些标准单元:包括完成逻辑功能的与非门,非门,或非门等基本门单元,完成存储功能的各类触发器和锁存器,以及其他宏单元如RAM等。FPGA器件为了实现可编程功能,通常使用查找表结构实现电路的逻辑功能。面向ASIC的HDL代码必须进行以下的修改才能移植到FPGA中去。

1.修改存储单元

ASIC实现的存取单元通常使用RAM,但是FPGA中使用特殊宏单元结构。所以在使用FPGA实现大规模存储单元时需要将标准单元的RAM替换为FPGA宏单元。由于m』ERA器件的存储宏单元基于嵌入系统块(EmbedBlock,ESB)实现,不同位宽,时钟的RAM不能使用同一个ESB单元实现,所有最后生成的RAM容量通常会大于所需容量。System

为了减少ESB浪费,RAM的字长和位宽最好是ESB可配置的倍数,RAM容量是ESB可提供容量的倍数。

2.修改时钟

FPGA中已经装备了数量有效的PLL宏单元和全局时钟线。必须将ASlC设计中的PLL单元替换成FPGA中的PLL宏单元。

3.增加计算部分的流水

FPGA中的器件延时比ASIC标准单元要大得多。对于父键路径很ⅡT能67

ASIC可以实现,而FPGA无法满足时序要求。这时就需要增加流7Jean使用乒乓模式来咀及并行模式柬提高系统速度。

削表36增加流水

4.减少数据总线延时

由于FPGA硬件结构特点,FPGA内部有很大的走线延时。FPGA器件中的特殊单元如ESB单元,Io单元等只在器件内特殊位置。使用这些单元必然会带来较长的走线延时。通过增加缓冲寄存器可以保证系统的时序满足要求。

5.扇出增强

FPGA中的高驱动单元数量有限,通常保留给时钟与重要的全局信号线。其他基本单元的驱动能力都是一致的。当一个信号的扇出多,负载大时,信号线的延时会增大许多,并最终导致时序不满足要求。对于这种情况必须进行扇出增强。通常有两种解决办法:一是使用驱动缓冲,增加信号驱动能力;另一个是使用驱动复制,减少信号负载;

蚓表37驱动增强利复制

6.时序调整在修改DRAM,增加计算部分的流水,增加缓冲寄仔器都会改变系统n0

时钟1,拍数。增加时钟节拍可能影响系统功能,时此需要进行仔细的评估,做到对系统的改动最小,以免影响到验证的效果。

5.5.3FPGA验证板介绍

视频后处理项目使用一块带有两块高性能FPGA的PCB板作为系统的验证板。该板的核心是一块m』ERAAPEX系列的EPOK600EBc652—2x的PFGA和一块ALTERAAPEX系列EP20K1500E一1X的FPGA。输入部分使用一块3230解码芯片和AD9051模数转换芯片实现多种输入的解码。解码后的数据为656格式的电视信号。输出部分使用多块DA芯片实现VGA等电视信号。每一块FPGA配备2块16位的SDRAM用于图像数据的保存。

输入格式能够接受s端子,Av信号,和CVBS全电视信号。AD905l是一块10比特的模数转换芯片,通过它对CVBS全电视信号进行采样后提供给后端处理。3230解码芯片可以完成s端子输入信号,RGB信号和AV信号等的多种格式转换为ccir656标准格式的电视信号以供后端处理。输出部分实现SVM信号,3路YpbPr和VGA格式。

3230卜—_.■

FPGA_.卜FPGA

l|AD卜+

图表38FPGA验证板

EPOK600EBC652PFGA的最大门数为1,772,000门,典型门数为1,000,000有38,400个LE,160个ESBs,327,680个最大RAM比特,最多2,560个宏单元,708个用户可用管脚。

EP20K1500EPFGA的最大门数为2,392,000门,典型门数为1,500,000

有51,840个LE,216个ESBs,442,368个最大RAM比特,最多3,456个宏单元,808个用户可用管脚

表格2FPGA性能比较

【

l最大f-j数EPOK6001.772,000EP20K15002,392.00069

典型门数

LEl,000,00038,400

160

327.6801,500,00051,840216ESBs最多RAM比特

最多宏单元442,3683,456

8082,560708用户可用管脚

视频后处理项目芯片的规模大约为70万门,其中RAM容量为27K比特自由逻辑大约30万门。因此可以采用以上的验证板进行完全的验证。

5.5.4可配置的验证平台

为了完成高效的算法验证,视频后处理项目搭建了一个可配置式的验证平台。该平台完成输入电视信号的格式转换,SDRAM数据存储时序控制和电视信号输出。可配置验证平台是可执行的,它可以完成输入信号的存取,进行格式转换后输出。当算法模块完成后,将算法模块添加到验证平台上去,就可以通过验证平台实时地对电视图形处理结果进行评估。

l.………-算法实现l

幽表39验证平台

由于有了以上的验证平台的支持,视频后处理项目可以对几种算法进行实时评估。

去隔行可以使用运动估计算法和非运动估计算法,线性和非线性的算法。有基于边缘的去隔行和图形匹配的去隔行等等。算法包括空间去隔行,时问去隔行和空l’HJ一时问去隔行等。如何选择合适的算法是芯片设计的一个重大问题。通过软什的模拟uJ以对各种算法进行列比,但是模拟的速度有限,而且无法在70

浙江:人学坝I。学位论文

电视机卜进行直接比较。通过FPGA的验证平台,任何算法的改变,参数调整都能够实现实时地观察到电视机上的图像输出,进行各种性能比较。

因为验证平台上的FPGA提供了足够的门逻辑,验证瓶颈是芯片实现的高效率的代码无法在FPGA上实现108M工作时钟的约束下的综合。为了解决FPGA速度限制,不得不对待验证的代码进行局部修改,以满足工作时序。如SDRAM控制器中的地址译码电路通过多级选择器实现,无法满足FPGA工作要求。在验证平台上使用时,对该部分逻辑进行了修改。

为了达到最大程度的验证效果,如此的改动要尽量少,而且必须通过一致性验证。

§5.6FPGA与调试

当芯片制造完成后进行的调试和测试是验证工作的延伸。FPGA在验证时发挥了强大的作用。根据验证时的FPGA技术的积累,数字视频后处理项目使用FPGA加强了芯片调试和测试工作。

5.6.1调试板

为了测试工作的方便,在设计芯片测试电路板时加入一块ALTERAcycloneEPICl2Q240C8系列。

蚓表40FPGA调试扳一j系统进入直通模式时,FPGA将解码芯片提供的数掘提交给视频后处理芯

』h处理后的结果也通过FPGA提交给电视机显示。当系统进行调试时,FPGA可以根据需要对处理芯片的输入输出数据进行处理和修『F。

5.6.2DFT结构的利用

在芯片设计演化过程中,可测性设计(DesignForTest,DFT)已经成为标准流程。其中最具代表性的时在综合时插入扫描链的基于扫描的可测性设计。在SoC芯片中,通过端口对内部的IP或底层模块的访问技术越来越受限制。当芯片制造出来后必须进行功能测试,由于芯片内部如同一个不可访问的黑盒子,无法高效地进行芯片的调试工作。为了方便调试要求在设计中加入可验证性设计,比如利用验证总线对数据进行访问等。但是这些验证用途的模块在芯片正常工作时是资源的闲置。视频后处理项目在实践中提出一种利用扫描链资源进行芯片验证的方法。

视频后处理项目的某一个版本的芯片在调试时发现图像显示异常。通过对设计版本的检查并没有发现问题。RTL级与网表级的代码模拟结果也『F常。由于在设计中没有进行可验证性设计,在调试时无法对内部模块进行分析,通过端口的数据分析也无进展。故障在哪里?故障如何产生?以后如何避免?这些问题直接影响下一版本设计的进度。使用FPGA,利用芯片内部的DFT结构进行验证工作最终找到缺陷所在。

这个问题是对芯片进行验证的工作。故障有以下的具体表现形式:

1.色度信号正常,亮度信号异常:

2.每8个象素点出现一次覆盖现象,第5个象索复制到第1个象素;

在故障观察阶段,使用了标准电视信号发生器作为芯片输入,在CRT显示器上观察输出。由于标注电视信号发生器的源的数量有限,不能针对数字视频后处理的故障进行调整,因此使用一块FPGA单独产生调试用的电视信号源。

在分析图像时,开始错误地估计图像故障为象素交换,即第5象素与第l象素交换。但是标准电视信号发生器的源无法确定这一猜测。

为了验证初步的猜想,根掘故障表现,制作了如下的源。经过数字视频后处理芯片处理插值后,理想输出图像为图41,实际输出分别为图42。

盖的关系,而不是

预处理的纠正办法

薰~筘l羹一囊薰~辫l图表42实际输出

在分析原因时从两个方面入手:一是对流片的verilog文件版本的核查和仿真,二是对数字视频后处理芯片与SDRAM接口之间的时序进行分析。

对verilog文件进行了手工核查,同时进行系统仿真。仿真结果表明没有异常。对SDRAM的接口也进行了分析。使用逻辑分析仪和示波器对SDRAM接El的数据和时序进行分析。通过对实际时序的提取延时参数施加在verilog仿真文件上进行故障模拟仿真。仿真的故障结果与实际故障不符合。同时进行对SDRAM接口的静态时序分析。仿真结果的进一步分析表明SDRAM接口的时序错误导致的故障应该是4个象素的错误,而不是实际上的一个象素点的错误。在进行核查时,着重考虑了输入,输出部分的串并转换的代码。因为数据在外部是8bit的组织形式,在数字视频后处理芯片内是32bit的组织形式。实际情况是32bit中的8bit出错了。但是检查和仿真都没有发现问题。

在分析的同时进行了RAM的BIST。BIST结果表明数字视频后处理芯片内的RAM有错。盯j二BIST只能输出lbit的结果,无法判断是片内4块RAM的

具体情况。根据BIST结果,判断数字视频后处理芯片内错误的可能性最大。由于数字视频后处理芯片没有测试总线,为了对故障点进行定位,利用计内的扫描链结构进行验证。

山于数字视频后处理芯片内没有测试总线,只有通过扫描链对芯片内的寄存器进行访问。为了定位方便,设计了一个特殊的数据源,同时对数据通路进行分析,确定了需要访问的寄存器与寄存器所在的扫描链。

控制器参考自动测试设备的控制时序设计。同时使用12C总线实现PC机与FPGA的数据交互。在进一步分析的结果表明故障点可能位于RAM的低位地址线。通过版图提取工具提出物理版图的信息也最终确认了该故障点。

该故障点是在芯片完成制造后检查出来的,是验证流程中的一个逃逸缺陷。如果在验证流程中发现这个缺陷,那么这个缺陷的修补代价将远远少于在芯片制造完成之后进行修补的代价。这正是验证的意义所在。74

第6章总结

不断缩小的晶体管特征尺寸给集成电路带来了更高的集成度、更快的速度以及更低的成本,同时也带来了新11,3-}4Ii战…卷片设计能力的增长速度远远少于芯片制造能力的增长速度。如何提升设计能力的1i足,弥补其与芯片制造能力间的差距是世人关注的焦点。同时市场竞争进一步加剧,为缩短投入市场的周期,降低成本,需要及时找出并修复尽可能多的缺陷。传统基于模拟的验证技术面对新形势回天无力。

在这个关键的时刻,如何科学的解决验证危机已经是成功实现芯片设计,出了解决验证危机的两条思路:一是在芯片设计的过程中采用高级的验证技术。二是在芯片设计的过程中采用科学的验证管理。

针对传统验证技术在超深亚微米阶段出现的瓶颈,本文回顾了传统基于模相结合的验证方法,解决了传统门级模拟急速上升的验证时间、日渐庞大的模分析了形式验证的验证过程。

高级验证语言是芯片设计复杂度达到一定程度后的必然产物。验证工作已面向对象的层次式的实现方法,和验证重用的思想。高级验证语言帮助视频后处理项目更加专注于验证思想而不是验证细节的实现。面向对象的验证方法和验证重用带来效率的极大提高。

科学管理在芯片实现过程中扮演越来越重要的角色。芯片设计的过程是科学,但是它也是一门艺术。由于人在芯片设计过程中扮演的关键作用,设计过程中必然导入与人性相关的因素。视频后处理项目在验证独立性原则的指导下,为了避免人性中强烈的自我保护意识对验证工作的下扰,对验证组织和流程进行创新,科学有效地建立验证组织,实施同级审查和评审等流程,有力地弥补75提高产品质量的有力保证。本文在数字视频后处理芯片项目的实践中研究并提拟的验证技术,同时深入研究了实现验证方面的最新发展~静态验证技术和高级验证语言的应用。数字视频后处理项目全面地采用静态验证技术与模拟技术拟向量以及验证的不完备性等问题。本文还进一步从模拟工艺波动,真实性分析及信号完整性的分析等几个方面探讨如何做到准确的静态时序验证,还详细经发展成为独立的-r]技术,需要更加专业的工具。本文讨论了高级验证语言,

浙}E夫学蛾l掌能逊文

,个人的能力陷阱和茸区。通过科学韵管理理念和手段弥补技术与人力资源的不足,将技术与人完美地结合在一起,创造出更高的生产效率。

芯冀一验涯危巍已经列来,只有实瑗先邋鑫冬验证技术与季喜学的蛰理蠢‘能度过危枫。本文以超深甄徽涨ASIC实现为目的,在分析超深亚微米技术给ASIC实现带来的验证挑战的基础上,对现代ASIC验证流程进行了较为深入的研究,从验证技术与验证管理方面进行刨新,并将之运用到ASIC实践中去。希望本文对戮舔主流半导体工艺下的集成电路验证方法的研究能够为发展我国集成电路鬻始器一稔终薄之力。76

浙江J、学坝卜学位沦艾

一———————————————————————————————————————————————————————————————一——————————————————————————————————————————一

参考文献

[1]1NigerlHorspool,PeterGonnan,ASIC完备指南,清华大学出版社,2002,1l

【2]2黄勇刚,中小型软件丌发企业的嵌入式系统软件测试,电子工程专辑,2003,

ll,16

ProcessAutomation[3]VERISITY,Vel‘ificationSolutions加rSuccess,Next

GenerationVerificationseminars,2003

[4]DavidDempster,MichaelStuart,VerificationMethodol093,Manual,Teamwork

International,Jun2002

[5]JanickBergeron,WritingTestbenchsFunctionalVes";ficationofHDLModel,

KluwerAcademicPublishers,2000

[6]Synopsys,Fel-t)qcationwithVCSWorkshop,SynopsysProfessionalServices,2002[7]DaveTaylor,JamesC.Armstrong,Jr,著,冯博琴等译,

1998,3械工业出版社,

4UNIX自学通,机[8】WattsS.Humphrey著,高书敬译,软件过程管理,清华大学出版社,2003,

[9】G.GordonSchulmeyer,JamesI.McManus等著,李怀璋等译,软件质量保证,

机械工业出版社,2003,5

[10]KenAlbin,NutsandBoltsofCoreandSoCVerification,ACMConference’00,

Month1-2,2000

(1i]FusunOzguner,DuaneMarhetka,JoanneDeGroat,TeachingFutureVet妒cation

Engineers:孤eForgotten&如ofLogicDesign,DAC2001,June18—22,2001

【12]AlbertoL.Sangiovanni—Vincentelli—PatrickC.McGeeryAlexanderSaldanhaz,

Vet‘ificationofElectronicSystems,DAC96-06/96

StefanRohringer,Ver/fi。cation[13]GeorgNiedrist,

muhimillion-gateembeddedcoredesign,DAC99andManagementofa

[14]AdrianEvans,AllanSilburt,GaryVrckovnik,ThaneBrown,MarioDufresne,

GeoffreyHall,TungHo,YingLiu,FunctionalVerificationofLargeASICs,DAC98—06/98

【15]MikeG.Bartleyl,DarrenGalpin,TimBlackmore,ACompat。isonofThree

阮。ification

Checking,

BostonTechniques:Directed,Testing,Pseudo—RandomTestingandPropertyInfineonTechnologiesRecipe[16】PeetJames,Afo,+Multi—MillionGateASlCVel.ification.SNUG99

[17]BenCohen,ComponentVet"ification卸,Example,VhdlCohenPublishing,

http://www.vhd|cohen.com/

【18]JanickBergeron,ExploitingthePowe,‘ofVera:Creating№Emf

LevelDataSttluctgvesinClassLibrat’ies,Qualis

口,adBehm,ioralDesignCorporation,February2,2000[19]BradleySmith,BernardL,Delay,HighVet‘ification

DesignModels,2000System-on—ChipDesignConference[20]JanickBergeron,ManagingVHDLModelswithMakefiles,1997Qualis

Corporation

[211PeetJames.ChrisMacionski,Shotg“,7£?AnEi9111一StepApproachtOExpe,’ience

RandomVet。蛳cation,VerisityUsersGroup2001,March6.2001

[22]‘‘印ec—BasedVellification”,http://www

[23]Mark

theDesignvedsity.com/html/technicalpapers.htmlRosstSachidanandanSambandan,UsingStaticFunctionalVelt圻catiollinq(aMemon_,Conn‘ollet4,2000System.on.ChipDesignConference[24]ThomasL.Anderson,Vel-ification."ReuseIt01?LoseIt,DesignCon2002

System-on?-ChipandIPSystemDesignConferenc

[25]ThomasL.Anderson,UsingVCSwithWhite—BoxVel4ificationTechniques,

toSNUGSanJose2000[26]Steve

【27]DaveCox,RaisingFunctionalVel-ificationaHigher‘Level,虹地上纽璺璺丛瞳吐鼬Transactionacc.com/products/tbvtools/access/checkbenchwhitepaper.htmlWhipp,ExperienceswithRTL—SynchronizedReference

Models,DesignCon2003System—on—ChipandASICDesignConference

[28]Synopsys,OpenVerav”Assertions,April2002

[29】CarolFields,FPGA设计再利用策略,《电子设计技术》2001年5月

[30]王巍colinyen,集成电路设计的新纪元,丛p:型竖型w.!鲥t!.!Q幽i£缝n941a!!坚

hejidexinjiyuan.htm

[31]ThomasL.Anderson,UsingVCSwithWhite-BoxVerificationTechniques,

SanJose2000SNUGSanJose2000[32]GreggD.Lahti,TestBenches."TheDark&如矽IPReuse,SNUG

【33]Chris

Jose2003Spear,JoePick,OPENVERACODINGSTYLEGUIDELINES,SNUGSan

and[34]Hsin—Chu,ChallengesOpportunities砌Giga—Scale

Jointh?tegration,orWorkshop,Aug.24-26,1999

[35】AkihiroHigashi,KazuhideTamaki,TakayukiSasaki,Vel‘ificationMethodology

fo,‘aComplexSystem—OIl—a—Chip,FUJITSUSci.Tech.J.,36,1,PP.24-30System—On-A—Ch驷,NSF/NSC

[36]王迎春,吉利久,SOC设计过程的质量保证,电子产品世界,2002,l,p26

—29

[37】麦凯,模拟/混合电路SOC的设计难题,电子产品世界,2002,4,p65--67[38]GabeMoretti,系统级设计值得密切注意,EDNCHINA电子设计技术,2002,

6,p68—76

[391DinoCaporossi,SoC设计带来验证挑战,http://www.eetchina.com/ART一

88QQ22Q815:丛!醚,2002年09月15日

[40】SteveCox,RaisingFunctionalVet‘ificationtoaHigherLevel,h女p;』』型燮型dg煎gⅡ

acc.com/products/tbvtools/access/checkbenchwhitepaper.html,1998,11

【41]ScottCiener,在高风险ASIC丌发时,应选择仿真还是原型验证方法?2001,4[42]GreggD.Lahtit

Boston2000SteveJ.Brown,Tcl:The

Privett,AGood,确eBad,and朋P坛纱,SNUG[43]RodneyPesavento,Michael

SNUG‘99BFMSimulationStl‘ategyforVerilog,

in[44]CliffordE.Cummings,NonblockingAssigllnlents

勋,lesThatKill/,SNUGSanJose2000

[45】CliveMaxfield,Walking

【46]BruceGreene,OpentheassertionmazetVerilog¥,nthesis,Codinghttp://www.eedesign.com/stoly/OEG200208l5S0035.htlnl,August15,2002VeJla20assertionsempoue1.11el‘伊cation,h凹j/—/ww—w.ee

i折TI从学帧I学位论文

design.com/story/OEG20020410S0047.html,Aprill0,2002

『47]BrianMarick著,韩柯等译,软件子系统测试,机械工业出版社,2003,9f48]StephenHKan著,王振字等泽,软件质量工程的度量与模型,机械工业出

版社,2003,10

[49]KarlE.Wiegers著,沈备军等译,软件同级评审,机械工业出版社,2003,

6

[50】于兆明编著,数字电视和高清晰度电视,人民邮电出版社,1997,5『5l1ThomasL.Anderson,Vel‘ification:ReuseItOl"LoseIt,System—013一ChipandIP

SystemDesignConference,DesignCon2002

f52]StevenR.Rakitin著,软件验证与确认的最佳管理方法,电子工业出版社,

2003,3

f531CindaFlynn,建立仿真环境对芯片进行全面验证,地://www.eetchina.com/

—arti—clecontent.php37articLeid=—88002—40976,2002年06月叭R79

致谢

回顾攻读硕I:学位的三年,首先要特别感谢的是我的导Ni≯Li明教授。正是褒激老颡戆;|导下,我彳‘有懿会在芯冀设诗镁域孛述嚣探索,=}ili仅提裹了辩磁能力,而且找到了我所鬻爱的可以终生追求∞事业。我根敬佩张老师严谨的治学作风、求实的科学态度和高昂的工作热情,更让我敬佩的是他博大的人格魅力。这些都将使我受益终生。张老师不仅在学习上对我谆谆教导,而且在生活中绘了我无隈的关怀秘激暖。在觉,我要衷心黪澄…声:爨i蘩您,张老蜂l非常感谢胡海波师兄对我的指导,他以实际行动向我展示了在科研工作中应抱有的态度,在他的囊接指导下我才得以迅速的成长。

黪潦在生活黟学习中餐绘予我帮鼙豹畿雾雾秘霜学翻,毯们楚时丰,遥岩,张雪峰,韩晓霞,谢磊,郑伟,陈涛,吴明远,刘东栋,周凉芳,朱欣荣,占进,黄智杰,王文华,缪纲,孙一飞,李铭,徐红,孔晓斌等。

感滏=|竞itll雪芯摹萼按骞隈公霉款领导秘瓣攀粥杰实习赣淘绘予浚鲍关心帮嫠助。

感谢我的父母和繁函江小姐给我信心和勇气面对任何困难和挑战。

粱骏2004年1月于求是西

80

芯片设计的验证技术和验证流程研究

作者:

学位授予单位:

被引用次数:梁骏浙江大学4次

引证文献(4条)

1.王沛.任浩琪.钟文枫 VStation硬件辅助验证平台在高性能CPU功能验证中的应用[期刊论文]-中国集成电路 2007(11)

2.丁谢 THUASDSP2004处理器功能验证的设计及实现[学位论文]硕士 2006

3.沈浩 基于人工智能的芯片自动化验证[学位论文]硕士 2005

4.林敏星 DVB-S接收系统的芯片设计与实现[学位论文]硕士 2005

本文链接:http://d..cn/Thesis_Y581455.aspx

-

设计验证计划实施流程

贵州中电振华精密机械有限公司设计验证计划实施流程流程更新记录贵州中电振华精密机械有限公司1控制目标此流程规范公司开发新产品时的设计…

- 设计和开发验证操作规程

- 13设计验证计划和报告

-

设计验证计划和报告(DVP&R)要求点检表(APQP要求)

设计验证计划和报告DVPampR要求点检表APQP要求定义说明要求目的设计验证计划和报告DVPampR是指一种制订贯穿于产品过程开…

-

设计验证(APQP要求)

设计验证APQP要求定义说明要求目的设计验证是指确保所有的设计输出满足设计输入要求的试验设计验证是产品设计和开发阶段的输出也是过程…

-

质量检验计划

北京航天医院工程卧式脉动真空灭菌器工程质量检验计划编制审核批准北京政平建设工程有限公司年月日目录1编制说明及依据111编制说明11…

- 设计和开发验证操作规程

- 13设计验证计划和报告

-

设计验证计划和报告(DVP&R)要求点检表(APQP要求)

设计验证计划和报告DVPampR要求点检表APQP要求定义说明要求目的设计验证计划和报告DVPampR是指一种制订贯穿于产品过程开…

-

设计验证(APQP要求)

设计验证APQP要求定义说明要求目的设计验证是指确保所有的设计输出满足设计输入要求的试验设计验证是产品设计和开发阶段的输出也是过程…